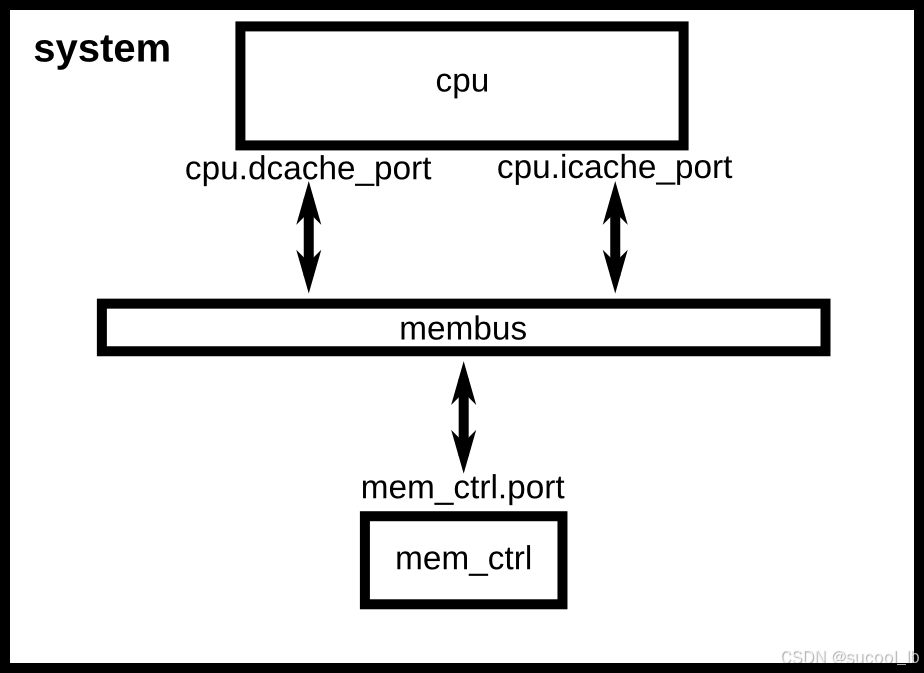

本节目标, 创建一个 简易的 RISCV CPU SoC 系统,系统拓扑如下:

- 单核/无cache

创建配置

mkdir configs/tutorial/part1/

touch configs/tutorial/part1/simple-riscv.py脚本内容如下:

import m5

from m5.objects import *

# 创建系统

system = System()

# 设置 时钟 电压域

system.clk_domain = SrcClockDomain()

system.clk_domain.clock = "1GHz"

system.clk_domain.voltage_domain = VoltageDomain()

system.mem_mode = "timing" # Use timing accesses

system.mem_ranges = [AddrRange("8GiB")] # Create an address range

# riscv

system.cpu = RiscvTimingSimpleCPU()

# membus

system.membus = SystemXBar()

system.cpu.icache_port = system.membus.cpu_

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

680

680

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?