目录

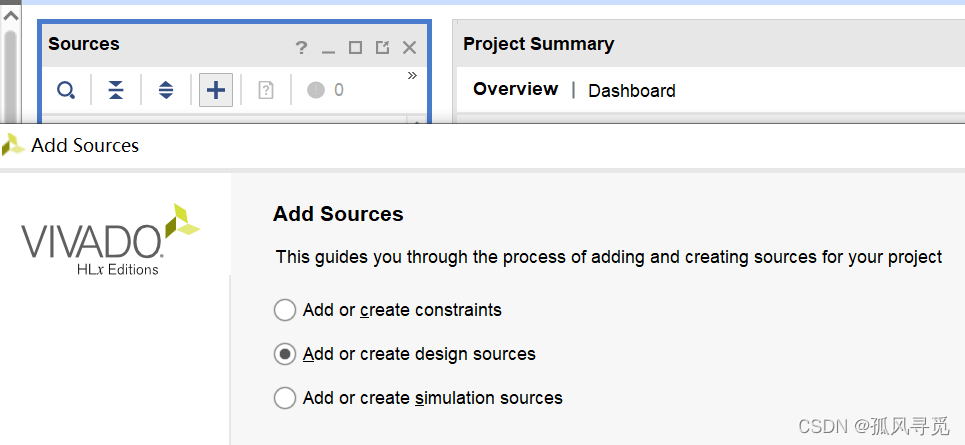

一、添加设计文件

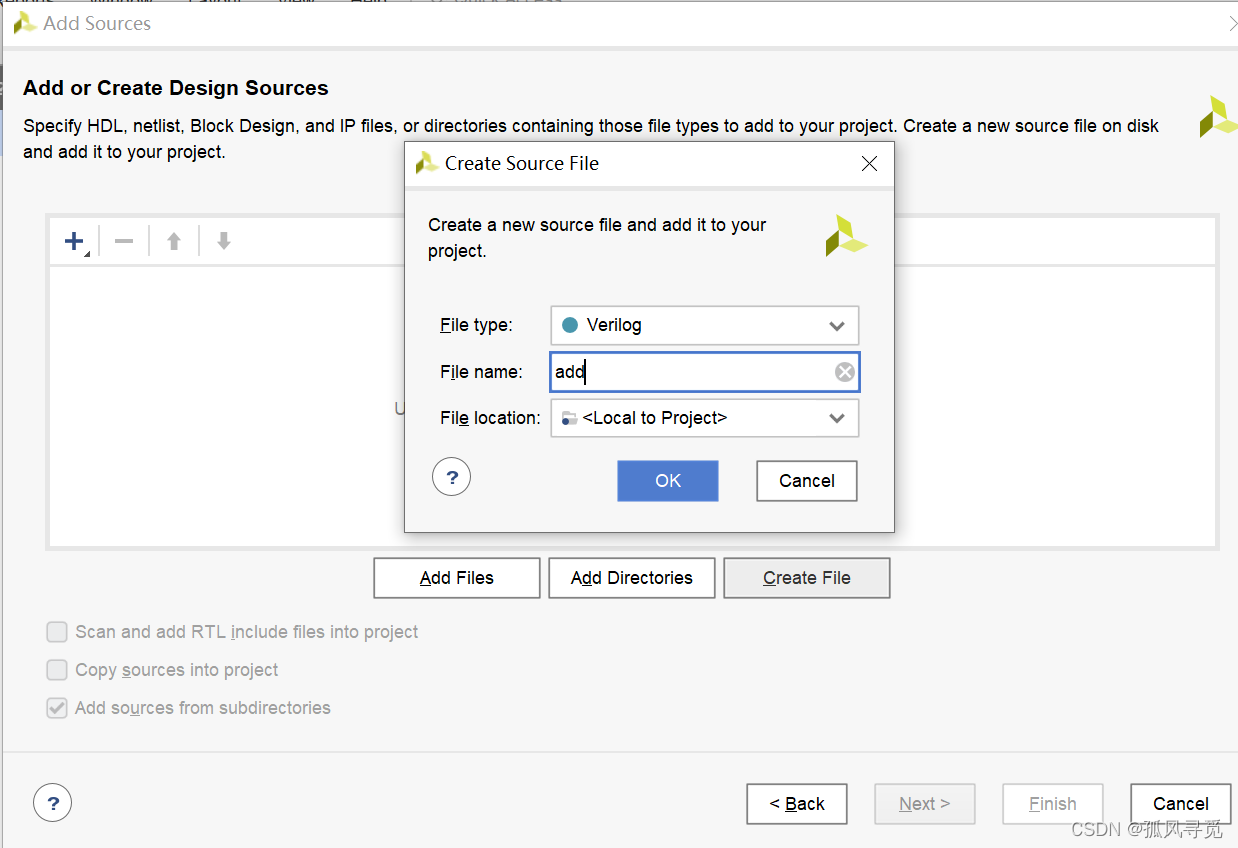

点击“+”号,选择新建设计文件add

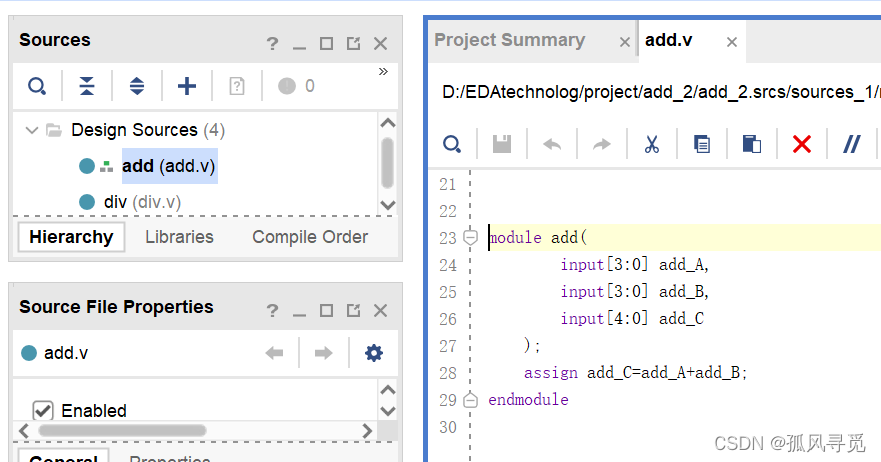

在这可以看到add.v文件,双击打开,输入add运算

add.v程序具体:

`timescale 1ns / 1ps

module add(

input[3:0] add_A,

input[3:0] add_B,

input[4:0] add_C

);

assign add_C=add_A+add_B;

endmodule

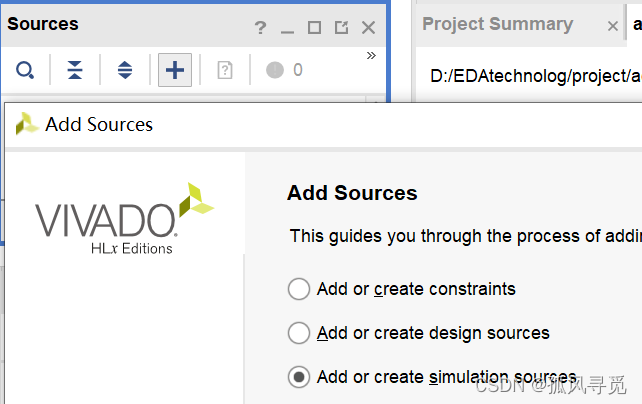

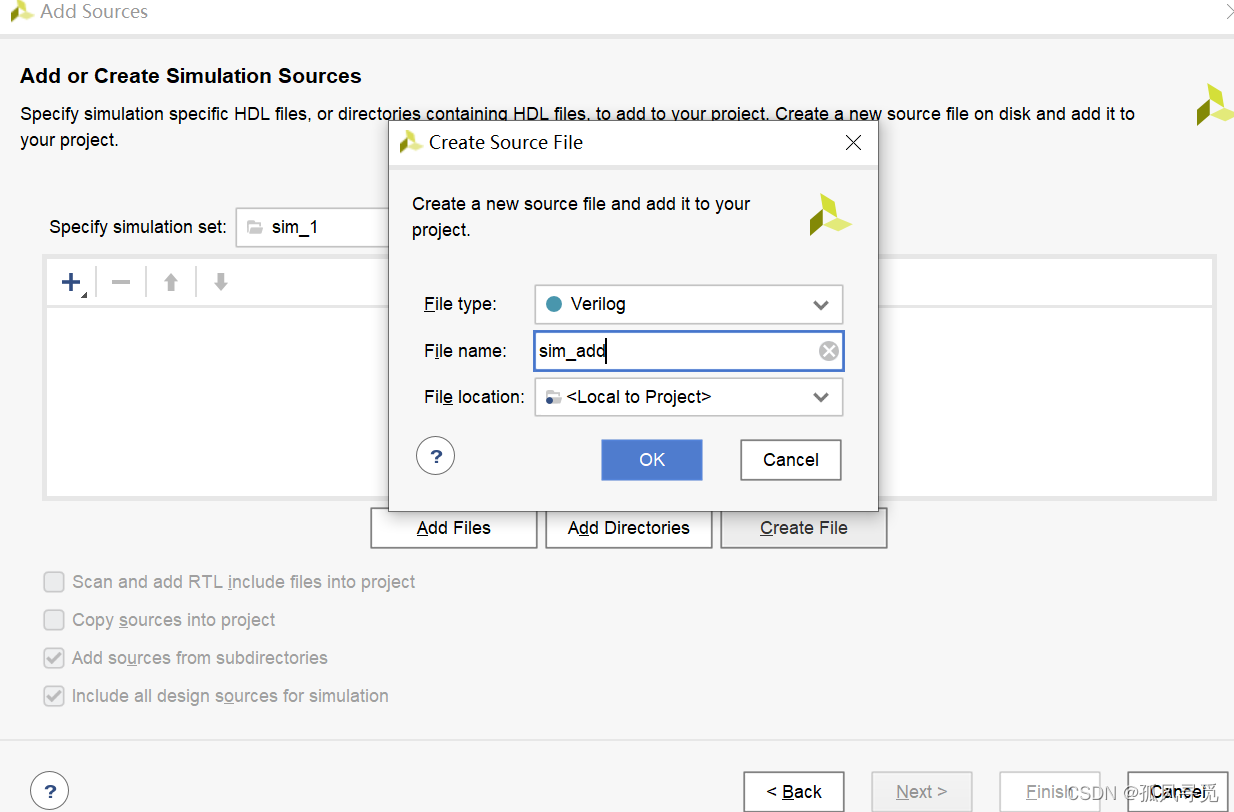

二、添加仿真文件

同样“+”号,选择新建仿真文件,命名为sim_add

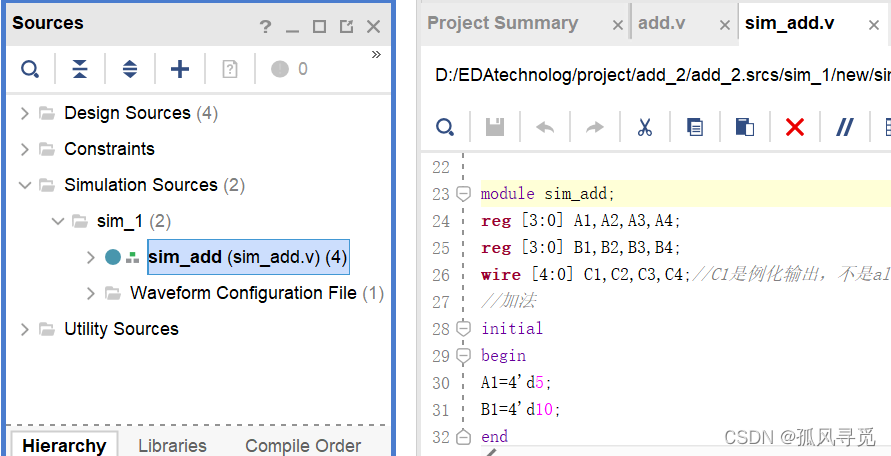

在source—simulation source可以找到sim_add.v,双击打开输入初始化代码和例化。

具体代码:

`timescale 1ns / 1ps

module sim_add;

reg [3:0] A1;

reg [3:0] B1;

wire [4:0] C1;//C1是例化输出,不是always产生,所以定义为wire型

//加法

initial

begin

A1=4'd5;

B1=4'd10;

end

//例化前面是要连接的模块名,后面是例化名

add my_add(

.add_A(A1),

.add_B(B1),

.add_C(C1));

endmodule

注意例化前面是模块名,后面是例化名。对应引脚框外是模块引脚,款内是例化引脚。

三、加减乘除的其他代码

只需要新建设计文件,将加法的代码稍作修改,再到sim_add中添加代码就可以了。

以减法为例:

新建设计文件sub.v,具体代码:

`timescale 1ns / 1ps

module sub(

input[3:0] sub_A,

input[3:0] sub_B,

input[4:0] sub_C

);

assign sub_C=sub_A-sub_B;

endmodule

补充完整的sim_add文件具体代码如下:

`timescale 1ns / 1ps

module sim_add;

reg [3:0] A1,A2;

reg [3:0] B1,B2;

wire [4:0] C1,C2;//C1是例化输出,不是always产生,所以定义为wire型

//加法

initial

begin

A1=4'd5;

B1=4'd10;

end

//例化前面是要连接的模块名,后面是例化名

add my_add(

.add_A(A1),

.add_B(B1),

.add_C(C1));

//减法

initial

begin

A2=4'd10;

B2=4'd5;

end

//例化前面是要连接的模块名,后面是例化名

sub my_sub(

.sub_A(A2),

.sub_B(B2),

.sub_C(C2));

//乘法

initial

begin

A3=4'd2;

B3=4'd3;

end

//例化前面是要连接的模块名,后面是例化名

mul my_mul(

.mul_A(A3),

.mul_B(B3),

.mul_C(C3));

endmodule

完整Vivado工程文件可以参考:Vivado—加减乘除算术运算仿真-C文档类资源-CSDN下载

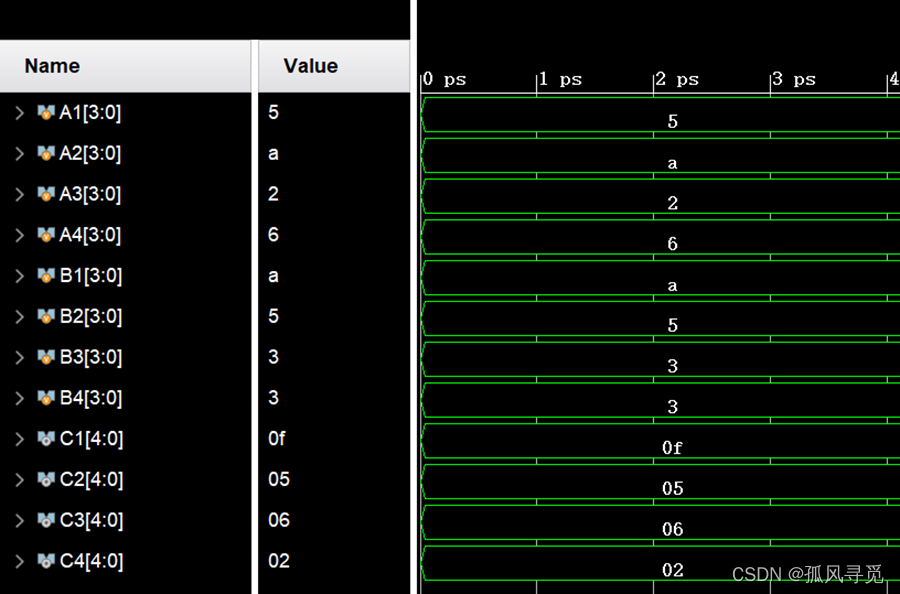

四、仿真+仿真结果

本文介绍了如何在Vivado环境中进行FPGA设计,通过创建设计文件和仿真文件实现加减乘除运算。首先,添加了`add.v`文件实现加法运算,接着创建仿真文件`sim_add.v`并进行初始化设置及模块例化。然后,展示了如何修改加法模块来实现减法,并在`sim_add.v`中添加减法和乘法的例化代码。最后,仿真运行得到预期的运算结果。该教程对于学习FPGA设计和验证具有实践指导意义。

本文介绍了如何在Vivado环境中进行FPGA设计,通过创建设计文件和仿真文件实现加减乘除运算。首先,添加了`add.v`文件实现加法运算,接着创建仿真文件`sim_add.v`并进行初始化设置及模块例化。然后,展示了如何修改加法模块来实现减法,并在`sim_add.v`中添加减法和乘法的例化代码。最后,仿真运行得到预期的运算结果。该教程对于学习FPGA设计和验证具有实践指导意义。

4764

4764

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?