AXI协议总结

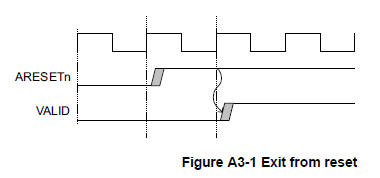

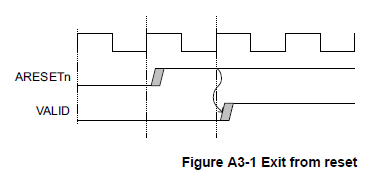

全局信号:ACLK, ARESETN. 其中ARESETN必须同步释放。

基本握手信号:VALID/READY。 发送方(source)将VALID置位表示数据有效,接收方(dest)将READY置位表示数据可以被接收。当VALID/READY都为高时,数据有效。

图A3-2~图A3-4显示了几种常见的时序。

但是并不推荐默认将READY置0,因为会浪费一个CLK。(判断VALID并拉高READY耗费一个CLK,source判断READY为高又要一个CLK, 这种情况如图A3-2,完成一次传输至少要耗费2个clk)

握手信号的独立性:

VALID信号不应依赖于READY信号。

READY信号可以等待VALID信号到来再置1,也可以不等待。后者效率更高。

AXI4的5个通道:写通道有3个,读通道有2个。我认为这5个通道中,除了Write Response通道都是从master的角度去看的。每个通道都遵循上述的VALID/READY握手协议,具体的信号名字有所区分。

Abbr:

AW-Addr Write, AR-Addr Read, W-Write data, B-Response, AR-Addr Read, R-Read data

Channel之间的关系

AXI4 Channel仅有以下简单的约束关系:

1满足VALID/READY握手 2写响应必须伴随最后一次写传输 3读数据必须跟随读地址

握手信号的独立性:

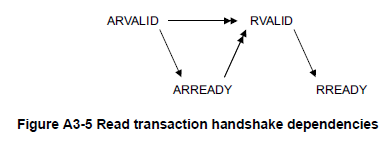

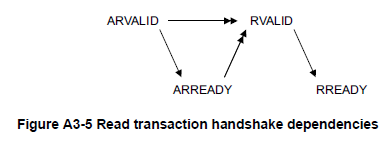

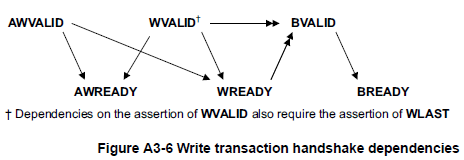

一个箭头表示不具备严格的先后关系,两个箭头表示具备严格的先后关系。

读交易的握手信号独立性:

Valid信号是master设置的,Ready信号是slave设置的。

(1)首先要准备好读地址(AR)并且获得响应。但是ARVALID和ARREADY没有强先后关系。

(2)在ARVALID/ARREADY都为1的时候,才允许master将RVALID置为1。这很容易理解,因为如果读地址没有得到Ready响应,读到的数据很可能是错的。

(3)RVALID和RREADY没有强先后关系。

写交易的握手信号独立性:

VALID/READY握手信号和刚才的分析都是一致的。

写地址和写数据也没有依赖性。

但是写响应BVALID必须等AWVALID/AWREADY,WVALID/WREADY都为1,即写完数据之后再响应。

从设备的BVALID信号一定要等待WLAST信号,因写响应只在最后一次传输出现。

这里强调,从设备的BVALID信号一定不要等待主设备BREADY信号置1。

从设备写响应交易的握手信号独立性:

任何VALID都不能等待READY,但是READY可以等待VALID。

写响应信号BVALID必须等待AWVALID/AWREADY, WVALID/WREADY都为1时才可以为1

从设备的BVALID信号一定要等待WLAST信号,因写响应只在最后一次传输出现。

这里强调,从设备的BVALID信号一定不要等待主设备BREADY信号置1

AXI的读操作

AXI读只涉及到两个通道,读地址通道和读数据通道。Master将地址和控制信息通过读地址送到送入Slave, Slave再将数据通过读数据通道返回给Master

AXI写操作

AXI写操作涉及到3个通道。分别是写地址通道、写数据通道和写响应通道。Master首先将地址和控制信息通过写地址通道送到Slave,然后将数据通过写数据通道送到Slave,Slave在收到数据后会进行写响应。所以这是一种带反馈的写入。

AXI协议总结

全局信号:ACLK, ARESETN. 其中ARESETN必须同步释放。

基本握手信号:VALID/READY。 发送方(source)将VALID置位表示数据有效,接收方(dest)将READY置位表示数据可以被接收。当VALID/READY都为高时,数据有效。

图A3-2~图A3-4显示了几种常见的时序。

但是并不推荐默认将READY置0,因为会浪费一个CLK。(判断VALID并拉高READY耗费一个CLK,source判断READY为高又要一个CLK, 这种情况如图A3-2,完成一次传输至少要耗费2个clk)

握手信号的独立性:

VALID信号不应依赖于READY信号。

READY信号可以等待VALID信号到来再置1,也可以不等待。后者效率更高。

AXI4的5个通道:写通道有3个,读通道有2个。我认为这5个通道中,除了Write Response通道都是从master的角度去看的。每个通道都遵循上述的VALID/READY握手协议,具体的信号名字有所区分。

Abbr:

AW-Addr Write, AR-Addr Read, W-Write data, B-Response, AR-Addr Read, R-Read data

Channel之间的关系

AXI4 Channel仅有以下简单的约束关系:

1满足VALID/READY握手 2写响应必须伴随最后一次写传输 3读数据必须跟随读地址

握手信号的独立性:

一个箭头表示不具备严格的先后关系,两个箭头表示具备严格的先后关系。

读交易的握手信号独立性:

Valid信号是master设置的,Ready信号是slave设置的。

(1)首先要准备好读地址(AR)并且获得响应。但是ARVALID和ARREADY没有强先后关系。

(2)在ARVALID/ARREADY都为1的时候,才允许master将RVALID置为1。这很容易理解,因为如果读地址没有得到Ready响应,读到的数据很可能是错的。

(3)RVALID和RREADY没有强先后关系。

写交易的握手信号独立性:

VALID/READY握手信号和刚才的分析都是一致的。

写地址和写数据也没有依赖性。

但是写响应BVALID必须等AWVALID/AWREADY,WVALID/WREADY都为1,即写完数据之后再响应。

从设备的BVALID信号一定要等待WLAST信号,因写响应只在最后一次传输出现。

这里强调,从设备的BVALID信号一定不要等待主设备BREADY信号置1。

从设备写响应交易的握手信号独立性:

任何VALID都不能等待READY,但是READY可以等待VALID。

写响应信号BVALID必须等待AWVALID/AWREADY, WVALID/WREADY都为1时才可以为1

从设备的BVALID信号一定要等待WLAST信号,因写响应只在最后一次传输出现。

这里强调,从设备的BVALID信号一定不要等待主设备BREADY信号置1

AXI的读操作

AXI读只涉及到两个通道,读地址通道和读数据通道。Master将地址和控制信息通过读地址送到送入Slave, Slave再将数据通过读数据通道返回给Master

AXI写操作

AXI写操作涉及到3个通道。分别是写地址通道、写数据通道和写响应通道。Master首先将地址和控制信息通过写地址通道送到Slave,然后将数据通过写数据通道送到Slave,Slave在收到数据后会进行写响应。所以这是一种带反馈的写入。

4493

4493

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?