本章搭建的小型SOPC包括GPIO模块,UART控制器,Flash控制器,SDRAM控制器等,这些控制器与OpenMIPS处理器都连接到Wishbone总线互联矩阵上。

13.1 小型SOPC的结构

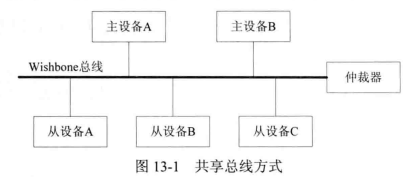

- Wishbone总线共有四中互联方式:点对点、数据流、共享总线、交叉互联。

- 点对点方式中,一般只有一个主设备,一个从设备,但是对于一个片上系统而言,一般存在多个模块,并且摸一个模块能够访问其余多个模块,比如存在CPU、DMA控制器,Flash控制器,SDRAM控制器,GPIO等,其中CPU、DMA控制器作为主设备,Flash控制器、SDRAM控制器、GPIO作为从设备。主设备CPU和DMA控制器都可以访问所有的从设备,当两者对同一设备发出访问请求时,就需要一个仲裁机制来判断哪个主设备占用总线,所有,片上系统一般使用共享总线或者交叉互联的方式。

- 共享总线

同一时刻只能有一对主、从设备建立通信。

- 交叉互联

主要用于多个主设备同时访问多个从设备的情况,在这种连接方式下,主设备发出对某个从设备的访问请求,仲裁器查看总线和从设备是否空闲,从而决定是否给主设备总线访问权。

本章建立的小型SOPC使用交叉互联的方式,Wishbone总线使用的是OpenCores站点提供的开源 项目WB_CONMAX,这是一个Wishbone总线互联矩阵。

13.2 Wishbione总线互联矩阵WB_CONMAX

特点:

- 支持8个Wishbone主设备

- 支持16个Wishbone总线从设备

- 内置仲裁器,支持1、2或4个优先级

- 允许多对主从设备同时相互通信

- 支持Wishbone B2版本

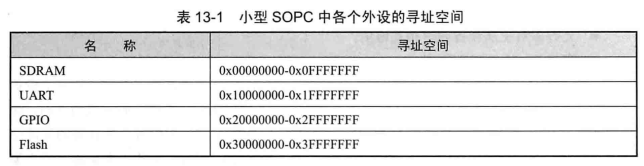

主设备选择从设备进行通信时,依据主设备提供的Wishbone地址的高4位确定是选择哪一个从设备进行通信,每个从设备的寻址空间大小都是256M,其中设备0的寻址空间是0x00000000-0x0FFFFFFF

一个实用的片上系统通常将程序放置在Flash中,系统启动后从Flash读取第一条指令,上表可知Flash对应的是从地址0x30000000处开始取指,只需要修改取指阶段的PC模块即可实现此目的。

13.3 GPIO

GPIO是以位为单位进行数字输入输出的I/O接口,作为单纯的通用输入/输出 I/O,输入时从外部读取输入信号,输出时将写入的值输出到外部。处理器通过GPIO可以与各种设备相连接,例如:LED、开关、七段数码管等。

本章建立的小型SOPC将直接使用OpenCores站点提供的开源项目GPIO IP Core。特点:

- I/O接口数量从1到32可配置

- 所有的I/O接口都可以配置为双向接口

- 输入接口可以触发中断

- 具有复用输入接口,GPIO最终的输出信号可以是Wishbone总线接口的输入信号,也可以是复用输入接口信号

- 可以采用Wishbone总线的时钟,也可以采用单独的时钟

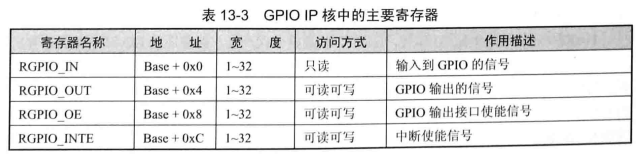

GPIO IP核的功能是通过配置一系列寄存器实现的,主要寄存器如表13-3所示。

13.4 UART控制器

13.4.1 UART简介

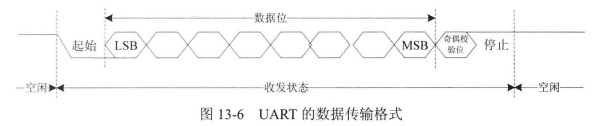

(1)UART数据传输

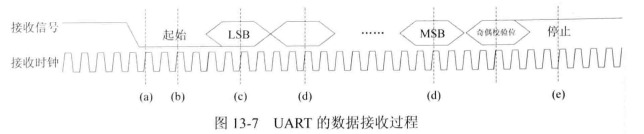

(2)UART数据接收

采用比波特率高的采样频率实现。实际使用中,一般使用比波特率高16倍的接受时钟进行采样。

(3)流控制

数据在两个UART之间传输时,常出现丢失数据的现象,比如,两台PC的处理速度不同,如果接收方数据缓冲区已满,那么此时继续发送来的数据就会丢失。解决方法是当接受方数据处理不过来时,发出不再接受的信号,发送方则停止发送,知道收到“可以继续发送”的信号。流控制包括硬件流控制和软件流控制。

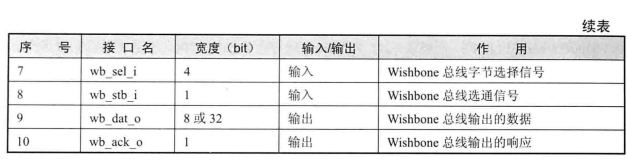

13.4.2 UART16550 IP核介绍

13.5 Flash控制器

13.5.1 Flash简介

本章设计的小型SOPC将程序保存在Flash中,并且从Flash启动,所以需要Flash控制器,用来进行Flash的读操作。Flash主要有两种:NAND flash、NOR flash,前者以块为基本单位进行访问,后者以字为基本单位进行访问,因此,程序可以直接在NOT flash里面运行,不必把程序复制到RAM里才运行。因此,一般把系统启动代码存放到NOR flash中。

13.5.2 Flash控制器设计

本章设计的SOPC在DE2开发平台上运行,其上的flash芯片数据位宽为8位,一条指令32位,所以共需要4次flash读操作。

13.5.3 Flash控制器的实现

13.6 SDRAM控制器

SDRAM读写速度快于Flash而且比Flash成本低,所以一般片上系统都具有较大容量SDRAM作为程序的主运行空间。

13.6.1 SDRAM简介

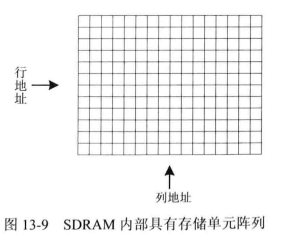

SDRAM 是同步动态随机访问存储器,内部有存储单元阵列,给出行列地址,就可以选择对应的存储单元。

13.6.1.1 SDRAM结构

这样的存储单元阵列称为Bank,在一个SDRAM中往往有多个Bank,寻址的时候需要给出对应Bank的编号。

13.6.1.2 SDRAM的刷新

通过电容存储信息,需要定期刷新以维持原有信息,刷新的方法是定时重复对SDRAM进行读出和再写入,以使电容中泄露的电荷得到补充。

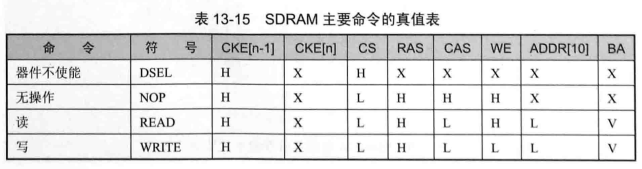

13.6.1.3 SDRAM的命令

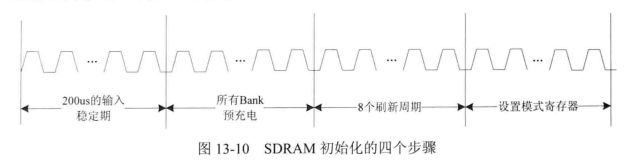

13.6.1.4 SDRAM初始化

13.6.1.5 模式寄存器

定义了SDRAM的运行模式,包括CAS延迟,突发类型,突发长度工作模式,写入突发模式等。模式寄存器的宽度是13bit,分为多个字段,重点包括突发长度,突发类型,CAS延迟三个字段。

13.6.1.6 Bank行激活

SDRAM中有多个Bank,在进行任何读写操作之前,要先选择进行操作的Bank,然后激活这个bank中相应的行,通过执行命令ACT来完成这个工作。

13.6.1.7 SDRAM读写

一般是突发读写,一个时钟周期读出一个新的数据,直到达到设定的突发长度。

13.6.1.8 SDRAM的时间参数

13.6.2 SDRAM CONTROLLER IP核

本章使用OpenCores站点提供的开源SDRAM控制器IP核,通过总线接收访问请求,然后转化为SDRAM的操作命令,将操作结果传递回总线。

13.7 实现基于实践版OpenMIPS的小型SOPC

将OpenMIPS处理器,Wishbone总线互联矩阵、GPIO模块、UART控制器,Flash控制器,SDRAM控制器连接在一起。

2614

2614

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?