学习前的建议

以下是一些学习定点加法和减法运算的建议:

-

掌握定点数的表示方法:在进行定点加法和减法运算之前,需要先了解定点数的表示方法,包括定点数的位数、小数点位置以及符号位等信息。

-

理解定点加法和减法的原理:定点加法和减法的原理和补码加法的原理类似,但是需要考虑到定点数的位数和小数点位置等因素。建议先了解定点数的表示方法,再通过实例演练加减法的过程,掌握定点加法和减法的基本原理。

-

学习进位和溢出的处理方法:在进行定点加法和减法运算时,需要注意处理进位和溢出的情况,例如,当两个正数相加结果超出了定点数的表示范围时,会产生溢出;当两个负数相加结果超出了定点数的表示范围时,同样也会产生溢出。因此,建议学习进位和溢出的处理方法,以保证运算结果的准确性。

-

利用模拟器和实验平台进行实践:定点加法和减法的原理比较抽象,建议通过模拟器和实验平台进行实践,例如,使用 Verilog HDL 或者其他模拟器进行定点加法和减法的实现,加深对定点加法和减法的理解和掌握。

总之,学习定点加法和减法运算需要深入理解定点数的表示方法、加法和减法的原理,同时也需要通过实践加深对知识点的掌握,不断练习和巩固。

学习目标:

在学习计算机组成原理中,我希望能够深入理解定点加法和减法运算的原理和方法,掌握定点数的表示方法,学会处理进位和溢出的情况,同时也希望能够通过实践加深对知识点的理解和掌握。具体来说,我计划在接下来的一个月内,完成以下学习目标:

-

掌握定点数的表示方法,包括定点数的位数、小数点位置以及符号位等信息。

-

理解定点加法和减法的原理和方法,掌握处理进位和溢出的情况。

-

学习使用 Verilog HDL 或者其他模拟器进行定点加法和减法的实现,加深对知识点的理解和掌握。

-

进行一些练习和实验,例如,实现定点加法和减法的模块,验证其正确性,并进行一些性能测试等。

-

最后,总结和复习所学的知识点,确保对定点加法和减法的原理和方法有一个深入的理解和掌握。

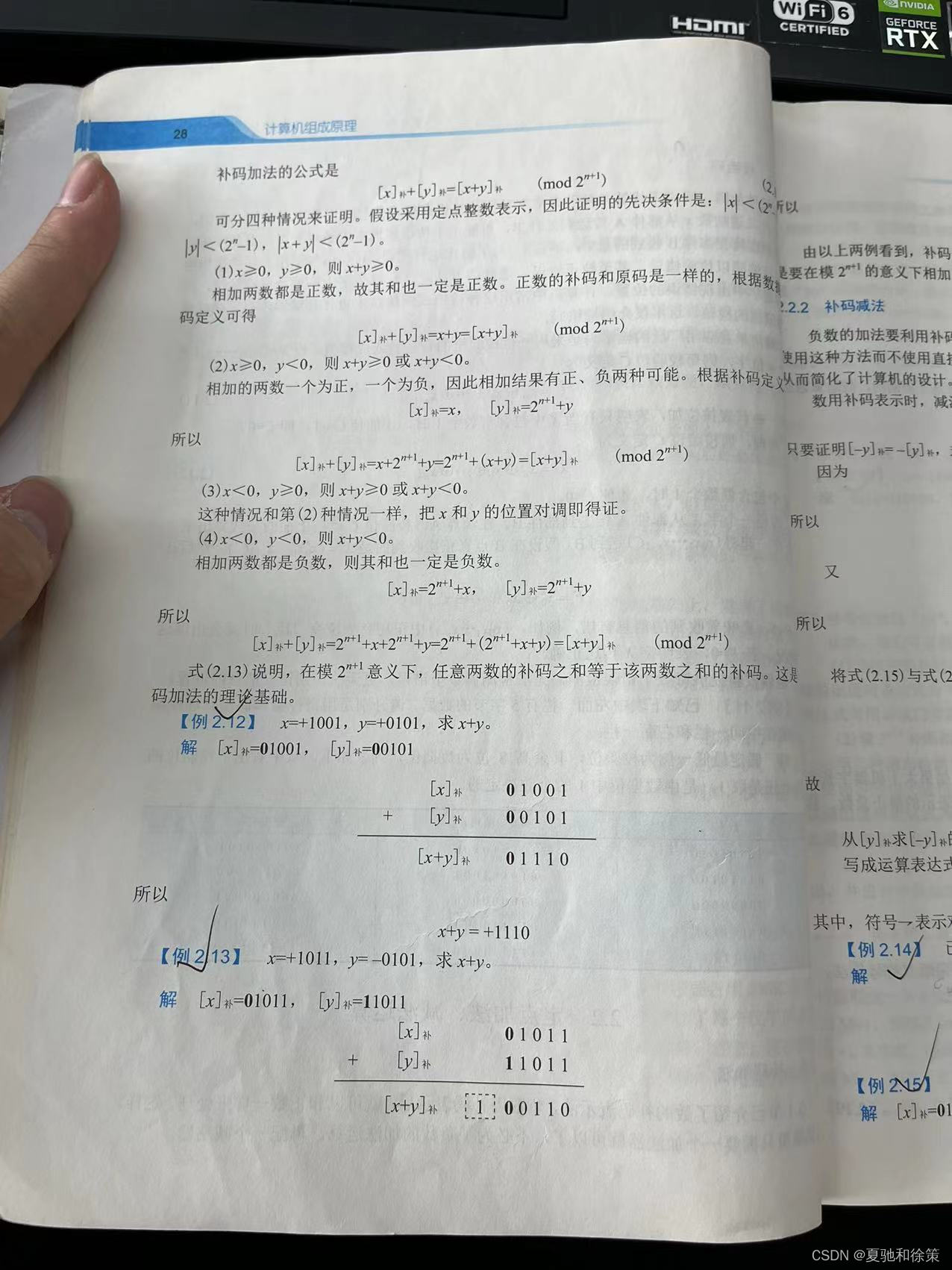

2.2.1 补码加法:

我的理解:

补码加法是计算机中常用的一种加法方式,可以快速实现整数的加法运算。补码加法的基本原理是:将两个补码相加,然后判断是否有进位或溢出,并根据情况进行进一步处理。下面,我将逐步讲解补码加法的实现步骤:

-

将两个补码的符号位进行比较,如果符号位相同,则表示两个数的加法结果为同号,否则表示两个数的加法结果为异号。例如,如果要计算 5 + (-3),则需要将 5 和 -3 转换成对应的补码形式,然后比较它们的符号位,因为 5 的符号位为 0,-3 的符号位为 1,所以这两个数的加法结果为异号。

-

将两个补码进行相加,这个过程和普通的加法运算类似,但需要注意的是,在计算加法时,需要将符号位也进行相加,因为补码的符号位也代表了数值的正负。例如,计算 5 + (-3) 的补码时,需要将 5 和 -3 的补码进行相加,得到 00101 + 11011 = 00000(忽略掉最高位的进位),这个结果的补码为 11111,表示 -8。

-

判断是否有进位或溢出。如果两个正数相加得到的结果超出了最大表示范围,或者两个负数相加得到的结果超出了最小表示范围,就会产生溢出。例如,如果计算 127 + 1,则会产生溢出,因为最大表示范围为 01111111,加 1 后会得到 10000000,超出了最大表示范围。如果一个正数和一个负数相加,但没有产生进位,也就是说,它们的绝对值之和小于等于最大表示范围,但符号位不一致,也会产生溢出。

-

根据产生的进位或溢出进行进一步处理。如果产生了进位,需要将最高位的进位加到计算结果中;如果产生了溢出,则需要将溢出的信息记录下来,并进行进一步的处理,例如,抛弃溢出的位或者将其作为错误信息返回。

总之,补码加法是计算机中常用的一种加法方式,能够快速实现整数的加法运算。补码加法的实现过程包括符号位比较、补码相加、进位溢出处理等步骤。

前置知识储备

理解补码加法的概念需要先了解一些基本的概念,如原码、反码、补码等。

在计算机中,数据一般以二进制的形式存储。原码是最基本的表示方式,直接用二进制表示数值的大小和符号,其中最高位表示符号位,0 表示正数,1 表示负数。例如,十进制数 5 的原码是 00000101,十进制数 -3 的原码是 10000011。

反码是将原码中的符号位不变,其余位按位取反得到的结果。例如,十进制数 5 的反码是 00000101,十进制数 -3 的反码是 11111100。

补码是将反码加 1 得到的结果,其中最高位仍然表示符号位。补码是计算机中最常用的一种数值表示方式,因为它能够将减法转换为加法,从而简化计算机的设计。例如,十进制数 5 的补码是 00000101,十进制数 -3 的补码是 11111101。

补码加法是在补码的基础上进行的加法运算。在补码加法中,相同符号的两个数的加法运算与原码加法一致,而不同符号的两个数的加法则需要通过符号位比较和进位处理来实现。

因此,理解补码加法的概念需要理解原码、反码、补码等数值表示方式,以及它们之间的相互转换规则。在了解这些基本概念的基础上,理解补码加法就变得相对简单了。

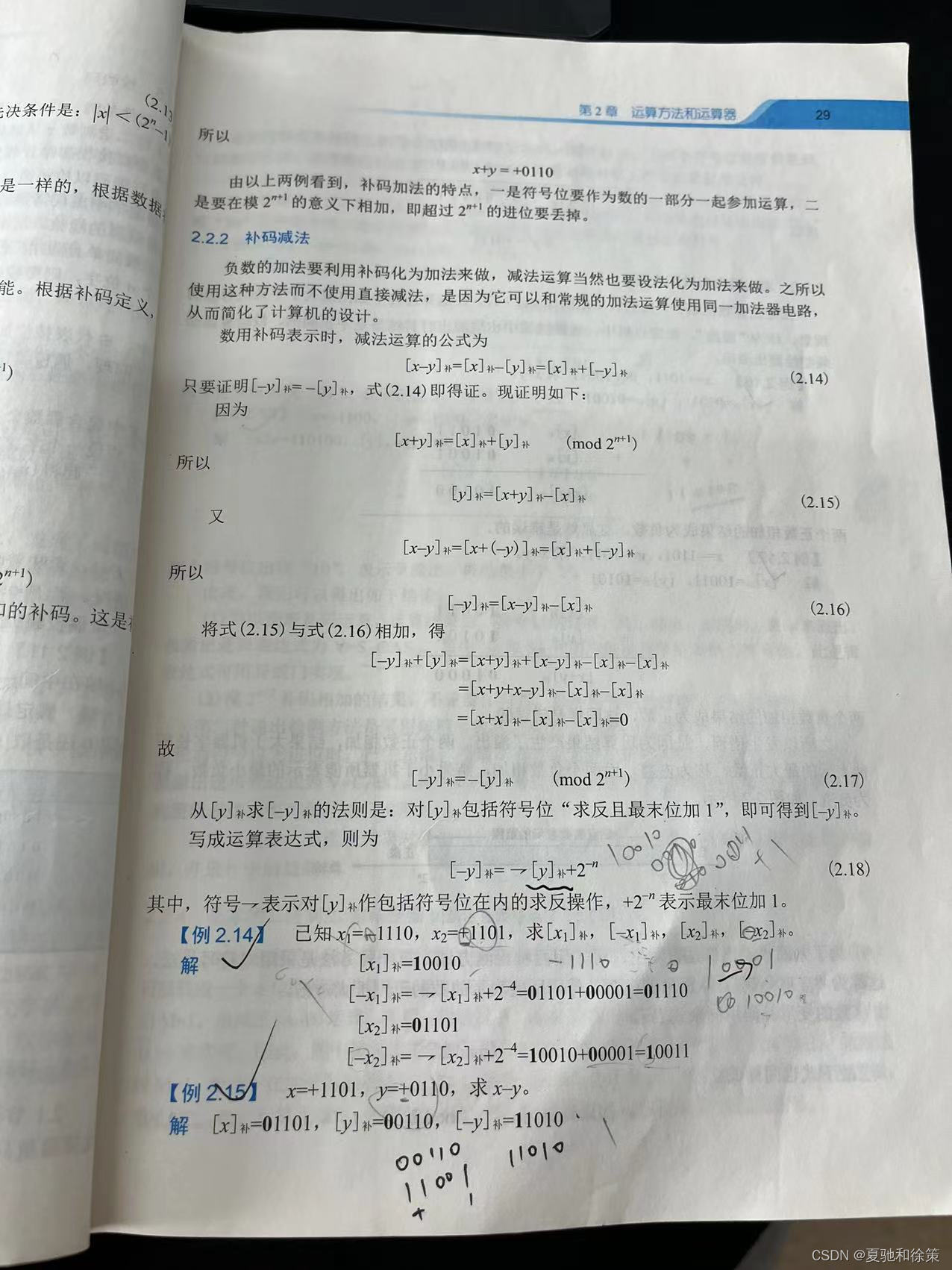

2.2.2 补码的减法

补码减法可以通过补码加法来实现。其基本思路是,将减数取反后加上被减数,即可得到减法的结果。

具体来说,设要计算的减法表达式为 A-B,其中 A 和 B 均为补码表示的数。我们可以先将 B 取反,得到 -B 的补码表示。然后,将 A 和 -B 作为两个补码数进行加法运算,即计算 A + (-B) 的补码表示。最后,将结果转换回原码表示,就得到了减法的结果。

以下是一个例子,计算 6-3 的补码表示:

- 计算被减数 6 的补码表示:+6 = 00000110

- 计算减数 3 的补码表示:+3 = 00000011,-3 的补码表示为 11111101

- 将 A = 00000110 和 -B = 11111101 作为两个补码数进行加法运算:A + (-B) = 00000110 + 11111101 = 00000011,即 -3 的补码表示

- 将 -3 的补码表示转换回原码表示,得到减法结果为 -3

因此,补码减法实际上就是将减法转换为加法,通过将减数取反后加上被减数来实现。这样可以避免减法的复杂性,简化计算机的设计,同时还能够有效地处理溢出问题。

(2)如何求-y的补码?

公式:包括符号位在内求反且最末位+1;

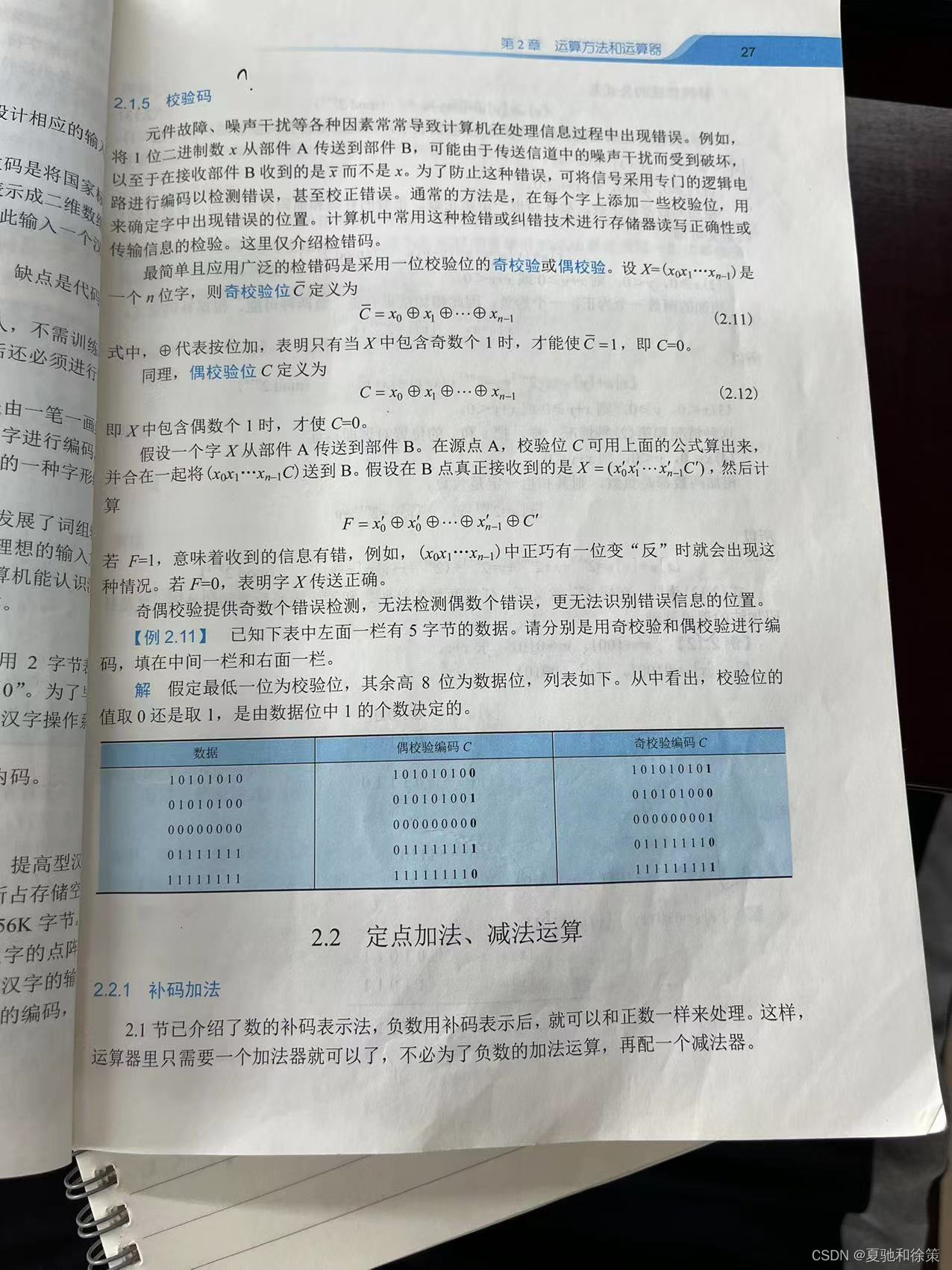

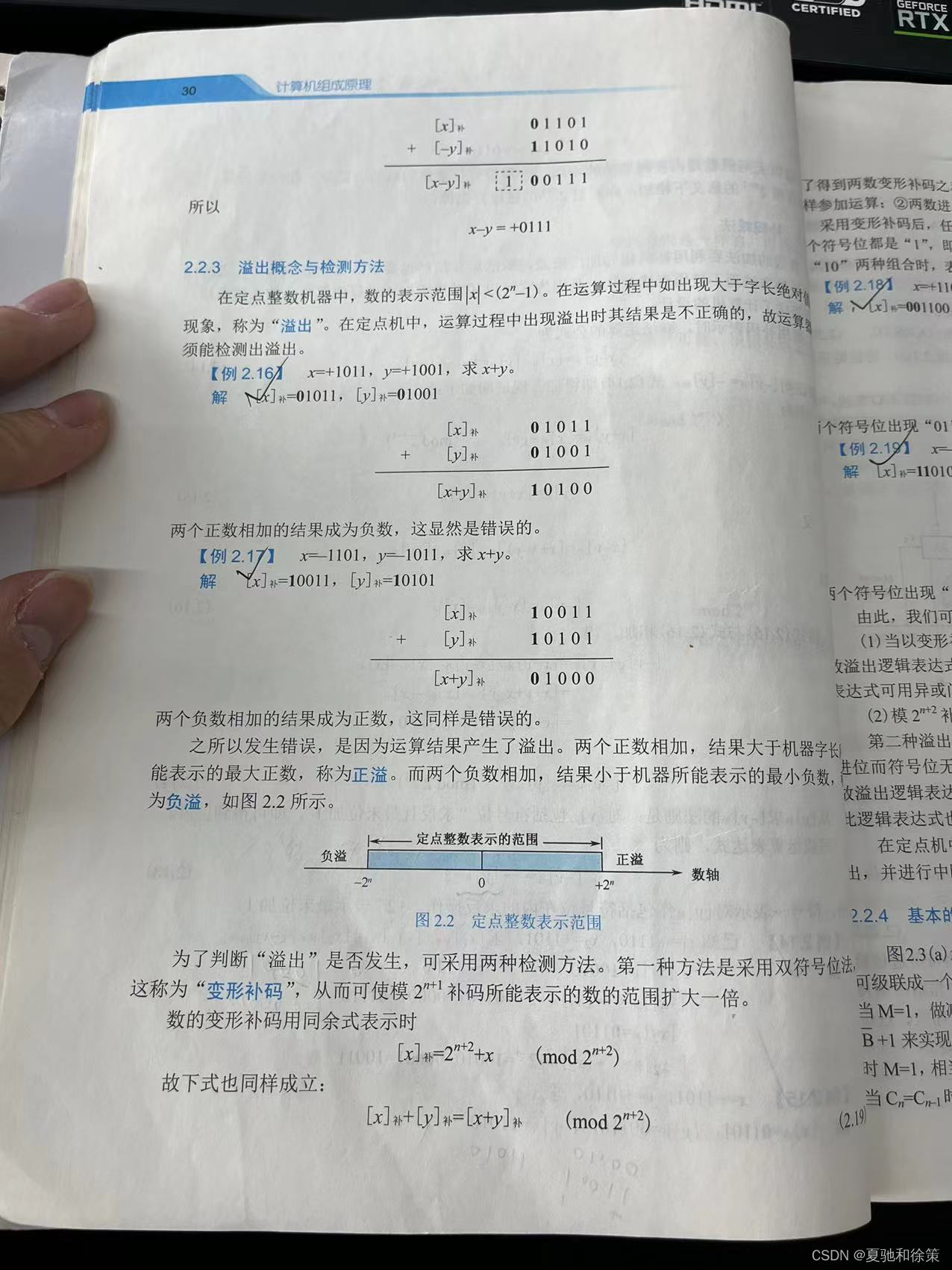

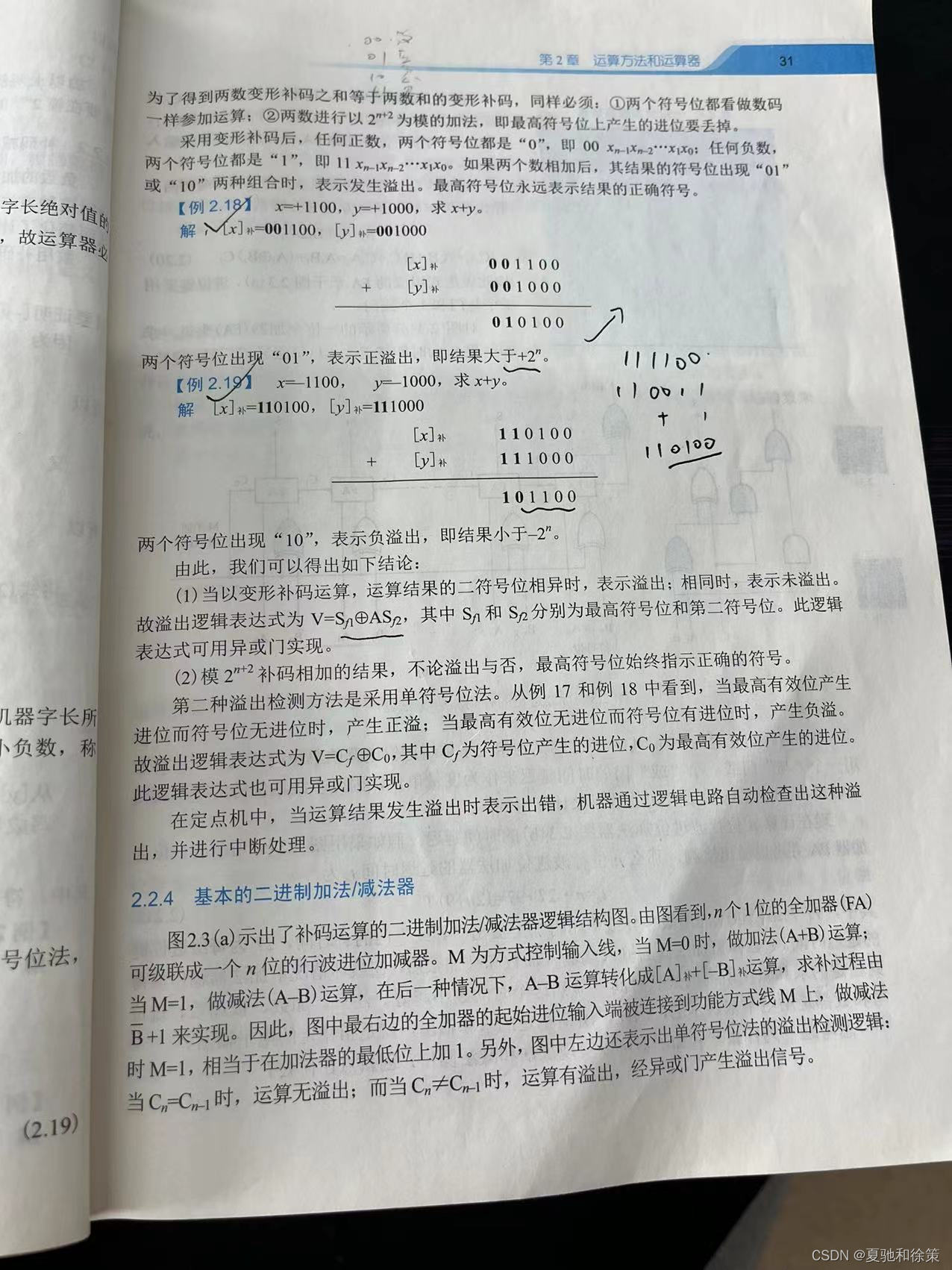

2.2.3 溢出概念与检测方法

在计算机中进行数值计算时,当运算结果超出了数据类型所能表示的范围,就会发生溢出(overflow)现象。溢出可能会导致程序崩溃、结果不准确、数据损坏等问题,因此在编写程序时需要注意溢出的情况,并进行相应的检测和处理。

下面是一些常见的检测溢出的方法:

-

符号位检查法:对于有符号整数,将运算结果的符号位与操作数的符号位进行比较,如果不一致,则发生了溢出。

-

位运算法:对于无符号整数,将运算结果右移数位,然后与操作数进行比较,如果不一致,则发生了溢出。

-

加法溢出检测法:对于加法运算,当两个正数相加得到的结果小于其中一个操作数时,或者当两个负数相加得到的结果大于其中一个操作数时,就会发生溢出。

-

减法溢出检测法:对于减法运算,当一个正数减去一个负数得到的结果小于其中一个操作数的绝对值时,或者当一个负数减去一个正数得到的结果大于其中一个操作数的绝对值时,就会发生溢出。

-

乘法溢出检测法:对于乘法运算,当两个有符号整数相乘得到的结果超出了数据类型所能表示的范围时,就会发生溢出。

-

浮点数溢出检测法:对于浮点数,当结果的指数部分超过了表示范围时,就会发生溢出。

以上仅是一些常见的检测溢出的方法,具体应根据情况选择合适的方法进行检测。在实际编写程序时,可以使用语言提供的内置函数或库函数来检测溢出,也可以自行编写相应的检测代码。同时,在发现溢出时,应根据具体情况进行相应的处理,如抛出异常、返回错误码等。

(1)双符号位判别溢出的方法

01代表正溢出

10代表负溢出

其他情况代表正常

我的理解:

溢出是指在进行数值计算时,结果超出了所能表示的范围,导致计算机无法准确表示运算结果的情况。比如,在使用8位二进制补码表示有符号整数时,其范围为-128~127,如果两个-100的有符号整数相加,由于其结果为-200,超出了所能表示的范围,就会发生溢出。

理解溢出概念需要理解数据类型的表示范围和计算机运算方式。对于有符号整数来说,通常使用补码进行表示和运算。在进行加减法运算时,需要考虑符号位的进位和借位问题。而在进行乘法和除法运算时,则需要考虑数据溢出的问题。

发生溢出后,计算机通常会采取一些处理方式,如截断、舍入、抛出异常等,具体取决于编程语言和计算机体系结构。在实际编程中,需要注意避免溢出情况的发生,对于可能发生溢出的运算,应该进行溢出检测并进行相应的处理。

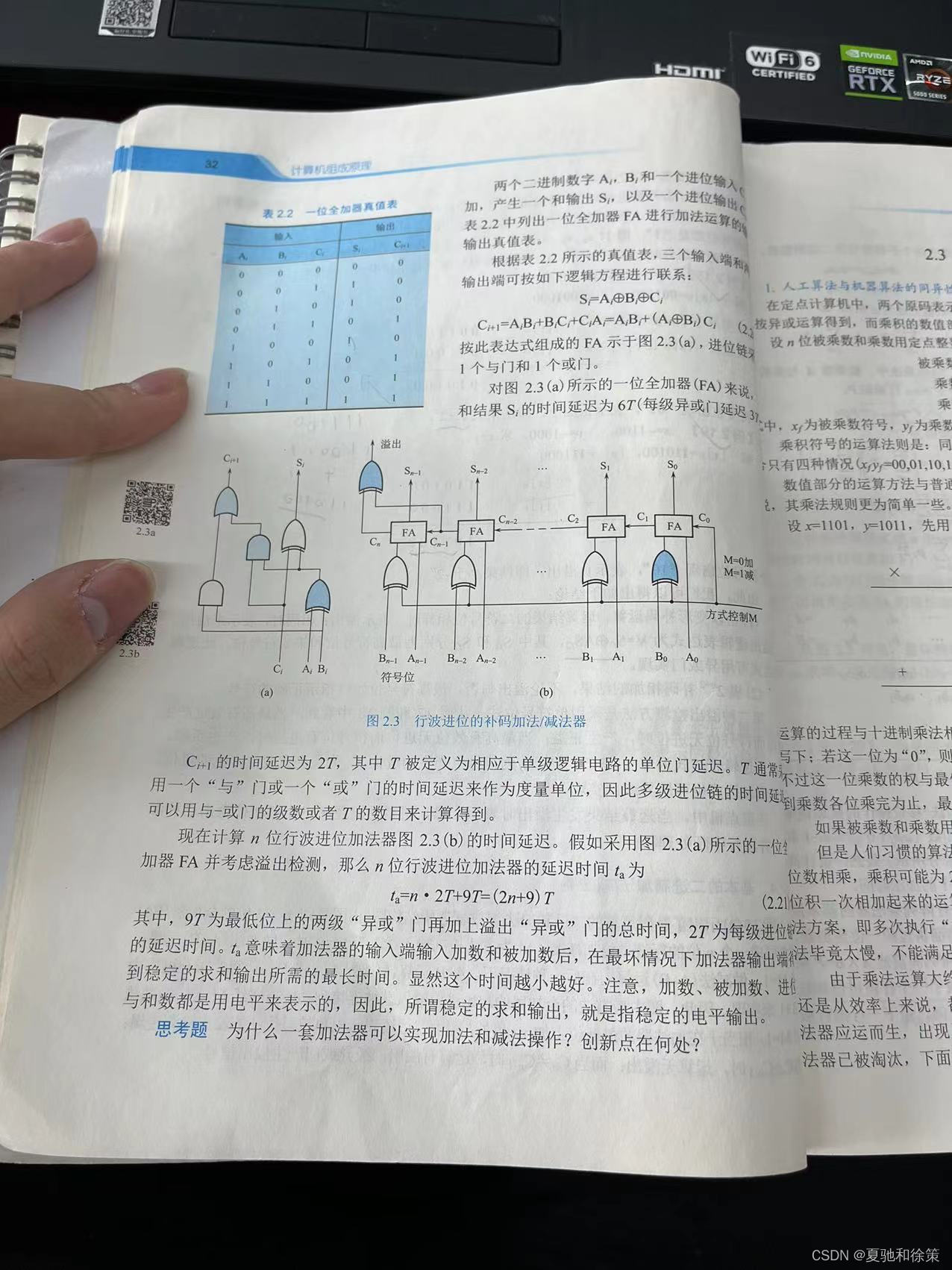

2.2.4 基本的二进制加法/减法器

2.2.4 基本的二进制加法/减法器

二进制加法器和减法器是计算机中最基本的电路之一,用于执行二进制数的加减运算。这些电路可以被组合在一起,构建更复杂的算术逻辑电路,如乘法器、除法器等。

二进制加法器的输入是两个二进制数和一个进位标志位(Carry-In),输出是一个二进制和结果和一个进位输出(Carry-Out)。二进制加法器可以使用半加器(Half-Adder)和全加器(Full-Adder)组成。

半加器只能处理两个二进制数的最低位加法,输出结果和一个进位位。全加器则可以处理两个二进制数的任意位加法,包括进位位,输出结果和一个进位位。

二进制减法器与加法器类似,但是需要进行补码运算来实现减法。补码减法可以通过将被减数取反并加1,然后与减数相加来实现。减法器的输入是两个二进制数和一个借位标志位(Borrow-In),输出是一个二进制差和一个借位输出(Borrow-Out)。减法器可以使用半减器(Half-Subtractor)和全减器(Full-Subtractor)组成。

半减器只能处理两个二进制数的最低位减法,输出结果和一个借位位。全减器则可以处理两个二进制数的任意位减法,包括借位位,输出结果和一个借位位。

以上是二进制加法器和减法器的基本概念和构成。在实际应用中,可以通过组合多个半加器或半减器,以及多个全加器或全减器,来实现更复杂的算术运算。

疑问 什么是行波进位加减器?

行波进位加法器(Ripple Carry Adder)是一种常见的二进制加法器,由多个全加器组成。它的原理是将两个二进制数的每一位相加,然后将进位输出给下一位进行相加。这种加法器的关键是产生进位信号,因为没有进位信号,后续的加法器无法正确计算出结果。

行波进位加法器的优点是简单易于实现,但是它的缺点是速度较慢,因为每一位的加法需要等待上一位的进位输出。因此,行波进位加法器的速度受到位数的限制,而且随着位数的增加,它的延迟会成倍增加。为了提高速度,可以采用更快的加法器结构,例如Carry Lookahead Adder(CLA)和Carry Select Adder(CSA)等。

文章介绍了定点数的表示方法,特别是定点加法和减法的运算原理,包括补码加法的步骤和处理进位、溢出的方法。此外,还讨论了如何通过模拟器和VerilogHDL实现定点运算,并提到了二进制加法器和减法器,如行波进位加法器的基本概念。

文章介绍了定点数的表示方法,特别是定点加法和减法的运算原理,包括补码加法的步骤和处理进位、溢出的方法。此外,还讨论了如何通过模拟器和VerilogHDL实现定点运算,并提到了二进制加法器和减法器,如行波进位加法器的基本概念。

1063

1063

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?