第六章 时序逻辑电路

6.1 概述

时序逻辑电路的基本概念

时序逻辑电路是区别于组合逻辑电路的一类重要电路。在组合逻辑电路中,任一时刻的输出信号仅依赖于当前的输入信号,而在时序逻辑电路中,输出信号不仅取决于当前输入信号,还取决于电路的当前状态,即电路的历史输入。因此,时序逻辑电路需要具备记忆功能。

时序逻辑电路一般由两个部分组成:

- 组合逻辑电路:负责当前输入信号和存储电路输出信号的逻辑运算。

- 存储电路:负责记忆电路的状态,通常由触发器(如D触发器、JK触发器等)构成。

例如,图6.1.1中的串行加法器电路展示了时序逻辑电路的典型结构。

时序逻辑电路的结构框图

时序逻辑电路的框图如图6.1.2所示,其中包含输入信号𝑋(𝑥1,𝑥2,...,𝑥𝑘)X(x1,x2,...,xk)、输出信号𝑌(𝑦1,𝑦2,...,𝑦𝑟)Y(y1,y2,...,yr)、存储电路的输入信号𝑍(𝑧1,𝑧2,...,𝑧𝑙)Z(z1,z2,...,zl)和存储电路的输出信号𝑄(𝑞1,𝑞2,...,𝑞𝑚)Q(q1,q2,...,qm)。

这些信号之间的逻辑关系可以用以下三个方程组描述:

输出方程

描述输出信号与输入信号及存储电路输出信号之间的关系

𝑦𝑖=𝑓𝑖(𝑥1,𝑥2,...,𝑥𝑘,𝑞1,𝑞2,...,𝑞𝑚)(𝑖=1,2,...,𝑟)yi=fi(x1,x2,...,xk,q1,q2,...,qm)(i=1,2,...,r)

驱动方程(激励方程)

描述存储电路的输入信号与输入信号及存储电路输出信号之间的关系

𝑧𝑖=𝑔𝑖(𝑥1,𝑥2,...,𝑥𝑘,𝑞1,𝑞2,...,𝑞𝑚)(𝑖=1,2,...,𝑙)zi=gi(x1,x2,...,xk,q1,q2,...,qm)(i=1,2,...,l)

状态方程

描述存储电路的次态信号与存储电路输入信号及存储电路当前输出信号之间的关系

𝑞𝑖′=ℎ𝑖(𝑧1,𝑧2,...,𝑧𝑙,𝑞1,𝑞2,...,𝑞𝑚)(𝑖=1,2,...,𝑚)qi′=hi(z1,z2,...,zl,q1,q2,...,qm)(i=1,2,...,m)

这些方程可以简写为向量函数的形式:

𝑌=𝐹[𝑋,𝑄]Y=F[X,Q]

𝑍=𝐺[𝑋,𝑄]Z=G[X,Q]

𝑄′=𝐻[𝑍,𝑄]Q′=H[Z,Q]

同步时序电路与异步时序电路

根据存储电路中触发器的动作特点,时序电路可以分为同步时序电路和异步时序电路:

- 同步时序电路:所有触发器的状态变化都在同一时钟信号操作下同时发生。

- 异步时序电路:触发器的状态变化不是同时发生的。

此外,时序电路根据输出信号的特点还可分为米利型(Mealy)电路和穆尔型(Moore)电路:

- 米利型电路:输出信号不仅取决于存储电路的状态,还取决于输入信号。

- 穆尔型电路:输出信号仅取决于存储电路的状态。

时序电路的分析方法

在分析时序电路时,需要将状态变量和输入信号一样当作逻辑函数的输入变量处理。由于状态变量的取值与电路的历史情况有关,时序电路的分析比组合电路复杂。

常用的分析方法包括:

- 状态表法:列出电路所有可能的状态及其对应的输出和次态。

- 状态图法:用状态图形象地描述电路的状态转换过程。

时序电路的设计方法

时序电路的设计较为复杂,通常包括以下步骤:

- 明确设计要求:确定电路所需的功能和性能指标。

- 状态分析与设计:定义状态,绘制状态图或状态表。

- 选择触发器类型:根据设计需要选择合适的触发器。

- 设计组合逻辑部分:实现状态转移逻辑和输出逻辑。

- 验证与优化:通过仿真或实验验证设计的正确性,并进行优化。

总结

通过以上分析,我们了解到时序逻辑电路不仅依赖于当前输入信号,还依赖于电路的状态。这使得时序逻辑电路在逻辑功能和电路结构上具有独特的特点。在设计与分析时序逻辑电路时,需要综合考虑状态变量、输入信号及其相互关系,采用系统化的方法进行分析与设计。

6.2 时序逻辑电路的分析方法

6.2.1 同步时序逻辑电路的分析方法

分析一个时序电路,就是要找出给定时序电路的逻辑功能。具体地说,就是要求找出电路的状态和输出的状态在输入变量和时钟信号作用下的变化规律。

首先讨论同步时序电路的分析方法。由于同步时序电路中所有触发器都是在同一个时钟信号操作下工作的,所以分析方法比较简单。

在本章6.1节中已经讲过,时序电路的逻辑功能可以用输出方程、驱动方程和状态方程全面描述。因此,只要能写出给定逻辑电路的这三个方程,那么它的逻辑功能也就表示清楚了。根据这三个方程,就能够求得在任何给定输入变量状态和电路状态下电路的输出和次态。分析同步时序电路时一般按如下步骤进行:

- 从给定的逻辑图中写出每个触发器的驱动方程(亦即存储电路中每个触发器输入信号的逻辑函数式)。

- 将得到的这些驱动方程代入相应触发器的特性方程,得出每个触发器的状态方程,从而得到由这些状态方程组成的整个时序电路的状态方程组。

- 根据逻辑图写出电路的输出方程。

示例 6.2.1

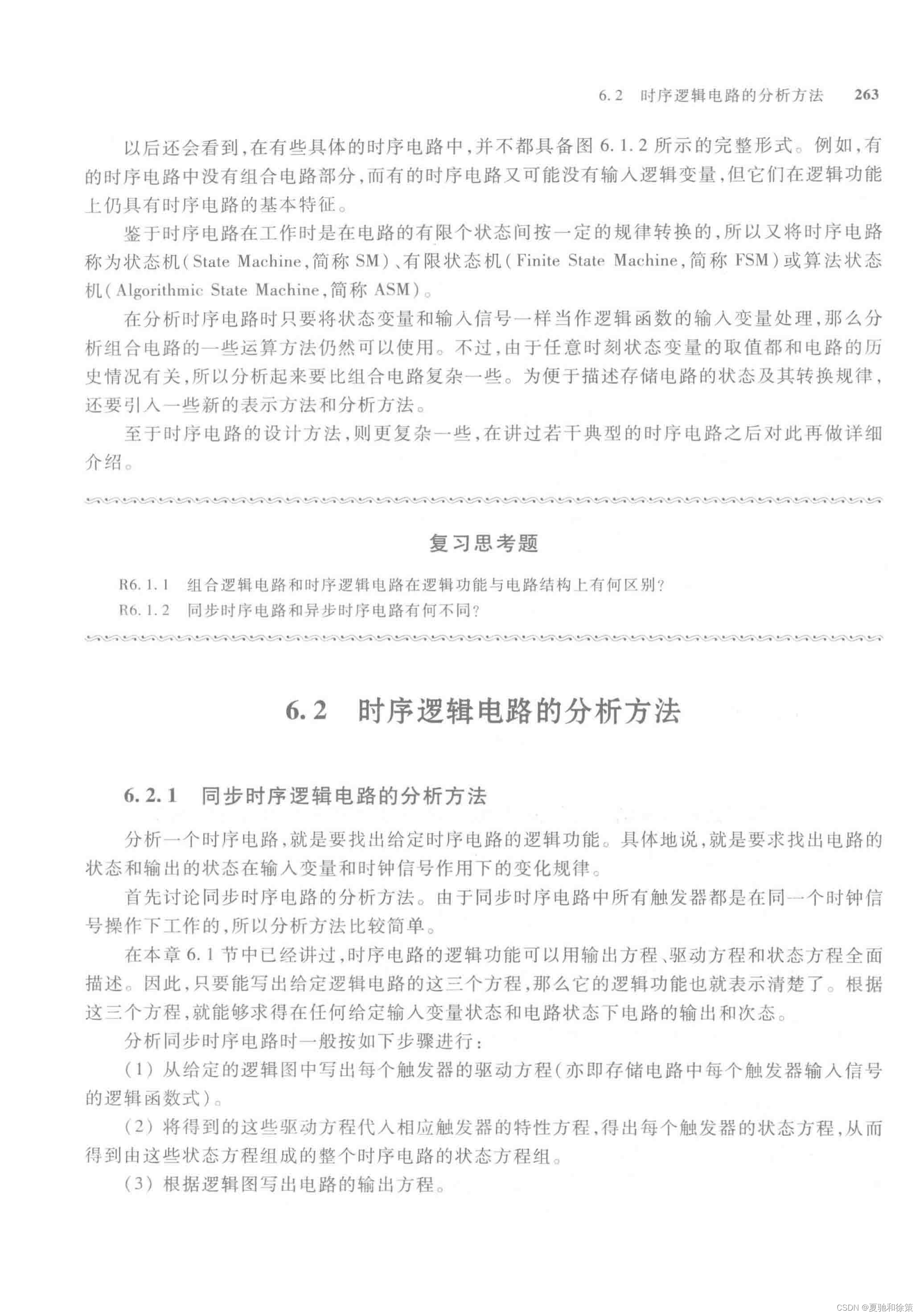

试分析图6.2.1所示时序逻辑电路的逻辑功能,写出它的驱动方程、状态方程和输出方程。FF₁、FF₂和FF₃是三个主从结构的TTL触发器,下降沿动作,输入端悬空时和逻辑1状态等效。

解:

-

从图6.2.1给定的逻辑图可写出电路的驱动方程为:

𝐽1=(𝑄2⋅𝑄3)′,𝐾1=1J1=(Q2⋅Q3)′,K1=1

𝐽2=𝑄1⋅𝑄2,𝐾2=(𝑄1′⋅𝑄3′)′J2=Q1⋅Q2,K2=(Q1′⋅Q3′)′

𝐽3=𝑄1⋅𝑄2,𝐾3=𝑄2J3=Q1⋅Q2,K3=Q2

-

将式(6.2.1)代入JK触发器的特性方程 𝑄′=𝐽⋅𝑄′+𝐾′⋅𝑄Q′=J⋅Q′+K′⋅Q 中去,于是得到电路的状态方程:

𝑄1′=(𝑄2⋅𝑄3)′⋅𝑄1′+𝑄1Q1′=(Q2⋅Q3)′⋅Q1′+Q1

𝑄2′=𝑄1⋅𝑄2⋅𝑄2′+(𝑄1′⋅𝑄3′)′⋅𝑄2Q2′=Q1⋅Q2⋅Q2′+(Q1′⋅Q3′)′⋅Q2

𝑄3′=𝑄1⋅𝑄2⋅𝑄3′+𝑄2Q3′=Q1⋅Q2⋅Q3′+Q2

-

根据逻辑图写出输出方程为:

𝑌=𝑄2⋅𝑄3Y=Q2⋅Q3

6.2.2 时序逻辑电路的状态转换表、状态转换图、状态机流程图和时序图

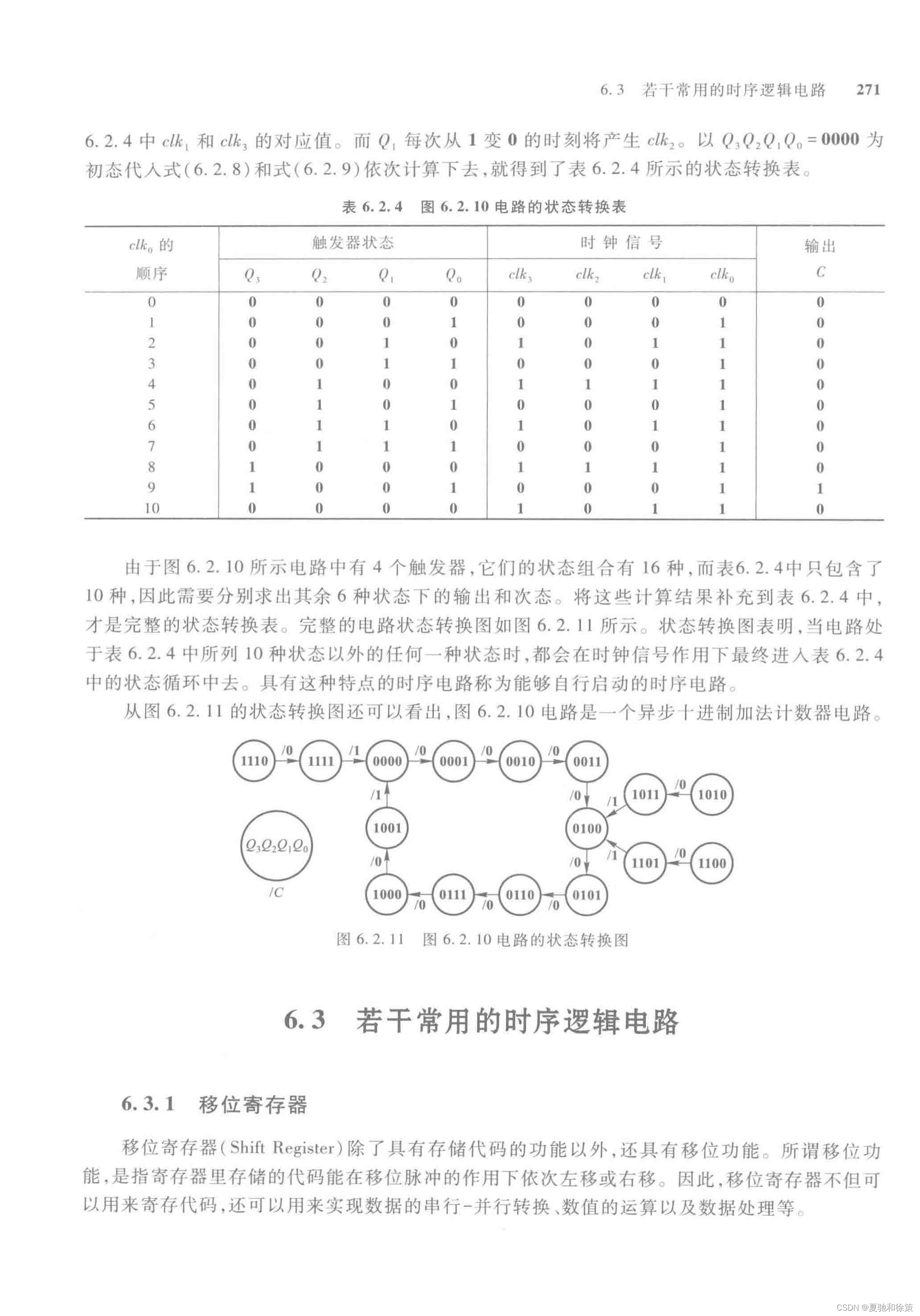

从理论上讲,有了驱动方程、状态方程和输出方程以后,时序电路的逻辑功能就已经描述清楚了。然而通过例6.2.1可以发现,从这一组方程式中还不能获得电路逻辑功能的完整印象。这主要是由于电路每一时刻的状态都和电路的历史情况有关的缘故。由此可以想到,如果将电路在一系列时钟信号作用下状态转换的全部过程找出来,则电路的逻辑功能便可一目了然了。

用于描述时序电路状态转换全部过程的方法有状态转换表(也称状态转换真值表)、状态转换图、状态机流程图和时序图。由于这几种方法和方程组一样,都可以用来描述同一个时序电路的逻辑功能,所以它们之间可以互相转换。此外,还可以用硬件描述语言对时序电路的逻辑功能进行描述,这一部分内容将在后面的有关章节中介绍。

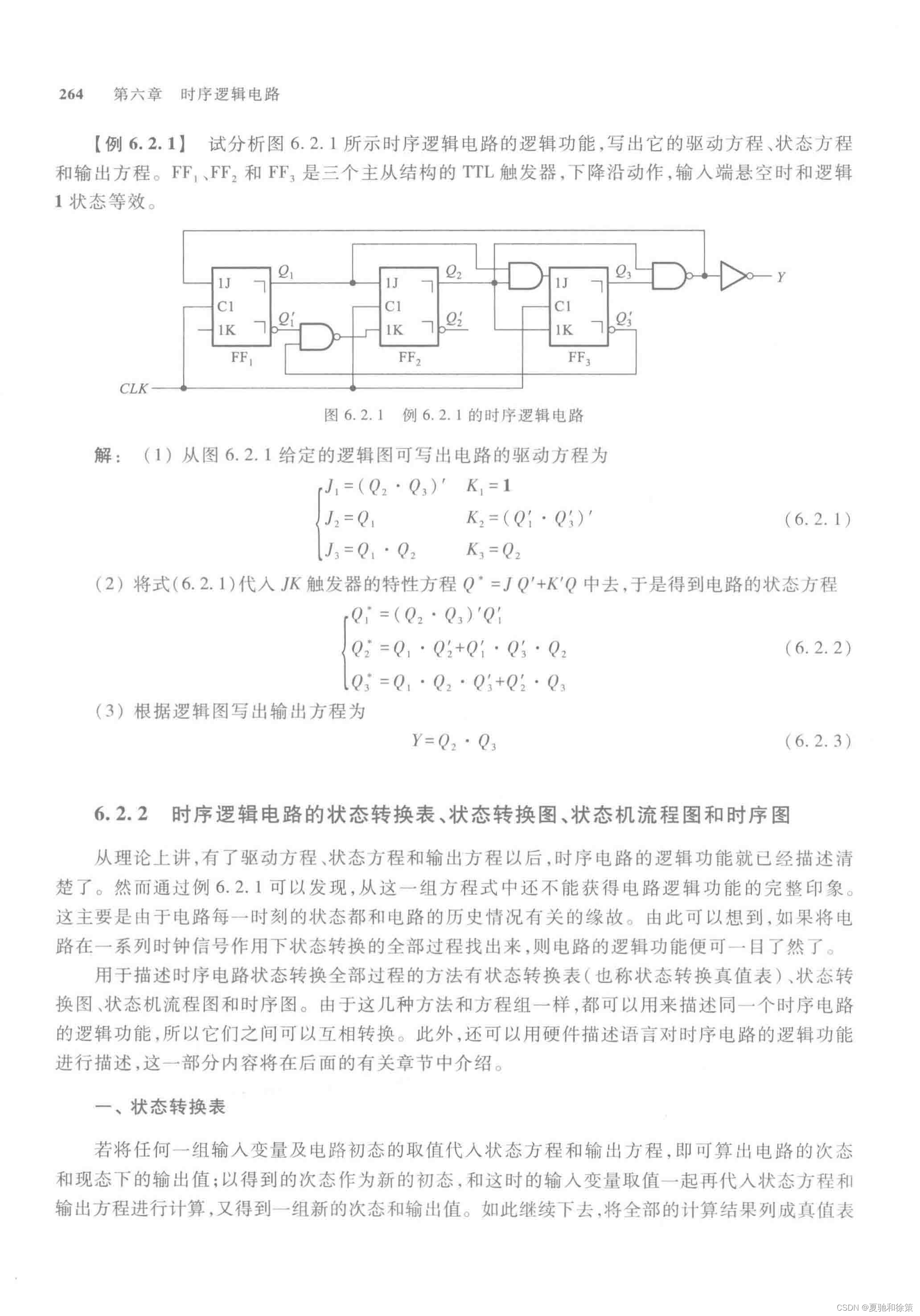

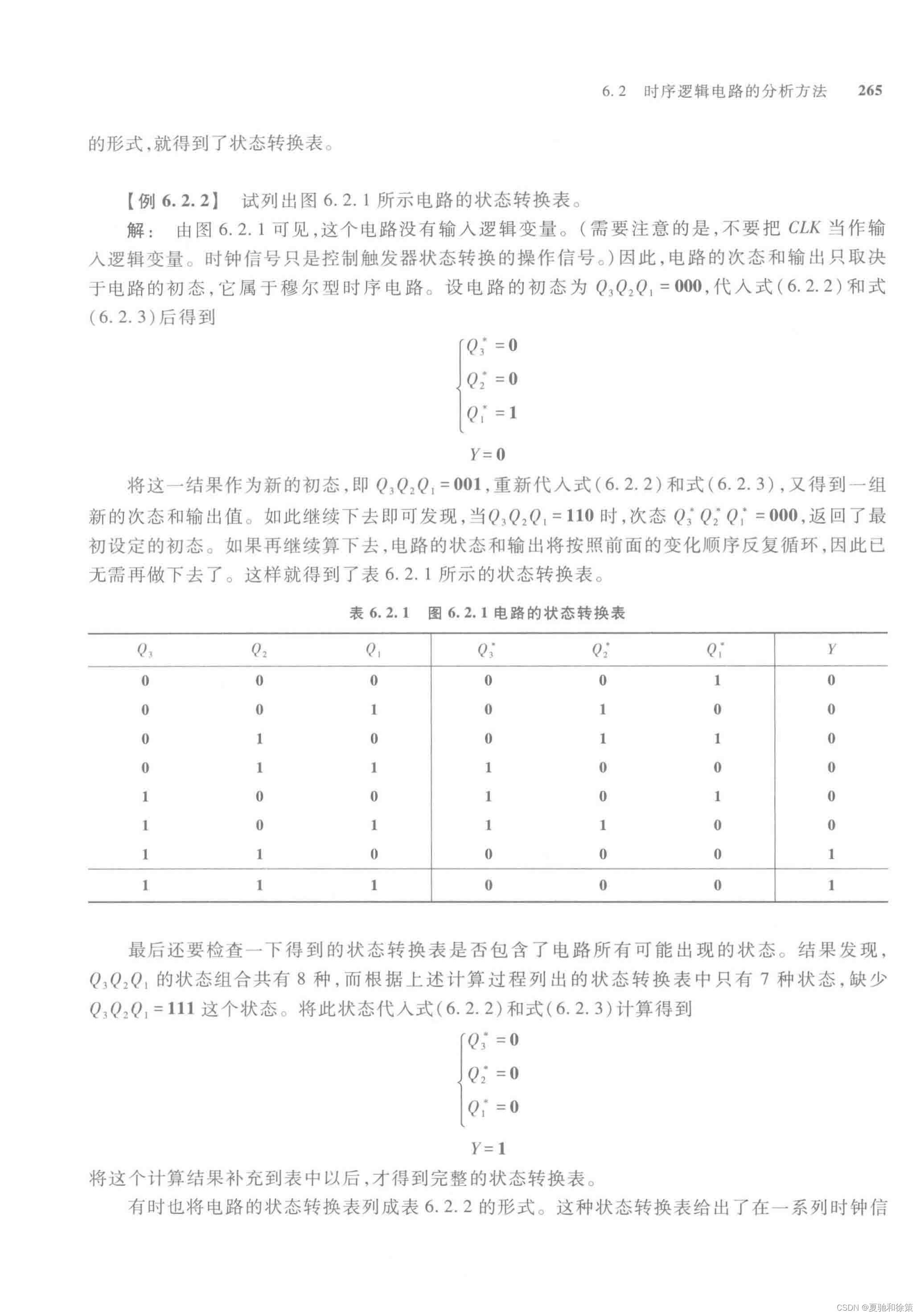

状态转换表

若将任何一组输入变量及电路初态的取值代入状态方程和输出方程,即可算出电路的次态和现态下的输出值;以得到的次态作为新的初态,和这时的输入变量取值一起再代入状态方程和输出方程进行计算,又得到一组新的次态和输出值。如此继续下去,将全部的计算结果列成真值表的形式,就得到了状态转换表。

示例 6.2.2

试列出图6.2.1所示电路的状态转换表。

解:

由图6.2.1可见,这个电路没有输入逻辑变量(需要注意的是,不要把CLK当作输入逻辑变量。时钟信号只是控制触发器状态转换的操作信号)。因此,电路的次态和输出只取决于电路的初态,它属于穆尔型时序电路。设电路的初态为 𝑄1𝑄2𝑄3=000Q1Q2Q3=000,代入式(6.2.2)和式(6.2.3)后得到:

𝑄1′=1Q1′=1

𝑄2′=0Q2′=0

𝑄3′=0Q3′=0

𝑌=0Y=0

将这一结果作为新的初态,即 𝑄1𝑄2𝑄3=001Q1Q2Q3=001,重新代入式(6.2.2)和式(6.2.3),又得到一组新的次态和输出值。如此继续下去即可发现,当 𝑄1𝑄2𝑄3=110Q1Q2Q3=110 时,次态 𝑄1𝑄2𝑄3=000Q1Q2Q3=000,返回了最初设定的初态。如果再继续算下去,电路的状态和输出将按照前面的变化顺序反复循环,因此已无需再做下去了。这样就得到了表6.2.1所示的状态转换表。

| Q_1 | Q_2 | Q_3 | Y |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 |

状态转换图

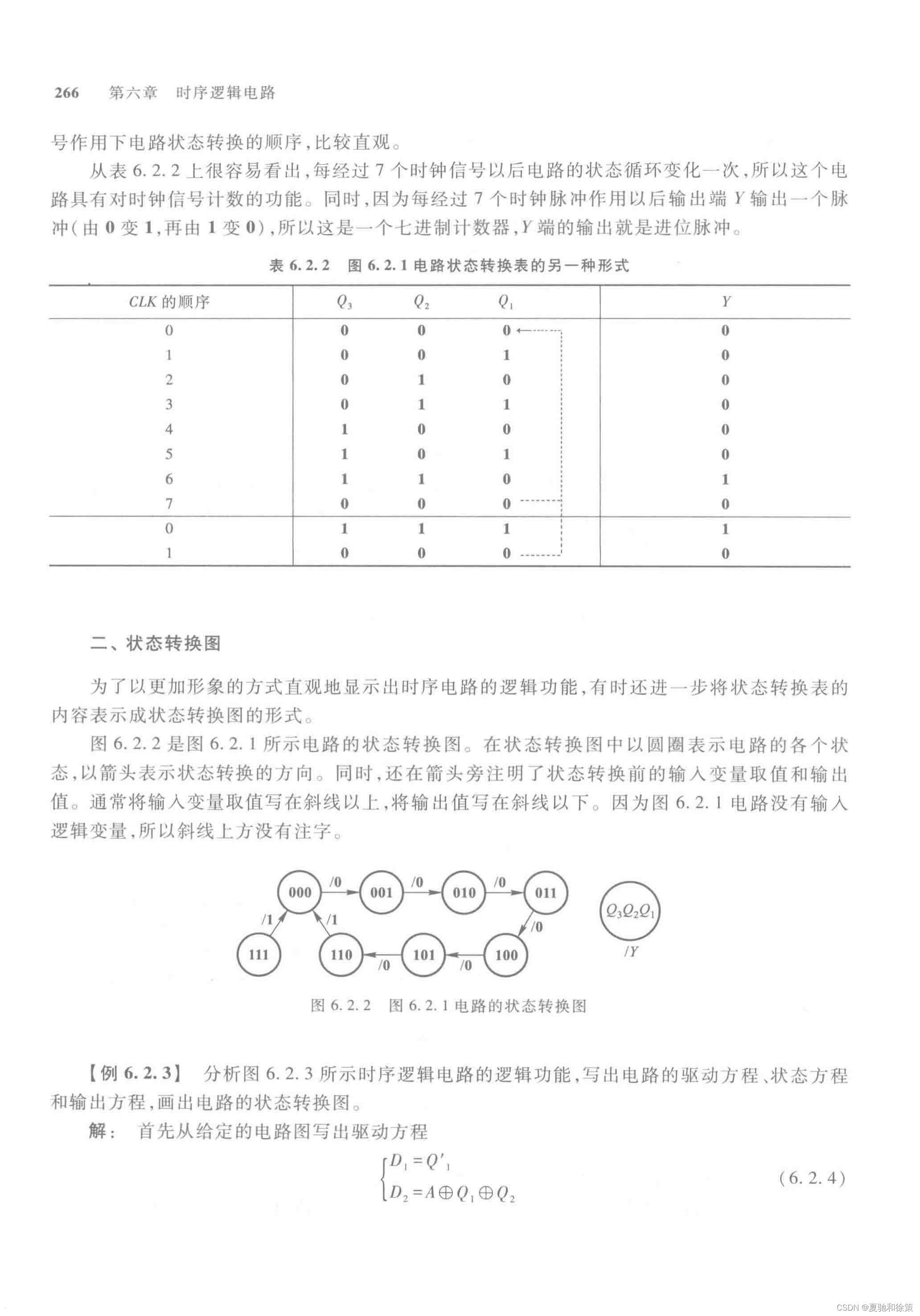

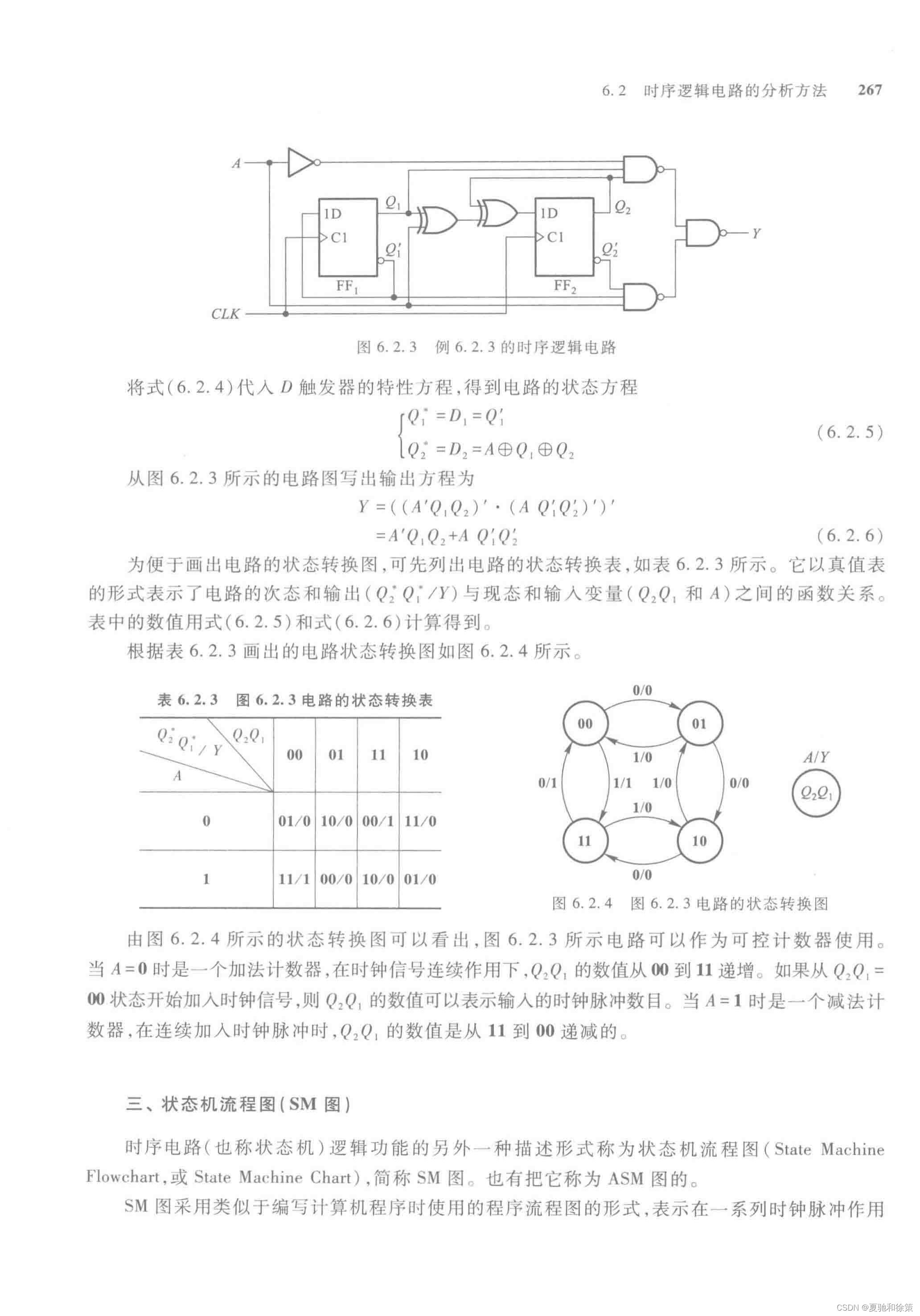

为了以更加形象的方式直观地显示出时序电路的逻辑功能,有时还进一步将状态转换表的内容表示成状态转换图的形式。图6.2.2是图6.2.1所示电路的状态转换图。在状态转换图中以圆圈表示电路的各个状态,以箭头表示状态转换的方向。同时,还在箭头旁注明状态转换前的输入变量取值和输出值。通常将输入变量取值写在斜线以上,将输出值写在斜线以下。因为图6.2.1电路没有输入逻辑变量,所以斜线上方没有注字。

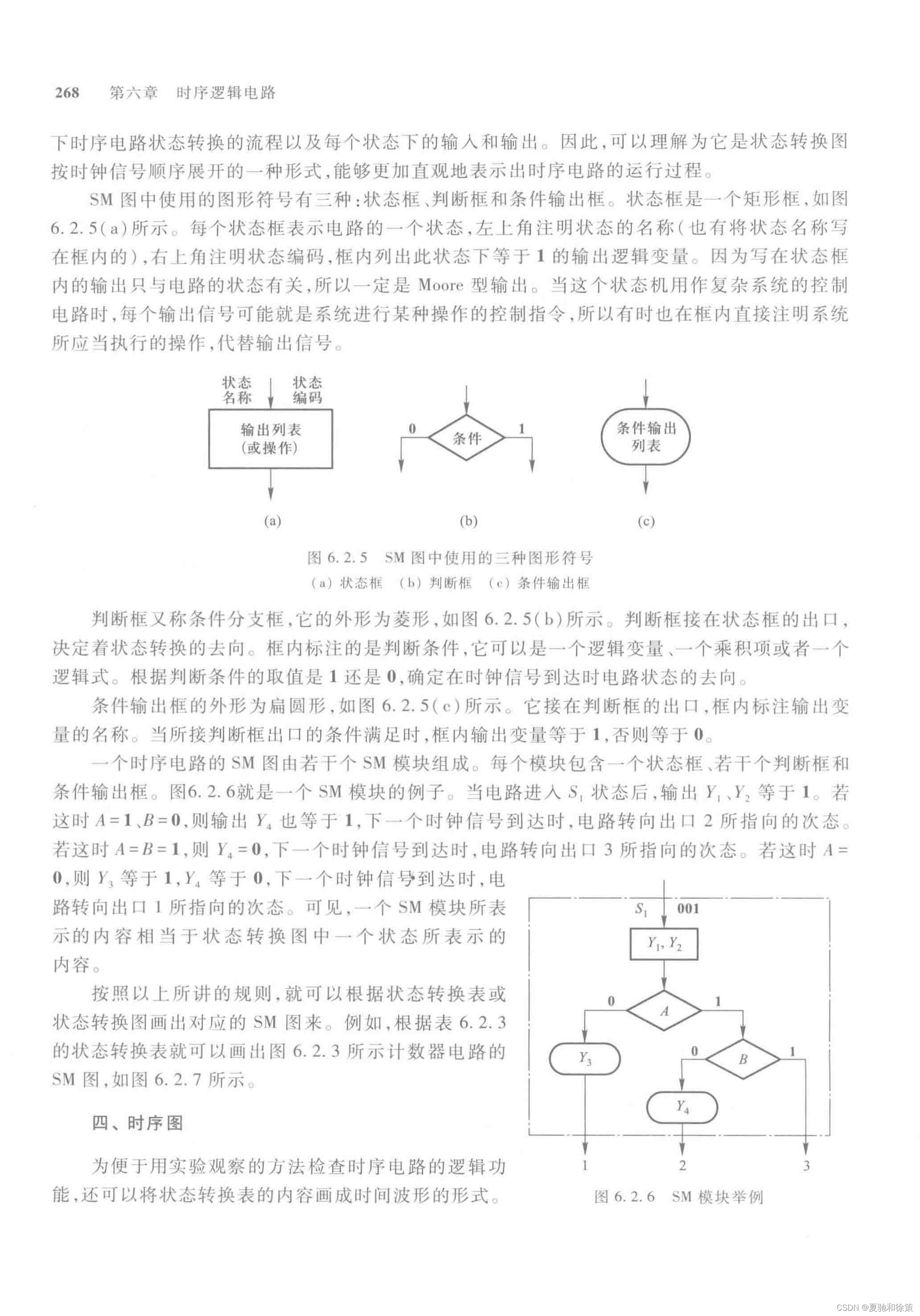

时序图

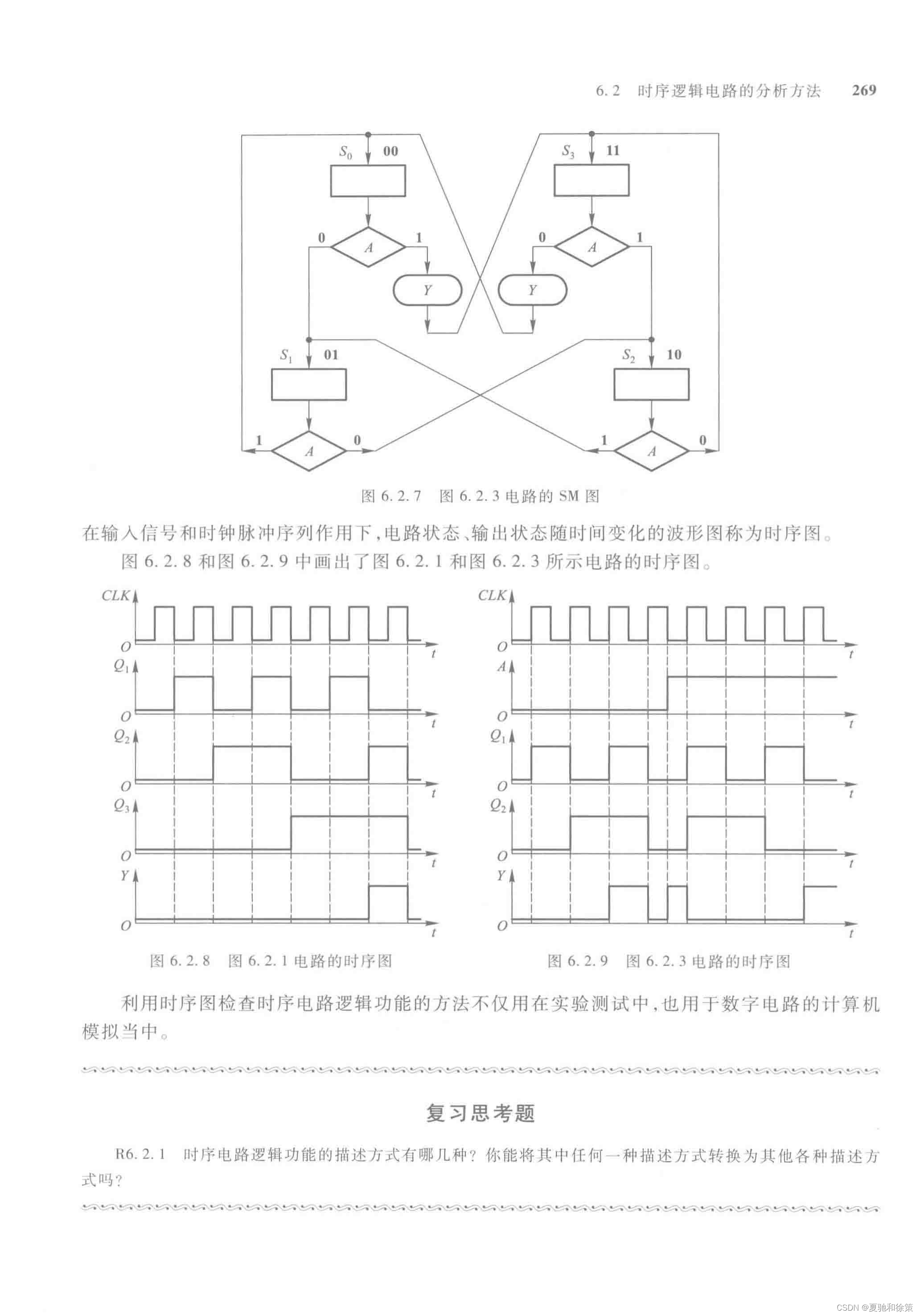

为便于用实验观察的方法检查时序电路的逻辑功能,还可以将状态转换表的内容画成时间波形的形式。图6.2.8和图6.2.9中画出了图6.2.1和图6.2.3所示电路的时序图。在输入信号和时钟脉冲序列作用下,电路状态、输出状态随时间变化的波形图称为时序图。

利用时序图检查时序电路逻辑功能的方法不仅用于实验测试中,也用于数字电路的计算机模拟当中。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?