AArch64 Exception model

privilege:当代软件被分成不同模块,不同模块访问系统或资源有不同的级别。例如kernel space和user space。

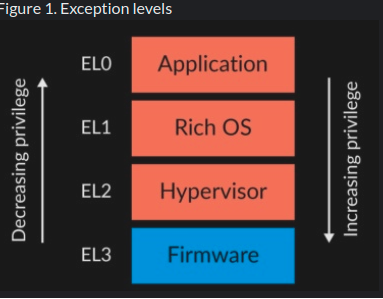

在Arm架构中,只有在cpu发出异常(exception)或从异常返回时,privilege level才变化。所以privileges level 基于Exception levels。

每个异常级别(exception level)被编号,编号越大级别越高。

通用规则:

EL0:运行用户应用代码

EL1:运行OS

EL2:被hypervisor使用

EL3:被底层固件(low-level firmware)和安全代码(security code)使用

特权类型:

1、memory system

2、访问cpu资源(processor resources)

memory system

Arm的架构使用虚拟内存,MMU(Memory Management Unit )使软件可以分配内存。这样可以灵活的配置read/write权限,可以隔离privileged和unprivileged的访问权限。

Register Access

在System registers中进行配置。

每个层都有各自的配置寄存器,高级别在特殊情况下可以访问低级别的,如下:

SCTLR_EL1 - Top level system control for EL0 and EL1

SCTLR_EL2 - Top level system control for EL2

SCTLR_EL3 - Top level system control for EL3

Execution and Security states

Execution states

Security state

Changing Execution state

Changing Security state

Implemented Exception levels and Execution states

EL0 and EL1 are the only Exception levels that must be implemented. EL2 and EL3 are optional.

Exception types

异常(Exception)是引起当前执行程序挂起,然后使操作这个异常的代码去执行的任何事件(event)。

在ArmV8中,中断被看作是外部异常。

Arm架构中分两种异种,synchronous exceptions and asynchronous exceptions。

Synchronous exceptions

这种异常是被当前执行的指令(instruction)引起的。意味这Synchronous exceptions和指令执行流(instruction execution streams)是同步的。

1、Synchronous exception可以由于当前将要执行的指令是无效的,这可能是由于在当前的ExceptionLevel是不允许执行的或者被禁用。

2、内存访问的时候也可以引起Synchronous exception。当访问的内存地址不对齐或者MMU权限不允许时,这可以在访问内存前产生exception。

3、Debug exceptions 也是synchronous exception。

ARM架构拥有发起异常的指令(exception-generating instructions):SVC, HVC, and SMC。

这些指令用来实施系统调用(system call),允许低特权请求高特权。

Asynchronous exceptions

这些异常是在外部产生的,异常可以在任何时候产生,不是在特定的execution streams产生的。

包括:

Physical interrupts

SError (System Error)

IRQ

FIQ

Virtual Interrupts

vSError (Virtual System Error)

vIRQ (Virtual IRQ)

vFIQ (Virtual FIQ)

Physical interrupts:用来响应PE(processing element)外部产生的信号。

Virtual Interrupts:可以是由于外部信号产生,也可以是由运行在EL2中的软件发起的。

IRQ and FIQ

IRQ和FIQ被外设中断来使用,在早期Arm架构中FIQ表示更快速更高优先级的中断,在Armv8-A和Armv9-A中,IRQ和FIQ相同。

IRQ和FIQ拥有独立的处理程序,经常用来实施Secure and Non-secure interrupts。

Non-maskable interrupts

2021年, Armv8.8-A和Armv9.3-A, 添加了Non-maskable interrupt (NMI) 支持.

NMI具有superpriority,即使PSTATE设置成不响应中断时,NMI也可以被获取。

SError

1、访问错误的内存的时候,发起的asynchronous abort

2、parity or Error Correction Code (ECC) checking on some RAMs

参考:

《TrustZone for Armv8-A》

Introduction to security:

Documentation – Arm Developer

AArch64 Exception model

Documentation – Arm Developer

Learn the architecture - Providing protection for complex software

Documentation – Arm Developer

Learn the architecture - AArch64 memory management

Documentation – Arm Developer

Learn the architecture - AArch64 memory model

Documentation – Arm Developer

Learn the architecture - TrustZone for AArch64

Documentation – Arm Developer

Realm Management Extension

Documentation – Arm Developer

6792

6792

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?