目录

1.1扇出操作

1.2差分对过孔间距调整

1.3差分线换层自动添加回流过孔

1.4多人协同操作

1.5导入pin delay

1.6走线导圆弧

1.1扇出操作

关于信号扇出有如下一些需要注意的点:

1、过孔扇出要考虑其间距,要求2个过孔之间保证能过一根信号线,防止过孔破坏地与电源的完整性;

2、2个过孔之间的中心间距建议在1mm以上(39.37mil),过孔大小的选择参考4.2章节—过孔添加与设置。

3、IC扇出优先选择外侧,有多排尽量调整地与电源的信号过孔扇出到管脚附近。 左右2边过孔应保持在同一水平线上,以方便内层布线。

4、电容扇出应保证其到供电管脚环路最小。过孔避免打到盘上,以免造成焊接不良,增加生产成本。一定要打盘中孔应将孔打在管脚边缘,不能打到中心位置。

5、BGA器件扇出时,过孔应打在2个焊盘对角线中心,并向四周扇出,中间十字通道禁示打过孔,保证其电源通道的载流能力。

6、BGA器件扇出时可考虑将前面2排孔拉出去一段距离,拉出去的过孔要与BGA中间的过孔尽量保持对齐,以方便BGA器件信号的出线。

7、一般可根据BGA器件间距,估算每层出线的数量,规划出所需设计板层。 一般1mm间距以上的,一个通道可以布2根信号线,1mm间距以下一个通道过1根信号。0.4mm间距一般只能进行HDI设计。

8、器件小于0805封装的,在与大铜皮相连时,建议采用十字连接处理。大面积铺铜的通孔焊盘一般采用十字连接处理,特别是对于多层板的GND网络通孔管脚, 防止焊接时散热过快导致焊接不良。

操作步骤说明:

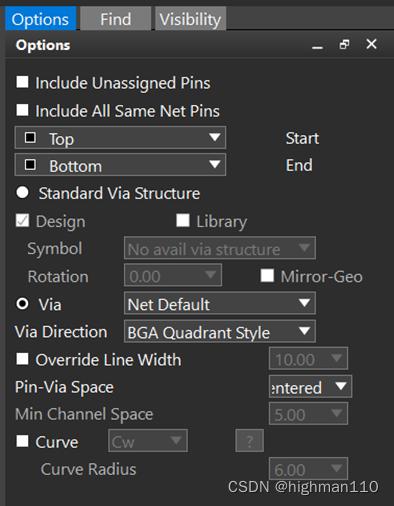

非BGA器件直接按要求手动打孔扇出即可,注意美观及不要使平面割裂。BGA器件可以使用route-create fanout进行自动打孔,先激活命令,然后在option面板设置参数:

Include Unassigned Pins:含义是扇出的时候,将没有网络的管脚也进行扇出,一般不用勾选,空网络的管脚不用进行扇出;

Include All Same Net Pins:含义是当单独对某一个管脚进行扇出时,将跟这个管脚网络一致的管脚也进行扇出,一般不用勾选;

Via:选择扇出所需要用到的过孔,过孔首先需要在物理规则里面添加好,不然这里没有可以选择的过孔;

Via Direction:过孔的方向朝向,一般选择BGA类型的风格,给BGA器件留出十字通道,方便散热;

Pin-Via Space:过孔到焊盘的间距,一般选择中心间距,将过孔扇出在周围四个焊盘的中心处。

设置好之后,在find面板,勾选symbol,然后点击要扇出的BGA器件,即可完成自动打孔扇出,之后再根据实际情况进行连线和过孔的调整。也可以在find面板勾选pin,然后点击某个pin就可以只针对这一个pin打孔,也可以鼠标框选部分pin,就可以对这部分pin打孔,当选择打孔方向为BGA风格时,单独打孔的位置是在pin的左上方。

1.2 差分对过孔间距调整

在差分走线命令下,右键-via pattern-spacing中可以设置间距,一般设置为8mil。

1.3差分线换层自动添加回流过孔

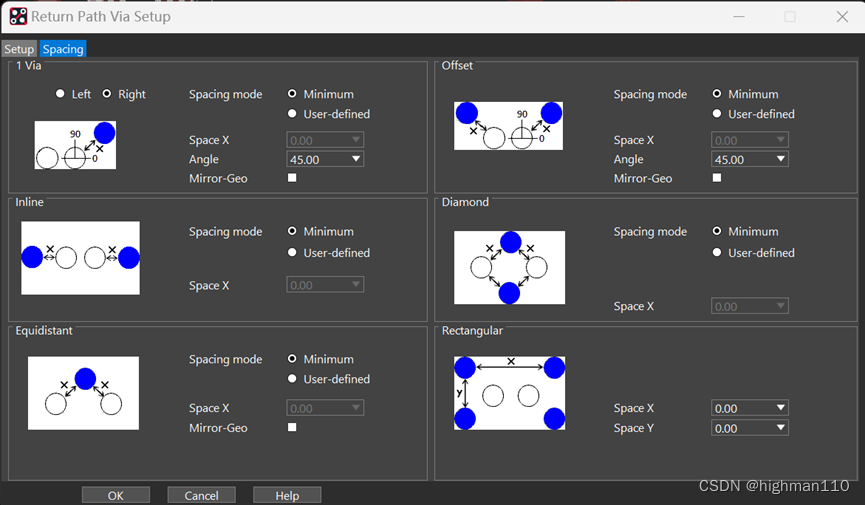

在差分对的走线命令下,右键-return path vias可以选择添加回流过孔的形式:

在settings里有如下几种回流孔添加形式,一般选择inline或者offset:

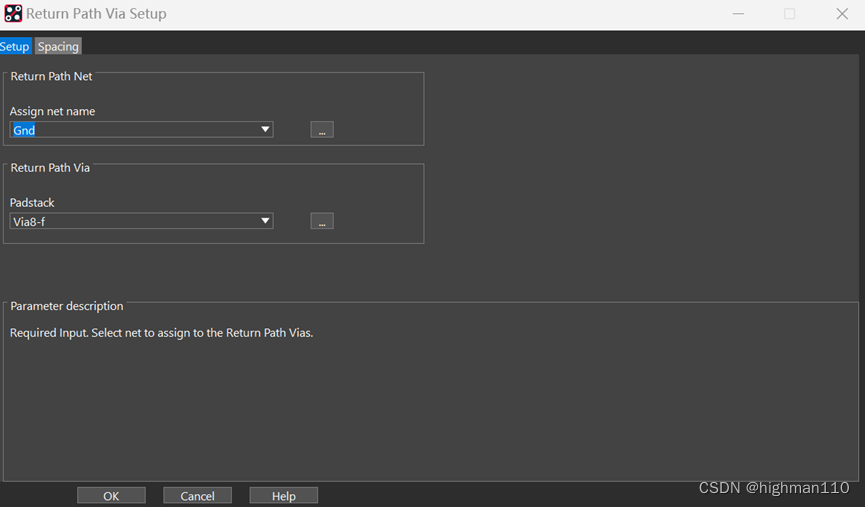

在setting-setup中设置过孔网络和选择过孔:

然后在打孔时双击就会自动添加上回流孔。

1.4 多人协同操作

当板子工作量较大时,可以采用多人协同操作,这里指的是布局完成后的布线操作协同。

操作步骤为:

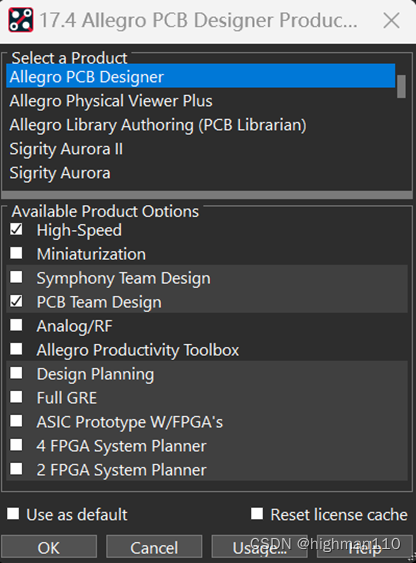

首先选择带有team design的产品组件,点击file-change editor,选择allegro PCB designer,勾选PCB team design即可。如果是16.6的版本,选择GXL产品,勾选team design即可:

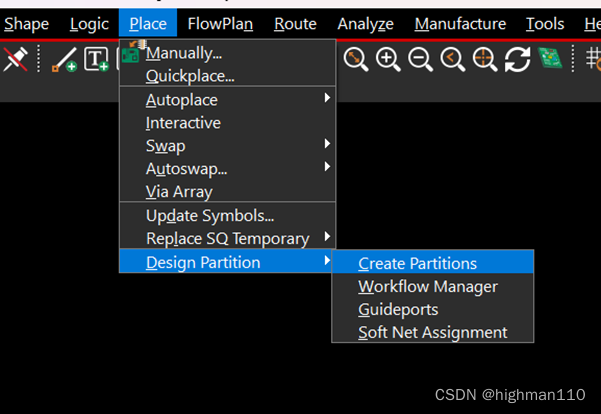

进入软件后点击place-design partition-create partition,然后在PCB中右键-add shape,在option面板设置画线转角为45度,圈出想要分出来的PCB部分,然后右键-done即可:

圈完之后会发现这个部分会有一个partition2的标识。

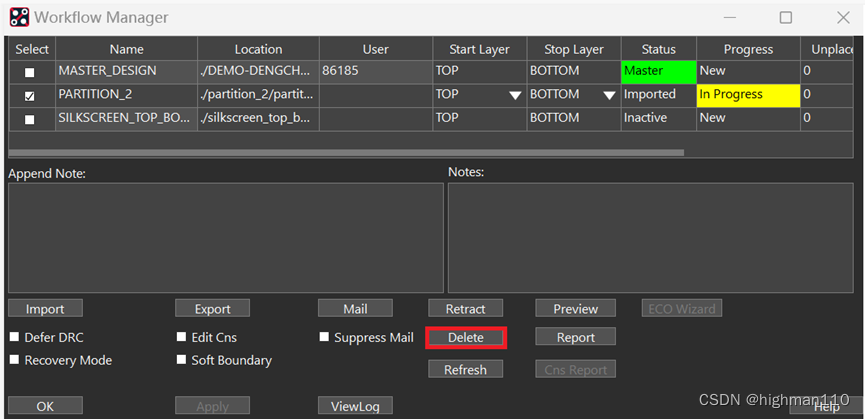

再点击place-design partition-workflow manager,勾选partition2,点击export,弹出没有连接电子邮件,直接点确定,不用管:

导出完成后可以发现这部分变成了灰色,在当前工程不可被编辑:

创建的partition文件在原工程目录下partition_2文件夹下,使用allegro打开此dpf文件,可以看到就只有圈出来的部分是可以编辑的。

Partition编辑完之后,需要与原工程合并。点击place-design partition-workflow manager,点击import即可完成导入合并,可以发现灰色部分变亮了:

然后删除刚刚画的圈,点击place-design partition-workflow manager,点击delete,即可删除:

然后删除刚刚画的圈,点击place-design partition-workflow manager,点击delete,即可删除:

1.5 导入pin delay

先打开约束模型设置:

勾选electrical option中的pin delay,apply-OK:

然后进入约束管理器的electrical-relative propagation delay,可以手动填入厂家给的数据,也可以导入,导入格式为csv表格:

文件格式如下:

然后点击file-import-pin delay,选择csv文件后,点击import即可完成导入。

1.6 走线导圆弧

一般高速信号需要将45度转角进行导圆弧处理。

按下图点击命令:

Find面板选中net,就可以对整个网络导圆弧,option面板默认即可,然后点击网路走线即可完成。

————————————————

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?