1 StrongARM锁存器的核心特点

-

零静态功耗:在不工作时(时钟低电平时)不消耗静态电流。

-

轨到轨输出(Rail-to-Rail Outputs):能够输出接近电源电压的完整摆幅。

-

低输入失调电压:输入失调电压主要由差分对(M1-M2)决定,其他晶体管的影响通过增益被抑制。

-

广泛应用于比较器、感知放大器(Sense Amplifier)和锁存器设计。

2 电路结构与原理

2.1 电路结构[1]

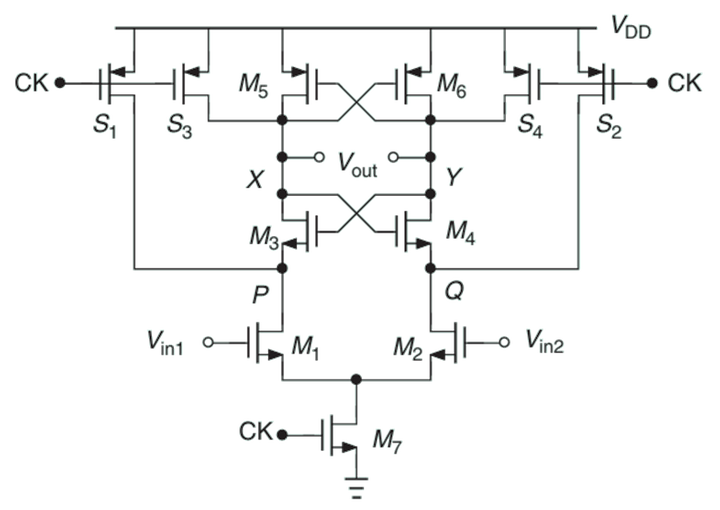

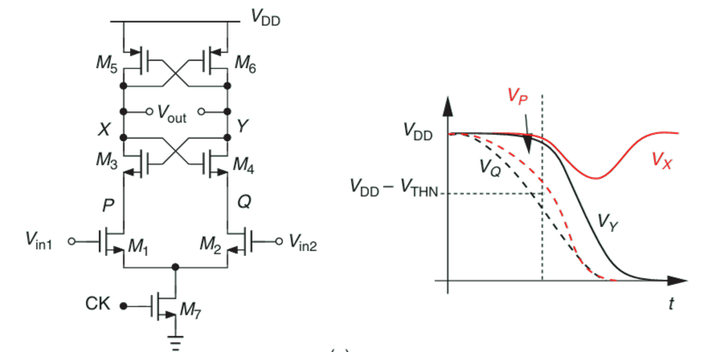

图1 StrongARM锁存器电路图

-

差分输入对(M1-M2):受时钟信号CK控制,提供差模信号放大。

-

交叉耦合NMOS对(M3-M4)和PMOS对(M5-M6):形成两级正反馈再生网络。

-

预充电开关(S1-S4):确保节点初始化,消除前次操作残留电荷。

-

尾电流源(M7):提供恒定电流,控制放大阶段电流分配。

2.2 工作原理

电路运行分为四个阶段,由时钟信号CK控制时序:

2.2.1 预充电阶段(Precharge Phase, CK低电平)

操作:

-

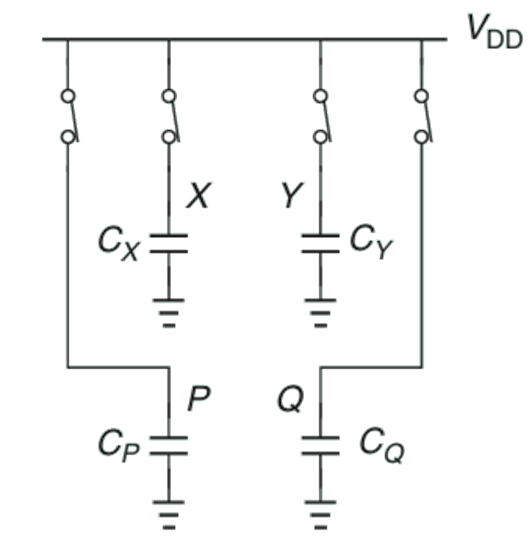

CK为低电平,S1-S4开关全部导通,将P、Q、X、Y四个节点强制上拉至VDD(P、Q处存在寄生电容,X、Y处存在寄生电容和负载电容)。

-

M1、M2关断,差分对无电流。

-

M3-M6因栅极、源极或漏极为VDD(VGS=0),处于关断状态。

-

图1简化为图2

关键作用:

-

节点均等化:P和Q节点的电位被强制设置为VDD,消除前次操作残留的电荷不平衡(动态失调电压主要来源)。

-

PMOS关断保证:X和Y预充电至VDD,确保M5和M6的栅源电压VGS=0,处于关闭状态。

图2 预充电阶段

2.2.2 放大阶段(Amplification Phase, CK变高电平初始阶段)

操作:

-

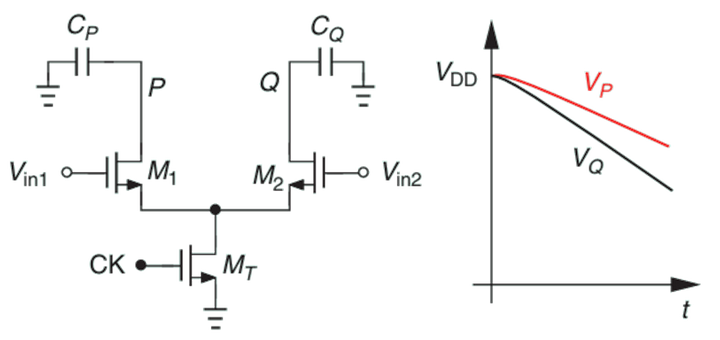

CK变高电平,S1-S4关断,停止预充电;M1-M2和M7导通,尾电流 IT 流经M1-M2。

-

输入差模电压 ΔVin=Vin1−Vin2 引起电流差: (1)ΔI=gm12⋅ΔVin

其中 gm12 是M1-M2的跨导,该电流差从P、Q节点对电容(CP、CQ)放电,建立放大电压差 ΔVPQ=VP−VQ , ΔVPQ 可能会超过 ΔVin,所以这个阶段被称为放大阶段,如图3所示。

关键过程:

-

M3-M4此时仍关断(P、Q尚未降至 VDD−VTHN ),电路处于线性放大模式。

-

尾电流 IT 几乎不变,小信号模型 |VP−VQ|≈(gm1,2|Vin1−Vin2|/CP,Q)tamp

其中 CP,Q=CP=CQ

-

放大阶段持续到 、VP、VQ 下降到 VDD−VTHN ,即进入下一阶段(NMOS交叉导通阶段)。

其中 ICM 为共模放电电流。

-

电压增益 Av :

现象:

-

P、Q电压线性下降,电压差呈线性增长。

-

X、Y节点仍保持VDD(因S3-S4关闭,电容CX、CY未放电)。

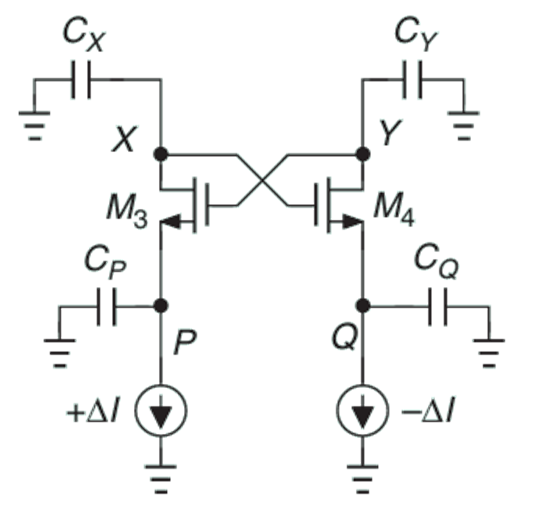

图3 放大阶段

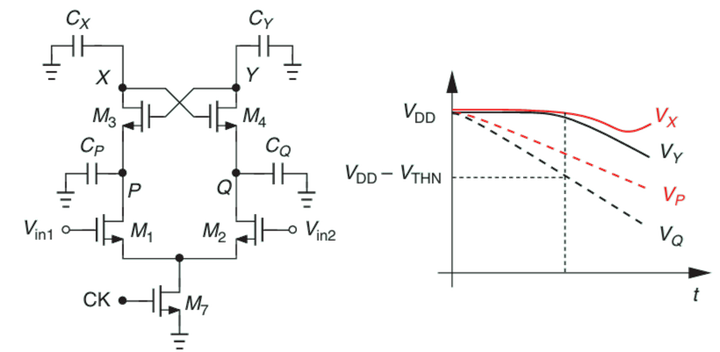

2.2.3 NMOS交叉导通阶段(M3-M4开启,再生阶段①)

-

触发条件:当P、Q节点电压降至 VDD−VTHN,M3-M4( VGS=VDD−VP/VQ≥VTHN )超过阈值,开始导通。

-

操作机制:

-

M3-M4的导通形成第一级正反馈:

-

假设初始 VP<VQ → M3的栅-漏电压比M4的栅-漏电压更高,M3导通电流更大,X点放电更快,X点电压降低 → M4的栅极电位更低,M4导通电流变小,Y点放电减速。

-

该正反馈加速 ΔVPQ的增长,放大效果进一步增强。

-

电路如图4所示,等效电路如图5所示。

图4 NMOS交叉导通阶段

图5 NMOS交叉导通阶段等效电路

-

再生时间常数:

由图5可知,P、Q、X、Y四节点的电流情况:

其中 +ΔI 代表M1的小信号电流, −ΔI代表M2的小信号电流 。

X和Y点公式相减得

P点和Q点公式分别积分后相加得

将此公式带入上个公式,我们得到

这是关于(VX−VY) 一阶线性微分方程,可知

其中,为再生时间常数, CX,Y 为负载电容,CP,Q为节点电容。因 CX,Y≫CP,Q,此阶段NMOS再生受限,但为后续PMOS再生提供初始电压差。

2.2.4 PMOS交叉导通阶段(M5-M6开启,再生阶段②)

-

触发条件:

-

X、Y节点电压降至 VDD−|VTHP| (PMOS阈值电压),PMOS管M5-M6的栅源电压 VSG=VDD−VX≥|VTHP| ,M5-M6开始导通。

-

操作机制:

-

正反馈加速锁定:

-

当X点因交叉耦合放电更低(例如 VX<VY ),M6的栅极接低电平X,导通更强,上拉Y点至VDD → Y点高电平使M5的栅极电位升高,导通更弱,X点进一步被拉低至GND。

-

轨到轨摆幅:最终X=0V,Y=VDD(或反向),完成信号锁存。

-

输出特性:

-

由于PMOS对M5-M6的强正反馈,输出在极短时间内被锁定为全摆幅(0V至VDD)。

-

零静态功耗:锁定后,M3-M4或M5-M6中总有一侧完全关断(M4-M5切断或者M3-M6切断),切断VDD到GND的直流通路。

图5 PMOS交叉导通阶段

3 输出和功耗

3.1 输出

StrongARM 锁存器后接 RS 锁存器(Reset-Set 锁存器)(如图6所示)的核心目的是为动态比较/锁存过程提供一个稳定的数字输出,弥补 StrongARM 锁存器在时序和信号完整性上的局限性。

图6 StrongARM 锁存器后接RS锁存器

StrongARM 锁存器没有加上RS 锁存器:

-

当时钟信号 CK 为高电平时,StrongARM 完成放大和再生,输出有效(如 X=0,Y=VDD)。

-

当 CK 变低电平时,StrongARM 进入预充电阶段,X 和 Y 被强制拉高到 VDD(此时输出失效)。

StrongARM 锁存器加上RS 锁存器:

阶段 1:StrongARM 的有效输出阶段(CK 高电平)

-

StrongARM 输出:假设再生后 X=0、Y=VDD(表示逻辑 "1")。

-

RS 锁存器输入:此时 X 的低电平置位 SET 输入,Y 的高电平复位 RESET 输入。

-

RS 锁存器状态:Q 输出高电平,\overline{Q} 输出低电平。

阶段 2:StrongARM 进入预充电阶段(CK 低电平)

-

StrongARM 输出失效:X 和 Y 被预充电到 VDD(输出均为高电平,状态失效)。

-

RS 锁存器维持:无论 SET 和 RESET 如何变化(此时均为高电平),RS 锁存器保持前一刻的状态(Q 仍为高电平)。

3.2 功耗

StrongARM锁存器功耗主要来自节点电容充放电

其中,2代表P点和Q点电容几乎完全放电。

4 失调电压

在感知放大器或比较其中,输入失调电压必须足够小。失调电压主要来自M1-M6和S1-S4。开关S1-S4导通过程中M3-M6截止状态,对输入失调电压贡献为0。开关S1-S4断开过程中,M3和M4之间的失陪引起的失调电压等效到输入端时,需要先除以一个大约为 Av≈4 的因子(第二阶段的增益);M5和M6之间的失陪引起的失调电压等效到输入端时,需要除以一个大约为10的因子,这是因为考虑到了M5、M6管只有在最后两个阶段的时候才导通。因此,M3-M6管的等效输入失调电压都不是很大,M1和M2起主要作用,因此我们需要重点关注并消除M1、M2的失调电压。

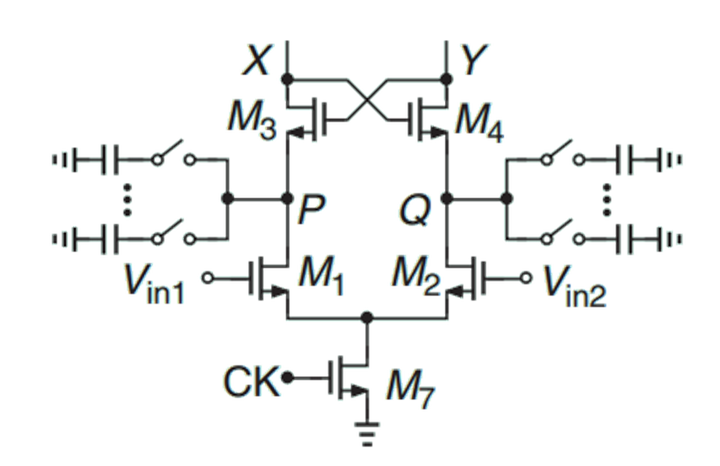

我们知道电路在放大阶段,增益通过P、Q点的电容放电实现。如果 CP 和 CQ 不相等,可以消除失调电压。因此,我们在P、Q点加上可编程的电容调整其放电速度。

首先,我们计算P、Q点电压

两者相减,我们得到

其中 和输入信号无关,是失调电压,随着时间累积。当 CP=CQ 时,该项为0;当 CP≠CQ 时,该项可以用来消除随机失调电压。

由公式(2)可知,放大阶段的持续时间为 (CP,Q/ICM)VTHN ,这里 CP≠CQ , CP,Q≈(CP+CQ)/2 。因此,内在失调电压为 VTHN(CP/CQ−CQ/CP)/2 。

图7 P、Q点可编程电容消除失调电压

为了降低失调电压(从30mV降低到1mV),大量小单位电容接到P、Q点,不过这会降低电路速度以及增加电路功耗[2,3]。

5 噪声

5.1 噪声来源与计算

和失调电压类似,噪声主要来自M1和M2,以及S1和S2的 kT/C 噪声,其余的晶体管起作用时增益已经很大,增效到输入端的值可以忽略。

图3为放大阶段电路,其等效电路是一个积分器,产生输出噪声(来自M1和M2噪声),输出电压的变量和时间相关

公式(2)给出了持续时间,因此,最终由M1和M2产生的输出噪声为

总的积分噪声为

其中, Av来自公式(3),,公式中方括号内的第一项是M1和M2贡献的噪声,第二项是开关贡献的噪声,通常第一项是第二项的4到8倍。

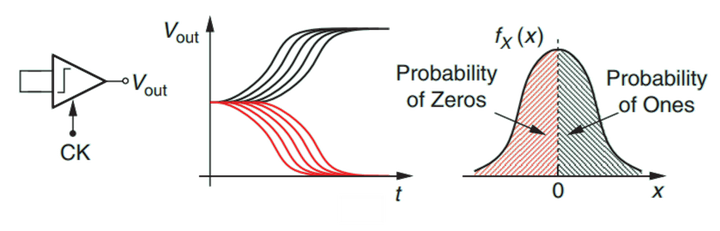

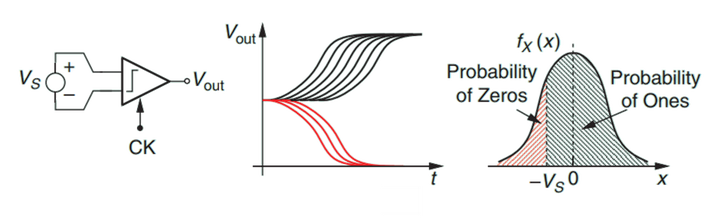

5.2 噪声分布

比较器并不能直接得到输出噪声与增益,因此需要进行仿真。假设比较器的输入失调电压为0,差分输入电压为0,然后给其时钟信号,在几次时钟信号之后,电路从亚稳态中摆脱出来了,因为电路中存在高斯噪声。此时,比较器输出高电平或者低电平的概率是相等的,如图8所示。

图8 有噪声的比较器零输入时输出情况

接下来,我们给比较器加上差模电压Vs(几mV),然后重复上面的仿真过程,结果如图9所示。

图9 有噪声的比较器输入为Vs时输出情况

比较器输入噪声小于-Vs时,输出才是低电平。

如果进行大量周期的仿真,我们可以预测低电平和高电平的数量 n0和 n1。

Vs需要足够大,保证n0/n1比1小很多;但也不能太大,使得 n0 或者 n1 太小,这样的话统计就没意义。

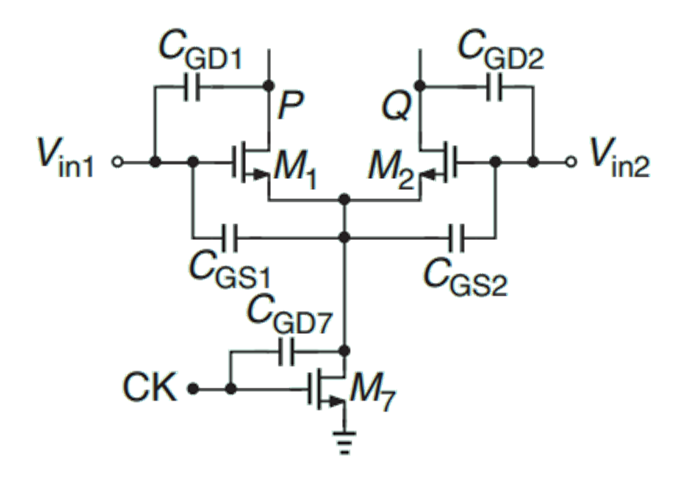

5.3 回踢噪声与电源瞬态电流

StrongARM结构的比较器会从输入端或者电源获得大量的瞬态电流,如果并联的比较器较多(例如flash ADC),那么瞬态电流会很大,带来问题。

图10 回踢噪声路径

来自输入端的回踢噪声产生机制很多,包括差模和共模成分。差模成分: VP 和 VQ 以不同的速率下降至0时,并通过 CGD1 和 CGD2 耦合到输入端。当M1,M2进入线性区后,它们的栅漏电压随之增加,导致这种现象会变得更为明显。共模成分:M7导通时,通过 CGS1 和 CGS2 抽取电流;M7截止后,时钟信号CK也可以通过 CGD7(≈CGS7) 和CGS1、 CGS2的路径耦合到输入端。

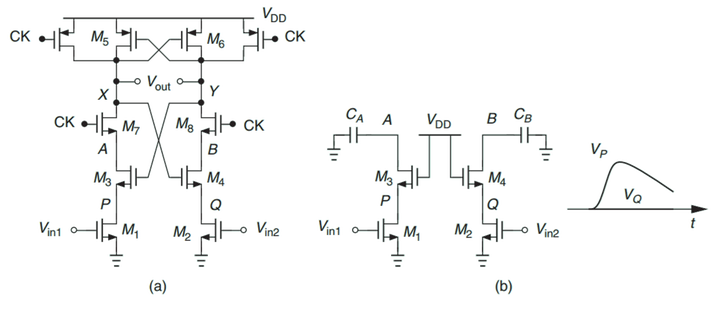

图11 (a)低回踢噪声电路 (b)预充电阶段

因为 CGS>CGD ,所以要避免时钟信号CK耦合到源端,如图11(a)所示,通过M7、M8进行控制。但是这种方法导致了更高的等效输入失调电压,因为此时M1、M2在第二阶段时工作在线性区(增益变小)。这个问题可以通过增加M3、M4、M7、M8的宽度来避免。但是图11(b)所示,在预充电阶段,A、B的寄生电容放电很慢,导致 VP 和 VQ 差值较大,从而产生大的动态失调。

电源的瞬态电流来自于预充电过程中S1-S4从VDD抽取的电流,如图2所示。如果CK下降很快,S1-S4中的三个会暂时地进入饱和区(另外一个会进入线性区,因为它的漏极电压等于VDD),从VDD抽取大量的瞬态电流。低功耗,但需要从VDD抽取大瞬时电流,说明产生了低电源阻抗。

参考文献:

[1]Razavi B. The StrongARM latch [a circuit for all seasons][J]. IEEE Solid-State Circuits Magazine, 2015, 7(2): 12-17.Razavi B. The StrongARM latch [a circuit for all seasons][J]. IEEE Solid-State Circuits Magazine, 2015, 7(2): 12-17.

[2] Nuzzo P , De Bernardinis F , Terreni P ,et al.Noise Analysis of Regenerative Comparators for Reconfigurable ADC Architectures[J].IEEE Transactions on Circuits & Systems I Regular Papers, 2008, 55(6):1441-1454.Nuzzo P , De Bernardinis F , Terreni P ,et al.Noise Analysis of Regenerative Comparators for Reconfigurable ADC Architectures[J].IEEE Transactions on Circuits & Systems I Regular Papers, 2008, 55(6):1441-1454.

[3] Lee M J E , Dally W J .Low-power area-efficient high-speed I/O circuit techniques[J].IEEE J. Solid-State Circuits, 2000, 35(11):1591-1599.Lee M J E , Dally W J .Low-power area-efficient high-speed I/O circuit techniques[J].IEEE J. Solid-State Circuits, 2000, 35(11):1591-1599.

7667

7667

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?