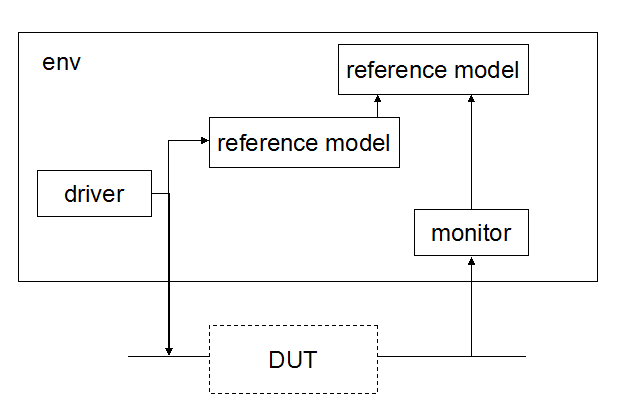

1.首先看下面的结构吧:

这个结构虽然不是一个严格满足官方规范的架构,但它真的可以跑.

1). driver:产生最原始的data,发送给两部分。一个是DUT,另一个是reference model。

2) reference model:是一个和DUT逻辑上相同的模块,可以sv,也可以通过DPI实现。我遇到的问题是,如果reference model和DUT是一个人写的,那么纯粹就是把同样的逻辑写了两遍,要错一起错,感觉意义不大了。你们是怎么处理的呢?

3)DUT:就是DUT。

4)monitor:是把DUT的输出给scoreboard作比较。严格说,monitor 和 DUT 的箭头应该是双向的。

5)scoreboard:比较reference model的输出和monitor的输出是否相同。

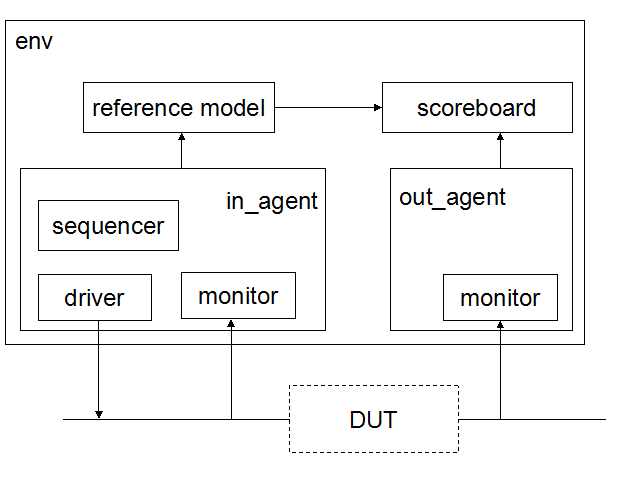

2:虽然上面的也能跑,但是明显不如官方的标准逼格高。小的还看不出来,但是大了,结构会很乱,扩展性rambling;接口的可移植性想都不要想;如果把这个给一个平时严格按照要求做的engineer,他会疯掉,简直没法交流。

所以比较基础的标准结构应该想下面一样:

这样就把sequencer,agent的概念加进去了,更有了hierarchy的感觉。

2761

2761

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?