当前各类的智能应用场景对芯片端的异构算力提供能力提出了越来越高的要求,芯片原厂越来越倾向于将CPU,DSP,GPU,VPU,NPU,ASIC等等异构单元集成在一颗硅片上。FPU作为传统CPU内部的用于浮点算例的集成单元,也可以划归为异构算例的一个组成部分,下面通过一个实验性质的FPU实现模块,简单分析一下FPU对IEEE754标准的实现方式。

安装gtkwave,iverilog:

获取源码:

https://gitee.com/tugouxp/hardware-lab.git

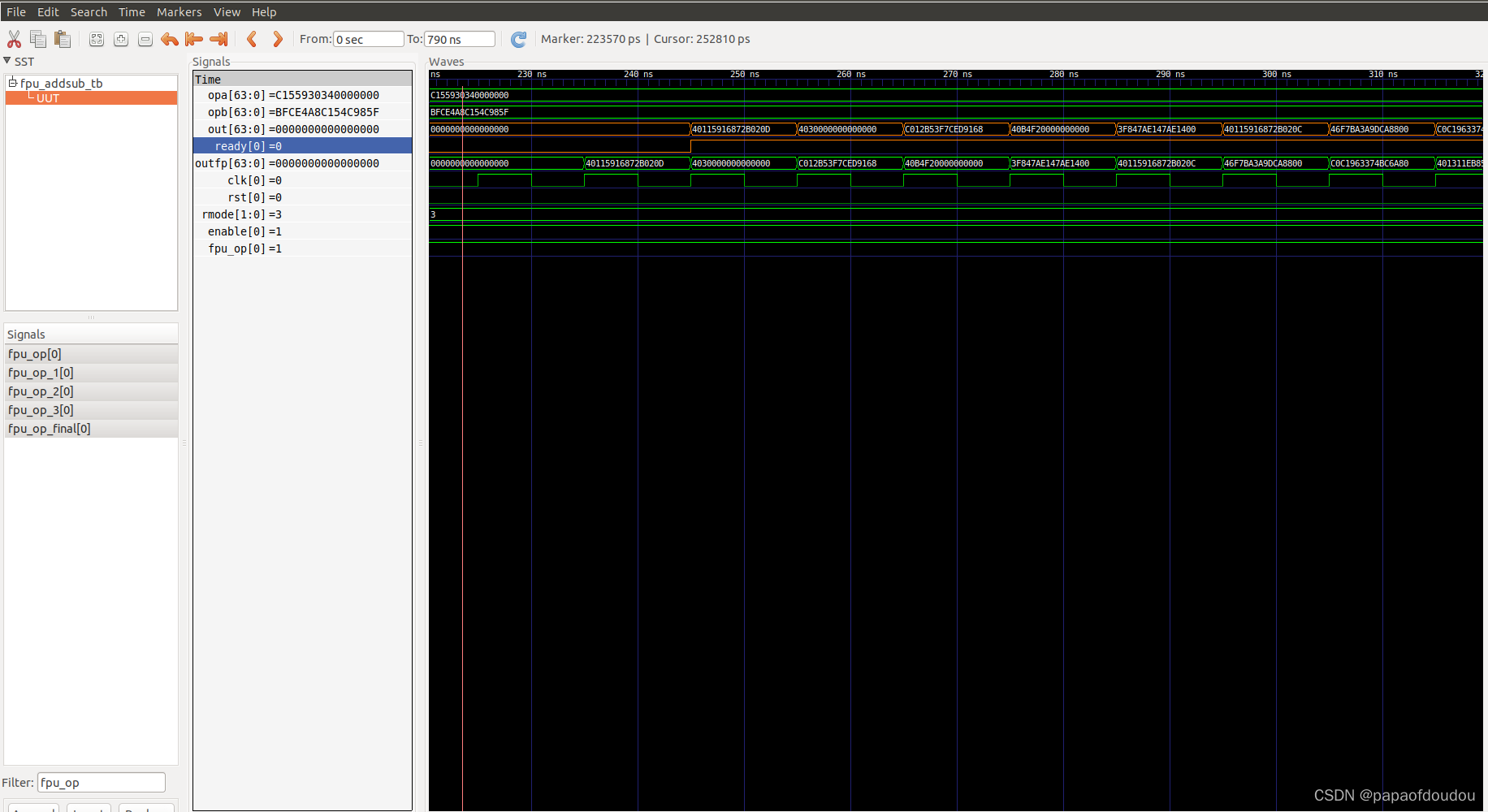

源码中有三个testbench文件,分别为fpu_TB.v,fpu_mul_TB.v,fpu_addsub_TB.v,仿真只能一个一个进行,不能同时将三个文件放在一起综合,否则,有可能从gtkwave看到的波形和实际波形并不match.

比如,我们要仿真fpu_addsub_TB.v,就先把另外两个删掉,否则根据构建写法,所有.v源码会参与编译。

接着执行make&&make sim

IEEE754的分析

浮点,并不意味着IEEE754定义中的符号位,阶码部分,尾数部分的位宽是可变的,而是说,最终表示的数字,小数点左边的有效数字浮动范围远远大于定点数字,看下图,你可以闭着眼睛想象一下Exponent域变化时的样子,就是因为最终表示的数字,小数点的位置会随着Exponent的变化而调整移动,所以才叫做浮点。

浮点表示的范围非常的广泛,下面的例子可以说明:

#include <stdio.h>

#include <stdio.h>

#include <stdint.h>

void test_fun(uint32_t num)

{

float *p = (float*)#

printf("%s line %d, num %d, *p=%f\n", __func__, __LINE__, num, *p);

return;

}

int main(void)

{

test_fun(0x40c00000);

test_fun(0x40e00000);

test_fun(0x40f00000);

test_fun(0x40ff0000);

test_fun(0x40ffffff);

test_fun(0x70c00000);

test_fun(0x78c00000);

test_fun(0x7dc00000);

test_fun(0x7f400000);

test_fun(0x7f7f0000);

test_fun(0x7fc00000);

return 0;

}运行结果:

总结:

所以,所谓的FPU,就是一个能够处理IEEE754数据格式的硬件加速单元模块,除了IEEE754标准,工业界也有其它一些实现标准,只是没有推广开来,仅仅在一些小范围内使用。

3704

3704

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?