Nand Flash简介

简介

相当于pc机的硬盘,保存系统运行所必须的操作系统、应用程序、用户数据以及运行过程中产生的一系列数据。掉电后数据仍可保存。

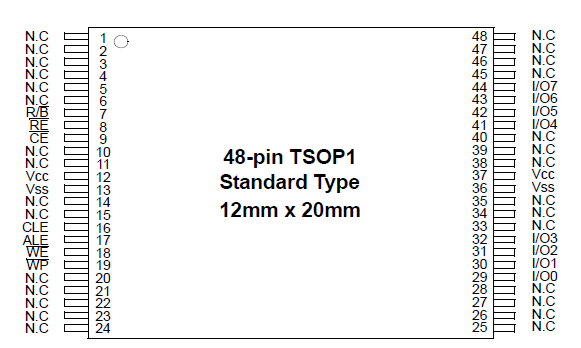

贴上Tiny6410所用的Nand Flash芯片的引脚配置图和信息,以后会用。

引脚

引脚配置图:

引脚描述:

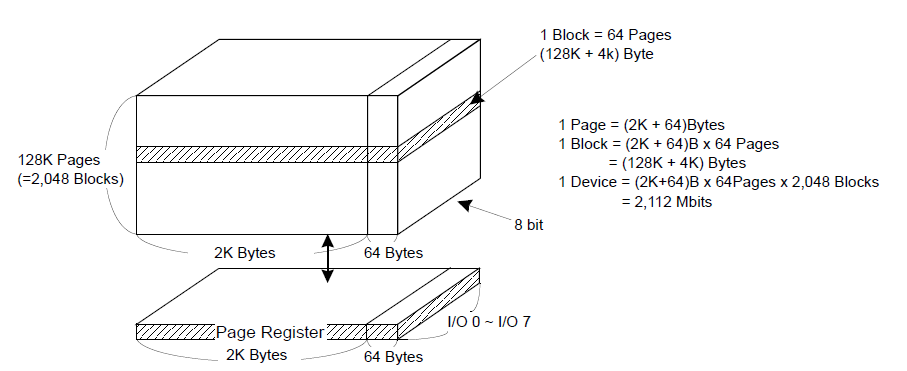

基本结构图

由图中可以看到,一页有2KB的空间以及64*8bit的额外空间(韦东山老师的视频教程里称之为OOB,不在Nand Flash的编址范围之内,一般情况下不用)。可以看出,一页有2112*8个cell(一个cell为1bit),一个block有64页,一个Device Register有2K个块(block)。

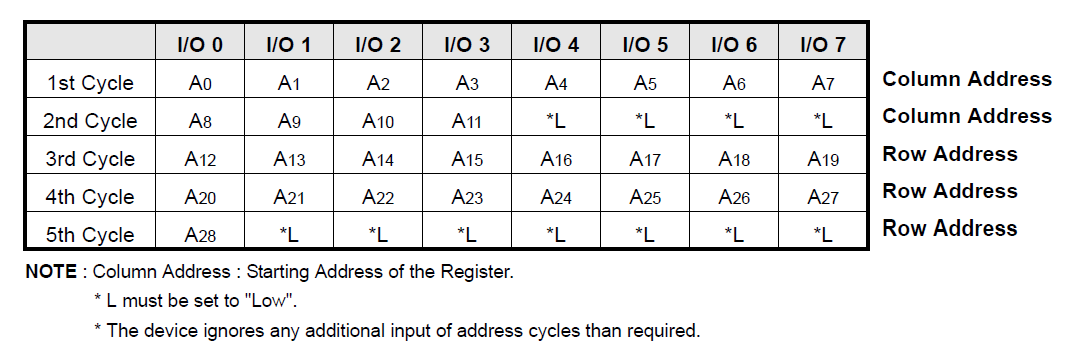

本文介绍了Nand Flash的基本结构和功能,特别关注了S3C6410微处理器如何通过Nand Flash Controller进行数据访问。详细阐述了Nand Flash的硬件连接、访问方式,包括命令的发送、地址的指定和数据的传输,并提到了NFCMMD、NFADDR和NFDATA寄存器的角色。文章以 Tiny6410 的Nand Flash控制器为例,解析了其独特的寻址机制,并预告了后续的代码分析。

本文介绍了Nand Flash的基本结构和功能,特别关注了S3C6410微处理器如何通过Nand Flash Controller进行数据访问。详细阐述了Nand Flash的硬件连接、访问方式,包括命令的发送、地址的指定和数据的传输,并提到了NFCMMD、NFADDR和NFDATA寄存器的角色。文章以 Tiny6410 的Nand Flash控制器为例,解析了其独特的寻址机制,并预告了后续的代码分析。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

754

754

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?