前面章节内容针对ARM内核和ARM内核汇编完成了ARM处理器最基础内容的学习,从本章开始我们针对集合ARM内核的SOC片上系统展开学习。片上系统设计的主要是针对各种外界硬件设备的驱动开发工作,关于这部分内容各个SOC芯片外部设备和接口协议大同小异,可以做到一通百通。当然,随着技术的发展和嵌入式开发人员的逐渐庞大,现在常见的外部设备硬件驱动开发工作基本上直接拿来现成代码做简单修改即可。对于网卡、ISP这种复杂类型的外部设备,需要一些负责相关业务的开发人员进行维护。

SOC涉及外部设备主要包含时钟树、串口、DRAM、I2C、SPI、CAN、USB、PCIE、DMA、Nandflash、网卡等。

1. 系统时钟体系

1.1. 时钟源

外部时钟源分两种,晶振OSC或者外部时钟EXTCLK,由om3-2选择具体输入哪个时钟源信息表:

1.2. 频率控制

经过选定开关OM选定以后的输入时钟MPLL_IN有三个去向MPLL、UPLL、USBCNTL。其中USBCNTL这些控制模块一开始控制室中都是来自选定后的时钟,这些控制模块给定时钟以后,我们才能进行后期复杂锁相环和分频器寄存器配置,产生需要的时钟。UPLL环和MPLL都包含了P/M/S配置用来实现频率倍增,DIVN分频器则实现频率成倍降低的功能。确定好频率控制以后,剩下的内容是如何分频,如何启用时钟停止时钟,锁相环配置等等。

| 输入时钟 | MPLL | FCLK | HCLK | 内存控制器,中断控制器,nand控制器,tic控制器等,系统内核920T,DMA控制器,USB控制器(也可UCLK) |

| PCLK | 基本外设RTC,UART,spi等外设,USB设备(也可UCLK) | |||

| 只供给系统内核, | ||||

| USB PLL | UCLK | USB主机时钟,usb设备时钟 | ||

1.3. 配置时序

启动晶振时钟序列图给出了启动过程的拉起流程, 根据芯片是时钟启动流程原理确定寄存器配置流程。

- 正常上点以后,晶振开始逐渐会振动,等待nRESET信号拉高确定具体的时间使用情况。

- FCLK提供给芯片的时钟稳定在晶振初始时钟

- 根据OM设置,nRESET拉高以后输出相应的选择时钟

- 设置PLL锁相环锁定时间,这个时间主要用于软件设置PLL倍频寄存器以后,给锁相环正常输出稳定频率的反映时间

- 结束锁定时间以后开始按照软件设置的最新频率输出给CPU工作频率

根据流程确定配置时钟需要的寄存器如下:

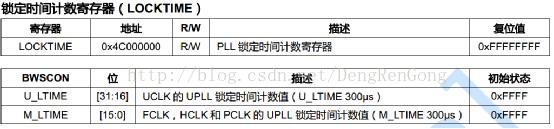

PLL的锁定时间,一般设置小一点查询是否锁定成功就好

通过锁相环控制器设定MPS比例,可以获取不同的MCLK或者UCLK,配置过程计算公式:

/* 设置MPLLCON(0x4C000004) = (92<<12)|(1<<4)|(1<<0)

/* 设置MPLLCON(0x4C000004) = (92<<12)|(1<<4)|(1<<0)

* m = MDIV+8 = 92+8=100

* p = PDIV+2 = 1+2 = 3

* s = SDIV = 1

* FCLK = 2*m*Fin/(p*2^s) = 2*100*12/(3*2^1)=400M

*/

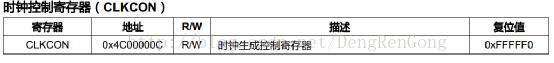

通过这个寄存器进行时钟的使能与切断,一般进行功耗控制的时候需要关闭一些不需要的模块。

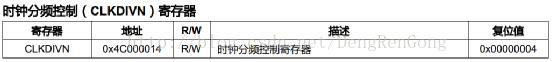

该寄存器确认以一种什么样的比例将FCLK分频为HCLK和PCLK

注意:

2. 汇编时钟

/* 目标设置MPLL, FCLK : HCLK : PCLK = 400m : 100m : 50m */

/* 1. LOCKTIME(0x4C000000) = 0xFFFFFFFF */

ldr r0, =0x4C000000

ldr r1, =0xFFFFFFFF

str r1, [r0]

/* 2. CLKDIVN(0x4C000014) = 0X5, tFCLK:tHCLK:tPCLK = 1:4:8 */

ldr r0, =0x4C000014

ldr r1, =0x5

str r1, [r0]

/* 3. 设置CPU工作于异步模式 */

mrc p15,0,r0,c1,c0,0

orr r0,r0,#0xc0000000 //R1_nF:OR:R1_iA

mcr p15,0,r0,c1,c0,0

/* 4. 设置MPLLCON(0x4C000004) = (92<<12)|(1<<4)|(1<<0)

* m = MDIV+8 = 92+8=100

* p = PDIV+2 = 1+2 = 3

* s = SDIV = 1

* FCLK = 2*m*Fin/(p*2^s) = 2*100*12/(3*2^1)=400M

*/

ldr r0, =0x4C000004

ldr r1, =(92<<12)|(1<<4)|(1<<0)

str r1, [r0]

/* 一旦设置PLL, 就会锁定lock time直到PLL输出稳定

* 锁定期间CPU不工作,结束后CPU工作于新的频率FCLK

*/

738

738

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?