转自:http://www.51hei.com/bbs/dpj-40117-1.html

一、引言

ARM公司在2009年初发布了其嵌入式处理器系列中最小型、最低功耗的CortexM0处理器。CortexM0低功耗、高性能与极精简程序代码的特性,能应用于各种微控制器(MCU)中,并可让研发业者以8位的价位创造32位的效能,并进一步将传统的8位和16位的处理器推进至更高效能、更低功耗的32位处理器。

二、关于CortexM0

ARM一改其传统的命名法则,以Cortex来为其全新的微处理器系列命名。在这个系列中,核心采用全新的ARMv7架构,引进了许多革命性的突破与创新,并首次由单一款式延伸成3种款式,并各自定义其相对应的架构,分别为CortexA(ARMv7A)、CortexR(ARMv7R)、CortexM(ARMv7M)。CortexA系列适于高性能的开放应用平台,CortexR系列适于实时信号处理控制系统,而CortexM系列则瞄准了对成本和功耗敏感却又有高性能需求的嵌入式应用领域,成为在微控制器、工业控制系统、汽车控制系统及无线网络等各种手持应用系统中的最佳解决方案。

CortexM0是CortexM家族中的微处理器核心,其拥有最低闸数、最低功耗以及强悍性能的优异表现。CortexM0为32位、3级流水线RISC处理器,其核心与ARM7同为冯·诺依曼(Von Neumann)架构,采指令和数据共享同一总线的设计。作为新一代的微处理器,CortexM0在整体的设计架构上进行了许多改革与创新,如折中效率和程序代码密度的全新指令集架构(ISA)、事先定义的系统存储器地址映像(system address map)、改善效率并增强确定性的嵌套向量中断系统(NVIC)与不可屏蔽中断(NMI)、全新的硬件除错单元等等,都带给了使用者全新的体验和更便利、更有效率的操作。

CortexM0其核心架构为ARMv6M,为CortexM家族架构ARMv7M的一个子集,去除了许多复杂的支持,所以大幅降低基本核心之门数至12K,从而拥有极低之动态功耗85 μW/Hz。而在低成本、低功耗的前提下,由于采用了全新的指令集架构Thumb2 指令集,CortexM0并没有牺牲掉应有的效能,其运算能力可以达到0.9 DMIPS/MHz,而与其他的16位与8位处理器相比,由于CortexM0的运算性能大幅提高,所以在同样任务的执行上CortexM0只需较低的运行速度,而大幅降低了整体的动态功耗。

三、指令集Thumb2

在传统的ARM7TDMI处理器系统中,系统重置后都是从ARM状态/指令集开始运行,处理器核心可以根据特定的应用需求切换到Thumb状态/指令集执行。ARM指令集为一32位长度之指令码,由于指令码长度较长,所以指令集都可以是有条件的执行,以获得较出色的效能。Thumb指令集为一16位长度之指令码,为ARM指令集之子集,程序代码密度提高了一倍,但可能需要更多的指令去执行相同的任务,所以造成了性能的下降。程序设计者可以根据不同的需求在两种状态下切换,以在程序代码效能和密度中取得平衡,但在状态切换中会有额外的程序执行,导致性能进一步的下降。另外ARM和Thumb指令集需要以不同方式编译,而增加的软件开发管理上的复杂度。Thumb2指令集则是一全新的技术,为一16位和32位指令码的结合,两种长度的指令码可共存于同一模式。所以全新的Thumb2技术结合了16位指令集高程序代码密度与32位指令集高效能的各自优点,并免去了状态切换之复杂度,而提升了整体的效能。

CortexM0同时支持了Thumb和部分的Thumb2指令集,核心不论是在正常程序执行还是处理中断异常模式均保持在单一Thumb状态下执行,免去了不必要的状态切换,大幅地节省了执行时间和指令码大小。

四、系统存储器地址映像

CortexM0核心采用一个系统存储器地址映像,为高达4 GB的可寻址存储空间提供简单和固定的映像机制。这个存储器映像机制为程序代码、SRAM、外部内存和外围设备提供了预先定义的专用地址。在传统的ARM微处理器架构中,并没有预先定义好存储器映像地址,而是由各家芯片制造商自行定义和设计,因此即使采用了相同的核心处理器,却有完全不同的存储器映像地址,给相互间程序代码移植带来了很大困难。CortexM0则是预先定义好了完整的存储器地址映像表,详细载明了每个区间地址内存储器的作用和特性,但也预留了某些区域给各家厂商自行设计。这种预先定义的映像关系,使得各家厂商可以对存取速度从事高度的优化,而且对于单芯片上的系统设计而言更易整合。

五、嵌套式向量中断系统

嵌套式向量中断系统(NVIC)是CortexM0另一个令人注目的创新设计,它可以依据使用者不同的需求进行高度配置。CortexM0中的NVIC支持16个系统异常(exception,部分为系统保留)与最多32个外部中断(interrupt,外部中断支持数量由芯片设计商自行配置)供芯片设计商使用,搭配4级优先权的设置并借助NVIC与CortexM0核心紧密的结合为整个系统提供丰富且实时的中断处理能力。

CortexM0采用一个事先定义的向量表,属于程序代码的一部分,向量表定义了堆栈的起始地址和各个异常/中断的入口地址。当某个中断被接受之后,CortexM0通过内部总线从向量表中获取其地址来执行。硬件支持的向量化中断功能大幅地缩短了进入中断的延迟,提高了程序效能,因为程序不再需要判断中断来源和进行必要的寄存器堆栈,完全由硬件自动完成。当异常发生时,程序状态寄存器(PSR)、程序计数器(PC)、链接寄存器(LR)和R0~R3、R12等通用寄存器将自动被存进堆栈;同时,处理器从中断向量表中读取出相对应的中断服务程序地址,并获取中断服务程序的第一条指令。一旦堆叠存储和取指完成后,中断服务或异常处理程序便开始执行,展现了极高且确切的效能。随后在中断服务程序结束前,相关寄存器将自动从堆栈中取出,原本中断了的正常程序也因此恢复执行,完全不需要软件的介入。由于可以在硬件中处理堆栈操作,CortexM0避免了传统的C语言中断服务程序中为了完成堆栈处理所要编写的汇编程序,这使应用程序的开发变得更加简单与便利。另外,值得一提的是,CortexM0还支持了所谓的TailChaining和LateArrival先进技术,大幅改善了传统ARM微处理器在相异的中断请求交互发生时的处理效率,缩短了中断延迟,进一步提升了CortexM0在实时系统的处理能力。

六、与ARM7TDMI 之比较

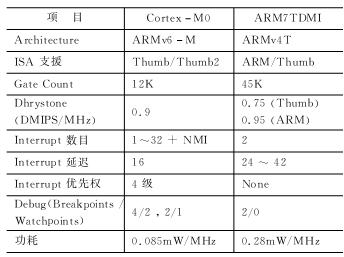

基于ARM7核心的微处理器在过去几十年袭卷了32位MCU市场,在此将CortexM0和这位师出同门的老大哥加以比较,使大家清楚它们的差异。

七、新唐科技NuMicro家族

微控制器(MCU)厂商新唐科技(Nuvoton Technology Inc.)前身为华邦电子逻辑事业群,近期推出以ARM CortexM0为核心的32位微控制器——NuMicro家族。该家族采用ARM公司最新发布的最小型、最低功耗、低门数、精简程序代码的CortexM0处理器,内建各种模拟与混合信号组件以及多种高速通信能力装置,执行效能约为传统8051的72倍。基于Keil开发环境下,客户很容易从8051升级至NuMicro来创造产品价值与竞争力。

NuMicro家族的成员包括了四大系列,NUC100系列、NUC120系列、NUC130系列、NUC140系列。其核心CortexM0的执行频率为50 MHz,具有先进的嵌套向量中断控制(NVIC)、唤醒中断控制(WIC)、单周期32位乘法器与Serial Wire硬件除错单元支持等优异特性,并拥有Sleep与PowerDown不同的节能模式;并且配置了一个递减计数24位SysTick Timer,它可定时产生中断,提供理想的计时功能来驱动实时操作系统或其他预定的任务。此家族配备了多达128 KB的闪存和16 KB的SRAM,外围设备提供了高达12位、800 ksps的8 通道ADC、多组UART、SPI、I2C与USB2.0等高速总线等接口。其他外设则包括至多80个GPIO脚、4组通用计数器/定时器、RTC、看门狗定时器与PWM、CAN总线控制器丰富的外围装置可供客户依需求搭配使用,并提供多种封装样式供选择。

八、总结

CortexM0核心的逻辑门数很少,非常适合低成本、低功耗要求的应用。由于支持全新的Thumb2指令集,免除了状态间的切换,增强了整体效能,提升了程序代码密度,简化了软件的开发与维护,缩短了产品的开发时间。CortexM0内建除错系统,在支持传统的JTAG基础上,开发了更新更好的Serial Wire除错接口,并配置了多达4个断点和2个观察点。CortexM0已获得ARM微控制器开发套Keil RealView MDK的支持,结合了ARM RealView编译工具以及强大完善的Keil uVision IDE与Debugger工具。CortexM0拥有许多实时操作系统与第三方工具的支持,包括IAR Systems、Mentor Graphics等。该处理器并向上兼容于其家族系列中的产品开发工具以及二进制程序代码,保证其程序代码未来的移植和发展性。相信在不久的未来,CortexM0将在整个微控制器市场和嵌入式应用系统中大放光彩。

1669

1669

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?