1.先打开一个PCB文件,在PCB工程界面:设计-规则-electrical-clearance-选中右键-新规则-左键点中新规则

2.右边出现设置框-在上面的“where the first object matches”框下面的高级旁边,点“询问构建器”

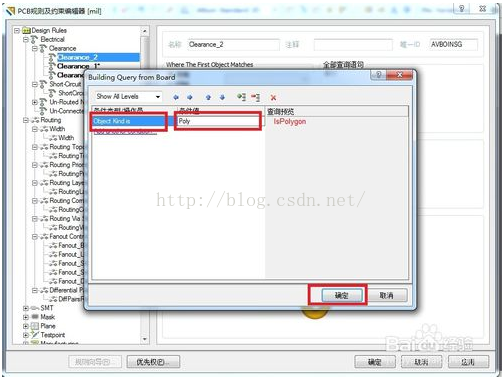

3.-左边的“条件类型/操作员”点中出现的下拉框选择“object kind is”,在右边的“条件值”选择“poly”然后确定

4.设置框右边出现“Ispolygon”,将其改为“Inpolygon”,即第二个字母s改为n

5.这时就可以更改最底下的“约束”里面“最小间隔”的值!

注意:这种方法改的最小间距只是覆铜与导线或过孔的间距,如果直接改默认Clearance会连引脚和导线的间距也改掉,导致部分和引脚靠的近的导线报错,所以要分开改。

2095

2095

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?