了解了ALU,我们来说说CPU内部的控制单元(CU)

理解CPU内部控制单元(Control Unit, CU)的深层原理涉及到计算机体系结构中的核心概念和技术细节。下面将更详细地探讨控制单元的实现细节和底层原理:

1. 指令解码的底层实现

指令解码是控制单元的关键任务之一,其过程涉及将二进制指令翻译成控制信号,以驱动CPU的各个功能单元执行相应的操作。

- 操作码(Opcode)的格式解析:

- 操作码是指令的一部分,它定义了指令的类型和操作内容。操作码的位宽(例如8位或16位)取决于指令集架构(如x86、ARM等)的设计。

- 控制单元通过解析操作码确定指令的类型(算术、逻辑、数据传输等)和具体的操作。

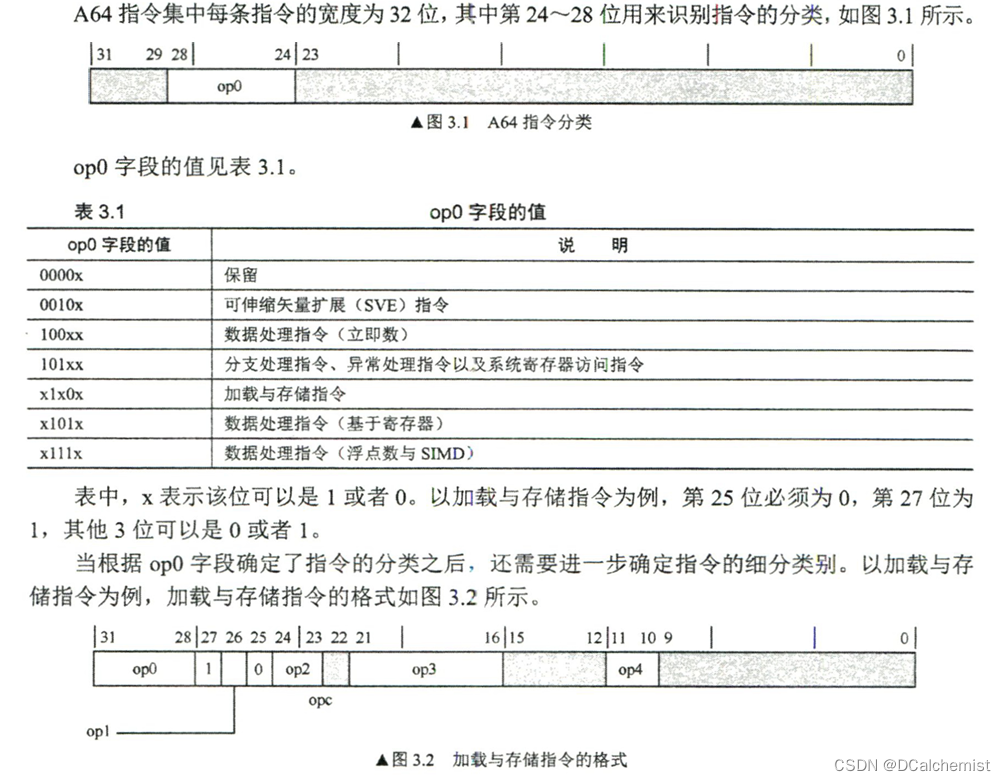

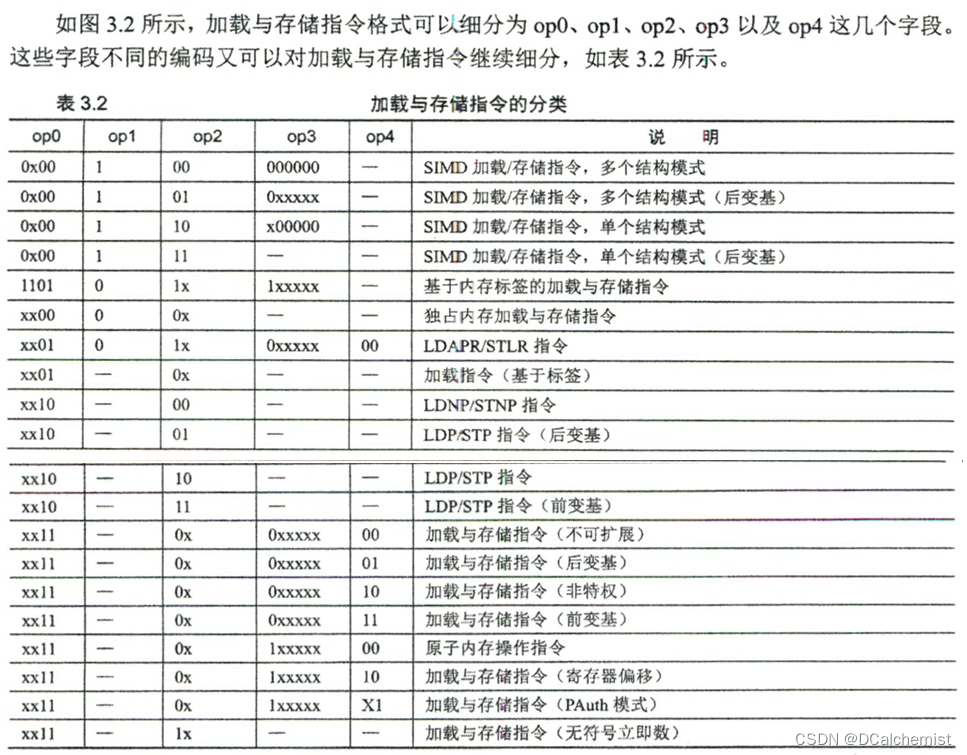

以A64指令格式为例:

2. 控制信号的生成和传输

控制单元生成各种控制信号,并通过内部总线将这些信号传递给CPU的其他功能单元,以执行指令的各个阶段和操作。

-

时序控制信号:

- 控制单元生成时钟信号和同步信号,这些信号同步整个CPU内部各个模块的操作,确保指令在正确的时间序列内执行。

-

数据通路选择信号:

- 根据指令的操作类型和操作数的位置,控制单元生成数据通路选择信号,指导数据的流动路径(如将操作数从寄存器传输到算术逻辑单元ALU)。

-

状态控制信号:

- 控制单元管理CPU的状态转换,例如从取指状态到解码状态再到执行状态的转换,确保指令按顺序和正确执行。

3.实现方式:

上述这些一般通过两种方式实现:

- 硬布线控制:

- 硬布线控制是一种基于固定逻辑电路的设计,它直接生成控制信号。硬布线控制器由组合逻辑电路和状态机组成,这些电路根据当前状态和输入信号生成所需的控制信号。

- 状态机:状态机是硬布线控制的核心组件,它在不同的时钟周期内切换状态,基于当前状态和输入来生成下一步操作所需的控制信号。

组合逻辑电路:这些电路根据输入信号(如指令码、条件标志)和当前状态生成输出控制信号。它们设计相对简单且速度快,但灵活性较差,难以适应复杂的指令集 。

- 微程序控制:

- 微程序控制使用微指令和微程序存储器来生成控制信号。每个微指令包含一组控制信号,用于执行 CPU 的基本操作。

- 微指令(Micro-instructions):每条微指令定义了一组要执行的基本操作或微操作(micro-operations)。这些操作通常包括数据传输、ALU 运算、寄存器操作等。

微程序存储器(Microprogram Memory):存储所有的微指令。微程序控制器通过读取和解释这些微指令来生成控制信号。

控制存储器(Control Memory):用于存储微程序。在执行指令时,控制单元从控制存储器中提取微指令,并根据这些指令生成控制信号 。

3. 分支预测和跳转处理的实现

分支预测的实现涉及到处理器的硬件设计和算法逻辑。下面详细解释分支预测的具体实现方法和流程:

-

静态分支预测:

-

静态分支预测是最简单的方法,它基于分支指令本身的统计特征或者固定的规则进行预测。典型的静态分支预测方法包括:

-

基于分支指令位置的预测:例如,按照分支指令的位置(比如离函数开头的距离)来做出预测。例如,某些编译器或处理器可能会默认选择执行条件跳转时最可能的分支。

-

基于分支历史数据的统计预测:根据程序的统计信息,比如某个条件分支在大多数情况下的执行方向是哪个,来预测分支的行为。

-

-

静态分支预测的优点是简单高效,但缺点是无法适应程序运行时的动态变化,可能导致准确率不高。

-

-

动态分支预测:

-

动态分支预测是处理器中更为常见和复杂的预测方法,它通过维护分支历史信息和预测算法来动态地调整预测。典型的动态分支预测方法包括:

-

两位饱和计数器(Two-bit Saturation Counter):这是一种常见的动态分支预测技术。每个分支指令会有一个对应的两位计数器。计数器的状态可以表示四种状态:Strongly Taken、Weakly Taken、Weakly Not Taken、Strongly Not Taken。根据历史执行情况,动态调整计数器的状态,以便在未来做出更准确的预测。

-

全局历史分支预测(Global History Branch Prediction):处理器会维护一个全局的分支历史记录表(Branch History Table,BHT),记录所有分支指令的历史行为。每个分支指令的历史行为(例如,最近的几次执行情况)会被用来决定下一次执行时的预测。

-

局部历史分支预测(Local History Branch Prediction):与全局历史不同,局部历史分支预测会为每个分支指令维护一个特定的历史记录表。这种方法更加精确,因为它考虑了每个分支指令的独特历史行为模式。

-

-

-

实现流程概述:

-

分支预测缓冲器(Branch Prediction Buffer):处理器会有一个预测缓冲区,用来存储预测结果和分支历史信息。

-

分支目标缓冲器(Branch Target Buffer,BTB):用来存储分支目标地址及其预测的执行状态(比如分支方向)。

-

预测算法逻辑:根据当前的分支指令及其历史行为,使用预测算法(如两位饱和计数器、全局历史或局部历史算法)来预测分支的执行方向。

-

预测更新:当分支指令实际执行时,根据实际结果更新预测缓冲区中的历史信息,以提高未来预测的准确性。

-

异常处理:处理器还需要考虑分支预测错误可能带来的异常情况,如分支预测失败需要撤销并重新执行的处理。

-

-

性能优化和挑战:

-

准确性:动态分支预测的准确性直接影响到处理器的性能。优化预测算法和增加预测历史信息是提高准确性的关键。

-

成本和复杂性:预测硬件的成本和复杂性随着预测算法的复杂性而增加。处理器设计者需要在准确性和成本之间进行权衡。

-

预测器状态管理*:预测器状态的管理和更新需要考虑处理器的并发执行和多核处理。

-

分支预测技术是现代处理器架构中一个复杂而关键的部分,它通过减少分支指令带来的流水线停顿和提高指令级并行性,显著提高了处理器的性能和效率。

控制单元需要处理条件分支和无条件跳转指令,以支持程序的流程控制和优化指令执行效率。

4. 异常和中断处理的实现

控制单元还负责处理和响应各种异常情况和外部中断,以确保系统的稳定性和可靠性。

-

异常检测和处理:

- 控制单元检测和识别指令执行过程中可能发生的异常情况,如除零错误、内存保护违规等。

- 异常处理机制允许CPU快速转移到异常处理程序,并在处理异常后恢复正常指令流的执行。

-

中断响应:

- 在外部设备请求中断时,控制单元中止当前指令的执行,并跳转到中断处理程序执行特定的中断服务例程。

- 中断处理保证了系统对外部事件的及时响应和处理。

这部分我会放到后面armv8的异常处理中再做详细讲解。

感谢阅览,欢迎斧正,收藏~

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?