4.1 Y86-64指令集体系结构

通过Y86——一个模拟X86的体系结构学习CPU结构

程序员可见状态

去掉了%r15,用F代表无寄存器。

Y86-64指令

只支持64位。

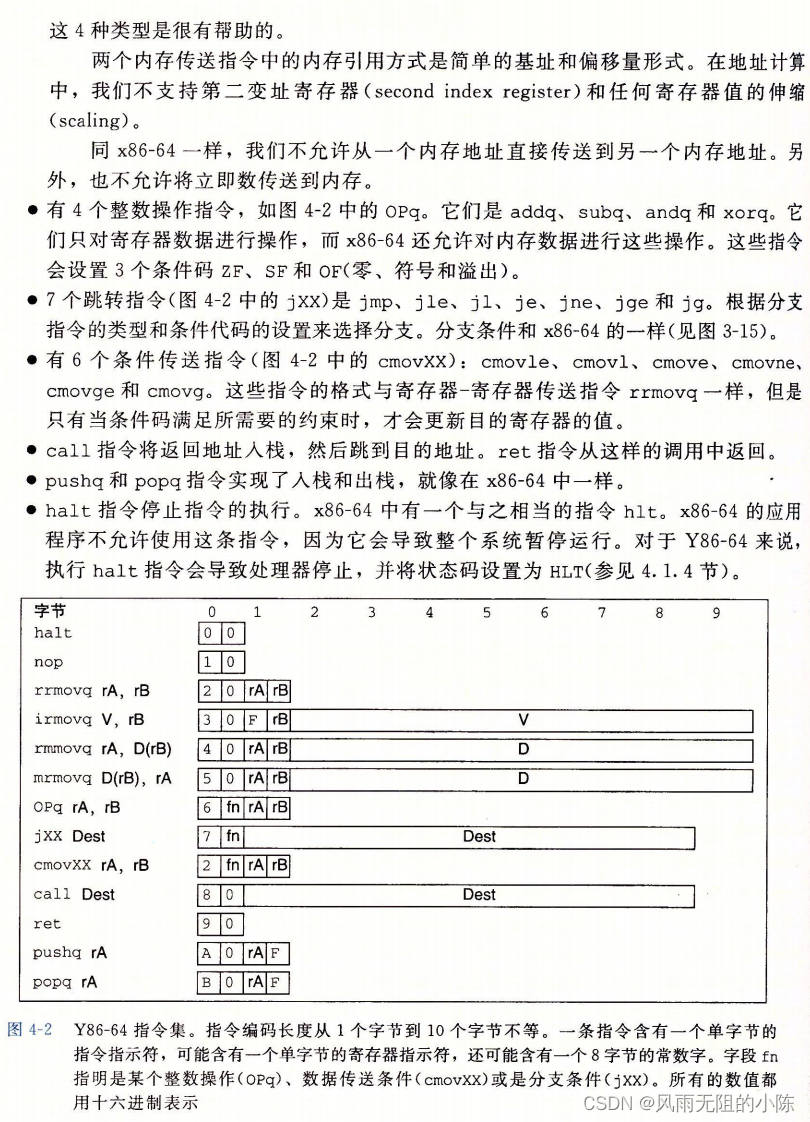

mov:

分成irmovq,rrmovq,mrmovq,rmmovq。不支持第二变址寄存器,和伸缩。即rrmovq (%rdi,%rsi,4) %rdx这样的格式,他的意思是说,在%rdi地址基础上,加上4倍%rsi寄存器的值,将这个运算得到的地址内的值移到%rdx。

算数运算:

addq, subq, andq, xorq,这些指令会设置条件码。

跳转,条件传送,call&ret,push&pop,halt

指令编码

与x86类似。第一个字节前四位指明指令大类,后四位指明具体行为,比如 addq=0x60。第二个字节指明REGIS A,B。

4.2逻辑设计和硬件控制语言HCL

逻辑门

我们代码中常用的逻辑在硬件控制语言HCL中的体现如图

组合电路和HCL布尔表达式

将很多的逻辑门组合成一个网,就能构建计算块(computational block),称为组合电路(combinational circuits)。如何构建这些网有几个限制∶

- 每个逻辑门的输入必须连接到下述选项之一∶1)一个系统输入(称为主输入),2)某

个存储器单元的输出,3)某个逻辑门的输出。 - 两个或多个逻辑门的输出不能连接在一起。否则它们可能会使线上的信号矛盾,可能会导致一个不合法的电压或电路故障。

- 这个网必须是无环的。也就是在网中不能有路径经过一系列的门而形成一个回路,这样的回路会导致该网络计算的函数有歧义。

HCL布尔表达式都能够被转化成电路设计。比如位相等bool eq = (a && b) || (!a && !b)就可以用下图表示。

而多路复用器电路(MUX)bool out = (s && a) || (!s && b);,用S控制输出a,b(s为1时,输出等于 a;而当s 为0时,输出等于b。)可以用下图表示。

HCL表达式代表的组合逻辑电路和C语言中逻辑的异同

它们都是用布尔操作来对输入进行计算的函数。值得注意的是,这两种表达计算的方法之间有以下区别∶

-

因为组合电路是由一系列的逻辑门组成,它的属性 是输出会持续地响应输入的变

化。 如果电路的输入变化了,在一定的延迟之后,输出也会相应地变化。相比之下,C表达式只会在程序执行过程中被遇到时才进行求值。 -

C的逻辑表达式允许参数是任意整数,0表示FALSE,其他任何值都表示TRU

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

947

947

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?