一、硬件描述语言概述

1.主要的硬件描述语言

- VHDL(VHSIC HDL): 天然支持并发描述,允许在同一个文件中定义多个并发执行的进程;可读性和可维护性较好,适合于大型项目和团队合作;支持用户定义的数据类型;可以使用抽象类型为系统建模

- Verilog HDL:Gateway Design Automation:语法更为灵活,允许多种描述同一硬件结构的方式,包括行为级、RTL级和门级描述;也支持并发性,但更倾向于顺序执行模型,需要使用特定的并发控制结构(如always块)来描述硬件的并发能力;代码简洁,易于编写;数据类型只能由语言本身定义,不能由用户定义;适于硬件结构的建模,不适于抽象的硬件行为建模。

- OO VHDL:美国国防部(面向对象)

- DE VHDL:美国杜克大学

- VITAL:美国电气与电子工程师协会(IEEE)

2.Verilog支持的五种不同的描述方法

- 系统级(System)

- 算法级(Algorithm):描述可以不对应具体电路,可广泛使用各种函数,代码最终的运行平台为计算机,通常不可综合

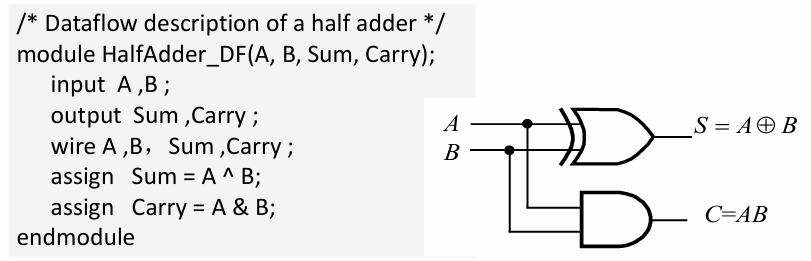

- 寄存器传输级(RTL):模型描述对应具体电路,代码最终的运行平台为FPGA或者ASIC,可综合

-

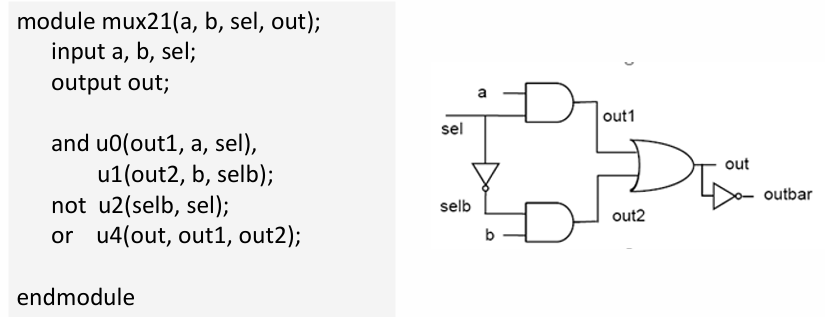

门级(Gate):模型描述对应具体电路,代码最终的运行平台为FPGA或者ASIC,可综合

-

开关级(Switch-level)

3.综合

3.1 定义

从高级别的描述自动转换到较低级别的描述的自动化方法

3.2 数字电路设计中的综合

寄存器传输级设计RTL design----(逻辑综合)---->门级网表Gate-level Netlist----(物理综合)---->物理版图Physical Layout

3.3 语句

可综合语句:if-else, case, for*, assign, begin-end, always等

不可综合语句:repeat, forever, time, defparam, finish, initial等

4.知识产权核(IP核)

4.1 简介

基于ASIC或FPGA预先设计好的,时序、面积、功率可配置的电路功能模块;复杂芯片设计时常调用已有IP核

4.2 优势

IP调用可以提高系统的设计效率,缩短系统的设计周期

4.3 常见IP核

常见的IP核:FIFO、PLL、RAM

分类:

- 软核: 使用RTL或者更高级别的描述定义的功能块,不涉及电路的具体实现,验证通过并且可综合;灵活、可移植、可重用;电路性能无法得到保证

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

3656

3656

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?