SOC——JTAG (IEEE 1149.1标准)介绍

目录:

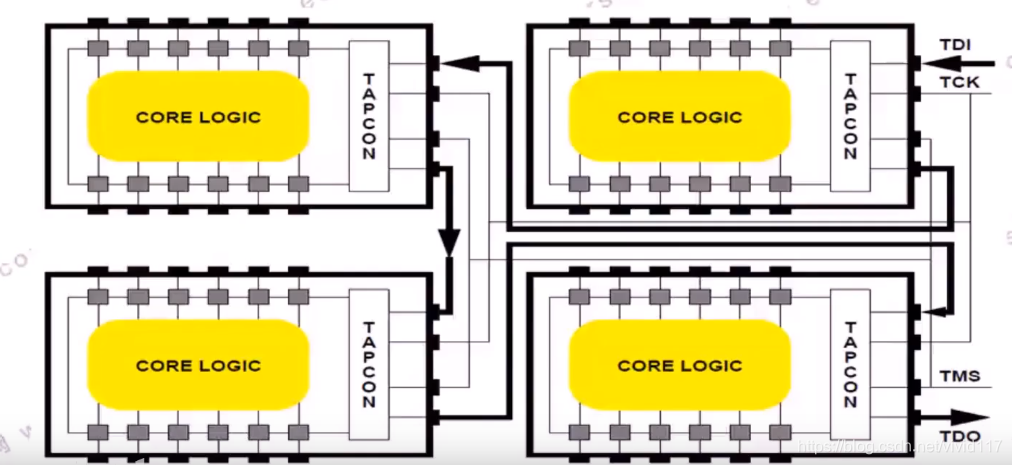

IEEE 1149.1 introduction

TAP Controller

Instruction Register

Test Data Register

Boundary Scan Cell

Boundary Scan Description Language (BSDL)

1. IEEE 1149.1 introduction

出发点:管脚的焊接问题,测试芯片之间的logic, 判断位置连接等 —>JTAG(joint Test Action Group)

定义了一些接口,TDI TCK TMS TDO TRST*

Test Acess Port (TAP)

TAP Controller

IR

Test Data Register—Basically Bundary scan register

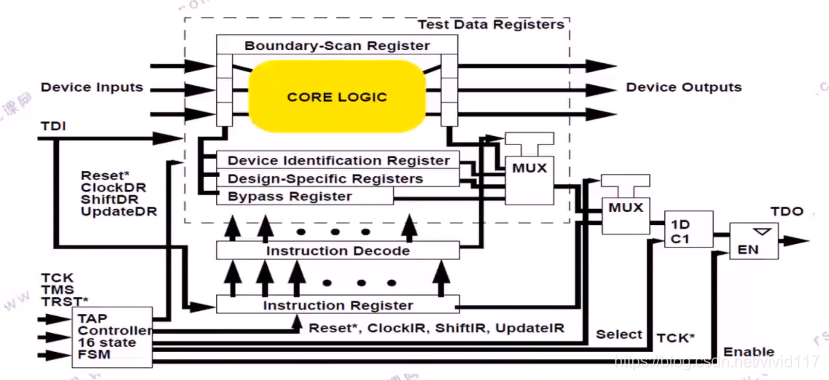

2. Acrchitecture IEEE 1149.1 introduction

Boundary Scan Register 所关注的logic是device 本身的function input 到内部系统逻辑之间的位置,以及正常的function 的输出,截断function logic,可以正常工作。

JTAP接口去做debug 对软件测试,数据寄存器,地址总线,指针等调试。

Input :TCK(TAP ctrl),TMS(TAP ctrl),TDI(IR &DR), TRST*(可上电reset)

Output :TDO(IR &DR)

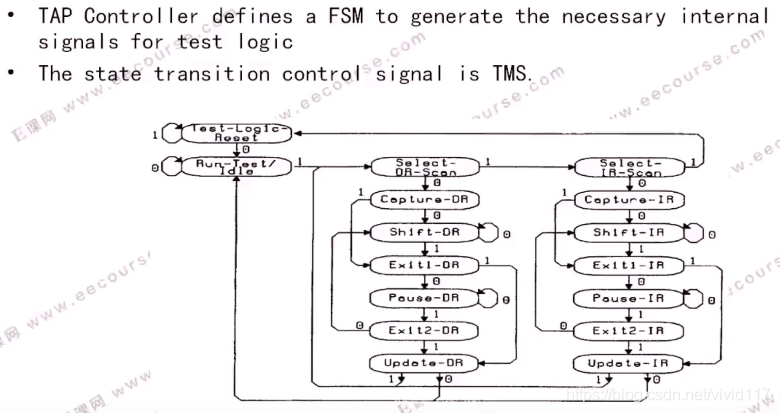

3. TAP Controller

16个FSM

初始状态:TMS = 11111

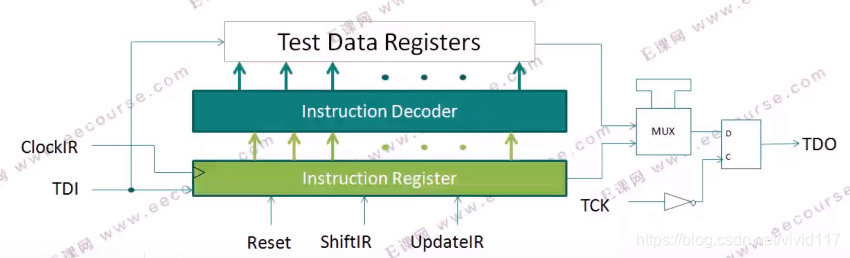

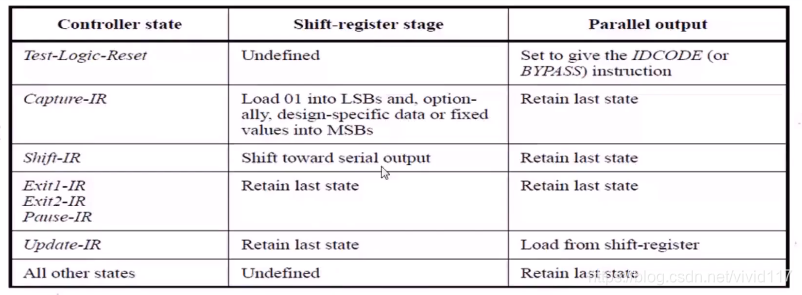

4. IR

串行输入,并行输出寄存器

译码逻辑

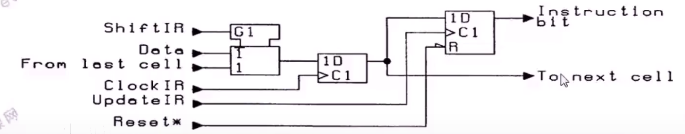

5. IR cell

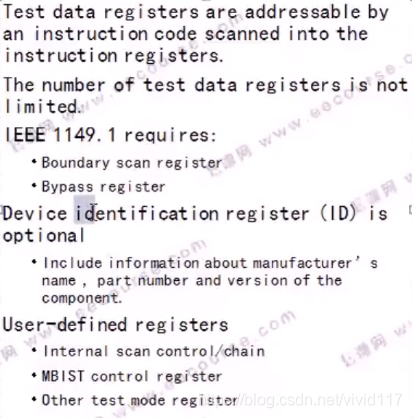

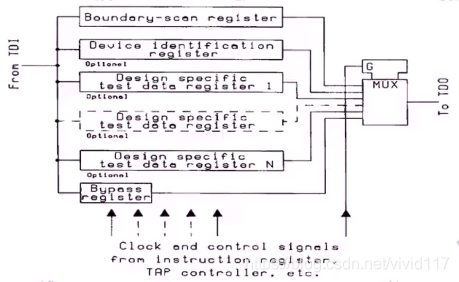

6. Test Data Register

数量不限制。

IEEE 1149.1 要求:

Boundary Scan register

Bypass Register

Device ID Register (optional)包含制造信息(代工厂等)代码标识. 4bit 数据 公司自定义的信息,版本信息等

User Defined Register

Internal scan control /chain

MBIST ctrl register

other test mode register

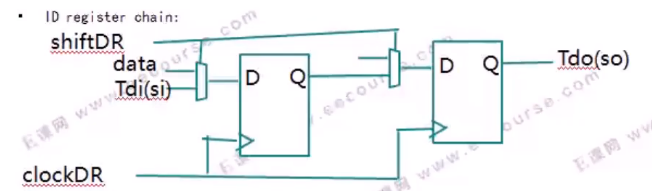

ID register chain

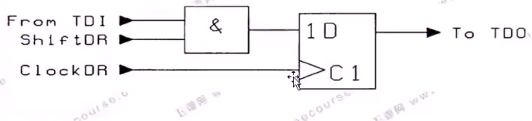

7. BYpass Register

提供最短的路径从TDI —>TDO

one stage

BYPASS只能在Shift DR状态下 Clock DR工作

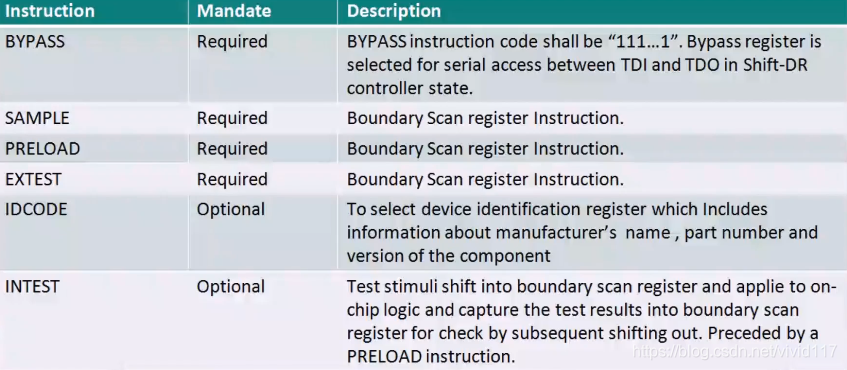

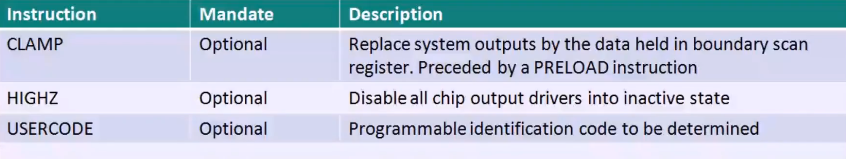

8. IEEE 1149.1 标准指令

BYPASS: TDI和TDO直接bypass -->shift DR加快测试速度,可以bypass几个不需要关心芯片的模块

SAMPLE

PRELOAD

EXTEST

IDCODE*

INTEST*

CLAMP*

HIGHZ*

USERCODE*

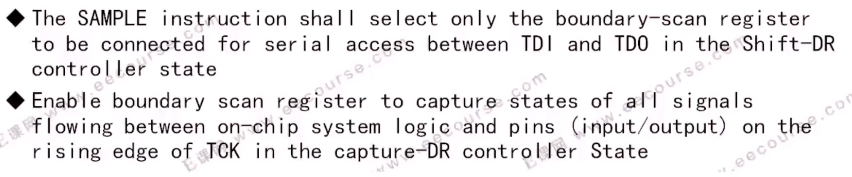

9. SAMPLE INstruction(采样指令)

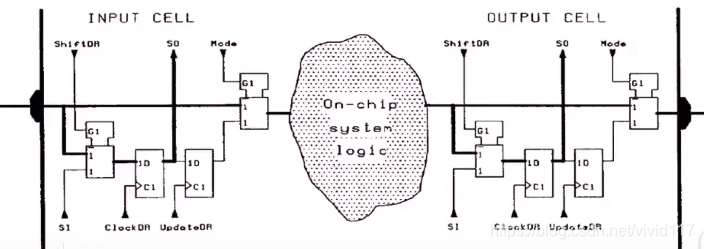

PRELOAD指令(通过shift register 进去数据,再通过Updata DR hold register里)

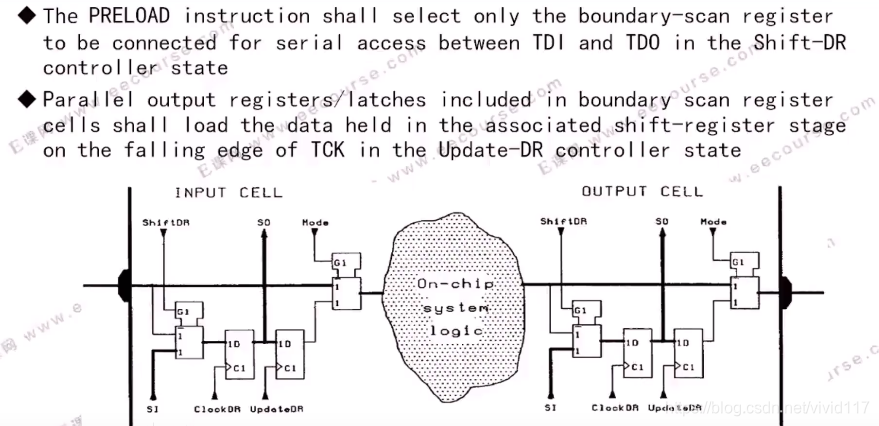

EXTEST (用BS通信测试,用 Shift 捕捉输入,HOld register bypass 内部输出)

基本指令一般针对板级测试,适用多个芯片之间,因为不同芯片之间可能会有不同的测试要求。

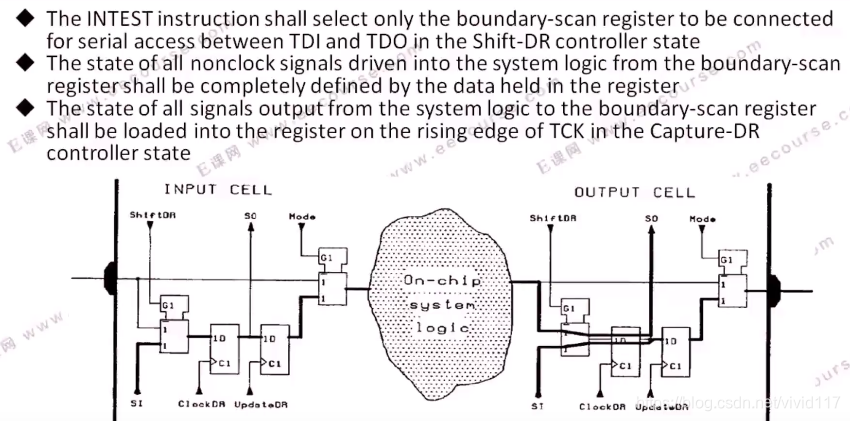

INTEST指令

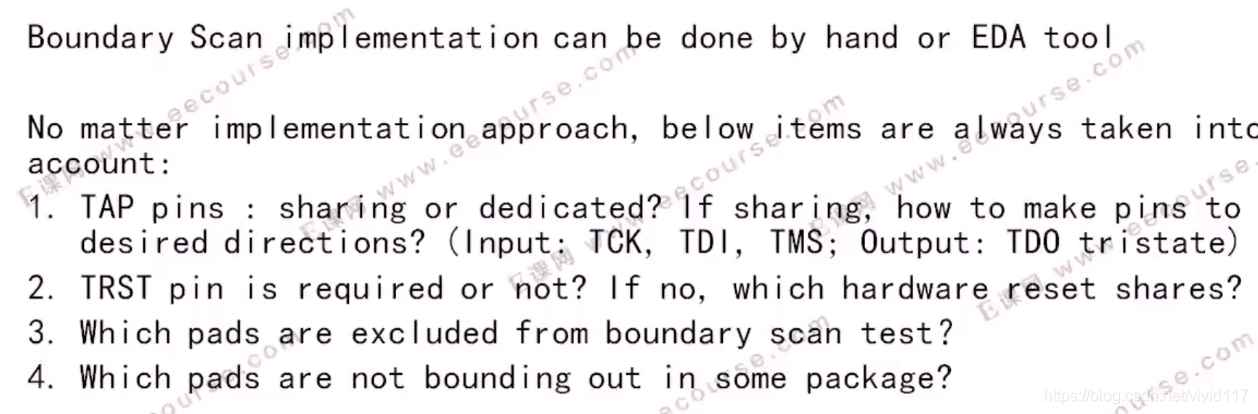

10. Implementation practice’

功能pin的复用;

IOMUX选择

REST 是否需要,自带hardware的复位,上电初始化reset。

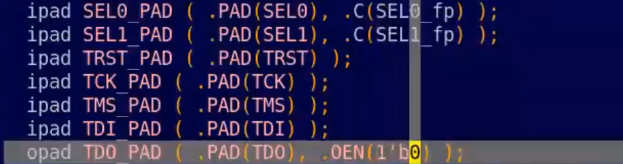

了解哪些pin不需要做,模拟pin,JTAG pin

上拉和下拉电阻的测试,HIGHZ的指令使能上拉和下拉。

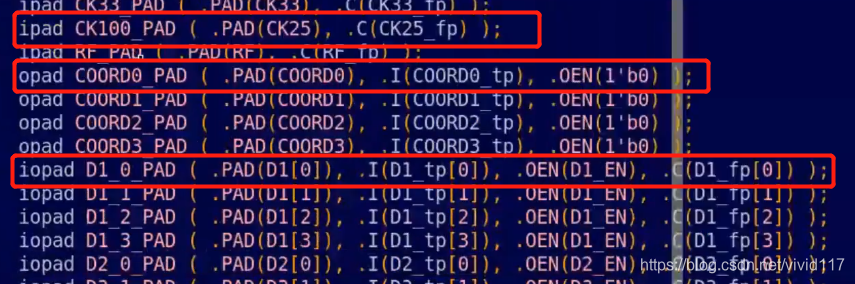

ipad RF_PAD (.PAD(RF), .C(RF_fp)); //一般的接口定义,PAD表示pin,C表示 pad输入到core logic(pad--->core)。

opad COORD0_PAD ( .PAD(COORD0), .I(COORD0_tp), .OEN(1'b0) ); // I 表示从core输出到pad(core--->pad),带OEN表示I是三态的输出

ioopad D1_0_PAD ( .PAD(D1[0]), .I(D1_tp[0]), .OEN(D1_EN), .C(D1_fp[0]) ); // PAD, I和OEN是一组三态输出,C表示双向的

下面的pad输入端是连接的,I端是floating,在工具生成的时候会自动连接

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?