一、概述

I2S总线是飞利浦公司(现为NXP)为了解决日益增多的音频处理设备和音频IC之间可以标准化传输音频信号而开发的一种总线标准。它一共定义了三根线,分别是串行时钟线CLK(也叫位时钟线BCLK)、帧同步线LRCK(也叫字选择线WS)和串行数据线SD。

二、总线特征

- 总线一共由三根线组成

- 总线协议定义了主设备和从设备,产生串行时钟信号和帧同步信号的设备是主设备,接受这两个信号作为输入信号的设备叫从设备

- 支持全双工和半双工通信

- 包括左右两个声道

三、总线协议详情

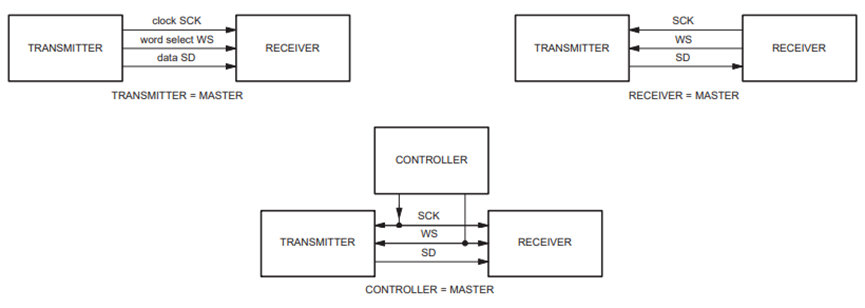

1. I2S简单系统模型

上图列出了三种应用模式,在第一种(左上角)模式中,发送设备(TRANSMITTER)产生所有信号,发送设备是主设备,接收设备是从设备;在第二种(右上角)模式中,接收设备(RECEIVER)产生时钟信号CLK和帧同步信号LRCK,所以接收设备是主设备,发送设备(TRANSMITTER)是从设备,从设备发送数据;在第三种(中间)模式中,时钟信号CLK和帧同步信号LRCK由控制器(CONTROLLER)产生,所以控制器是主设备,发送设备和接收设备都是从设备,数据有发送设备传输到接收设备。

2. I2S信号详解

2.1 时钟信号CLK

时钟信号的频率取决于采样频率、量化深度。

时钟信号频率 = 采样频率 x 量化深度x 2

假设采样频率是44.1KHz,量化深度是16bit,那么时钟频率CLK = 44.1 x 16 x 2 = 1.4112 MHz,其中2表示左右两个声道。

2.2 帧同步信号LRCK

帧同步信号等于采样频率,用于切换左右声道的数据。当LRCK为高电平时(逻辑为1),数据信号线上传输的是右声道的数据,反之则为左声道数据。

2.3 数据信号

数据信号线上的数据用二进制补码来表示,先传输最高位(MSB)。如果接收设备与发送设备的字长不匹配,当发送设备字长大于接收设备时,低位数据会被丢掉;当发送设备字长小于接收设备时,低位数据补0.

3. I2S时序模式

根据SD相对于SCK和WS位置的不同,I2S分为三种不同的时序模式,分别为标准I2S模式、左对齐模式和右对齐模式。

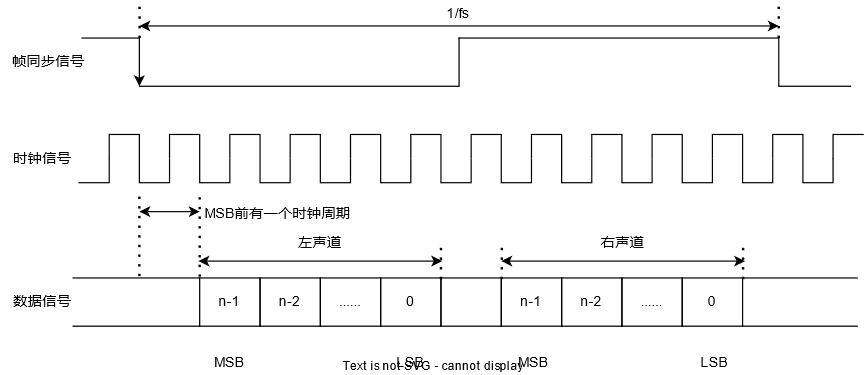

3.1 标准I2S模式

上升标准模式也叫Phillips模式,是由标准左对齐格式再延迟一个时钟周期变化来的。时序如下图所示,左声道的数据MSB在帧同步信号下降沿之后第二个时钟信号上升沿有效,右声道数据的MSB在帧同步信号上升沿之后第二个时钟信号沿有效。

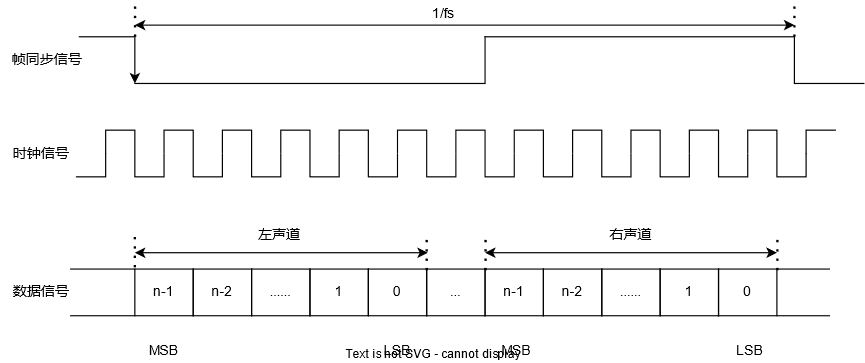

3.2 左对齐模式

下图为左对齐模式的时序图,和标准模式对比可以看出,左对齐模式的数据的MSB没有相对于时钟信号延迟一个时钟。左对齐模式的左声道的数据MSB在帧同步信号上升沿之后时钟信号的第一个上升沿有效;右声道的数据MSB在帧同步下降沿之后时钟信号第一个上升沿有效。左对齐模式的优点在于,由于在帧同步信号变化后的第一个时钟信号上升沿就开始采样,它不需要关心左右声道数据的字长,只要帧同步信号的时钟周期足够长。左对齐的方式支持16-32bit字长格式。

3.3 右对齐模式

右对齐模式也叫日本格式,EIAJ (Electronic Industries Association of Japan) 或SONY格式,下图为右对齐模式时序图。右对齐模式左声道的数据LSB在帧同步信号下降沿的前一个时钟信号上升沿有效,右声道的数据LSB在帧同步信号上升沿的前一个时钟信号上升沿有效。相比于左对齐模式,右对齐模式的不足在于接收设备必须事先知道待传数据的字长。

518

518

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?