cadence virtuoso 电路ADE 仿真小技巧

1、查看仿真信号的功率

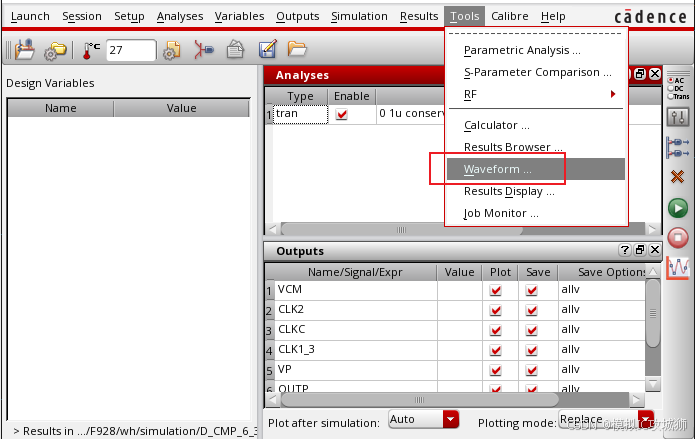

仿真前记得先设置功率信号输出

仿真结束后再如下操作

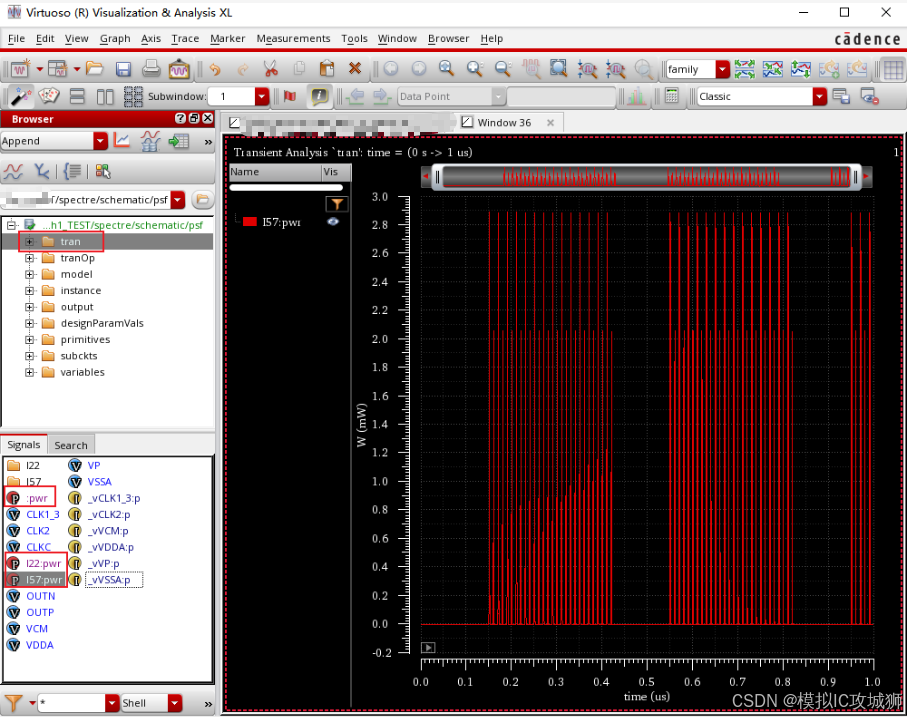

或者在新的窗口中打开仿真结果中的 simulation-spectre-schematic-PSF文件

找到TRAN

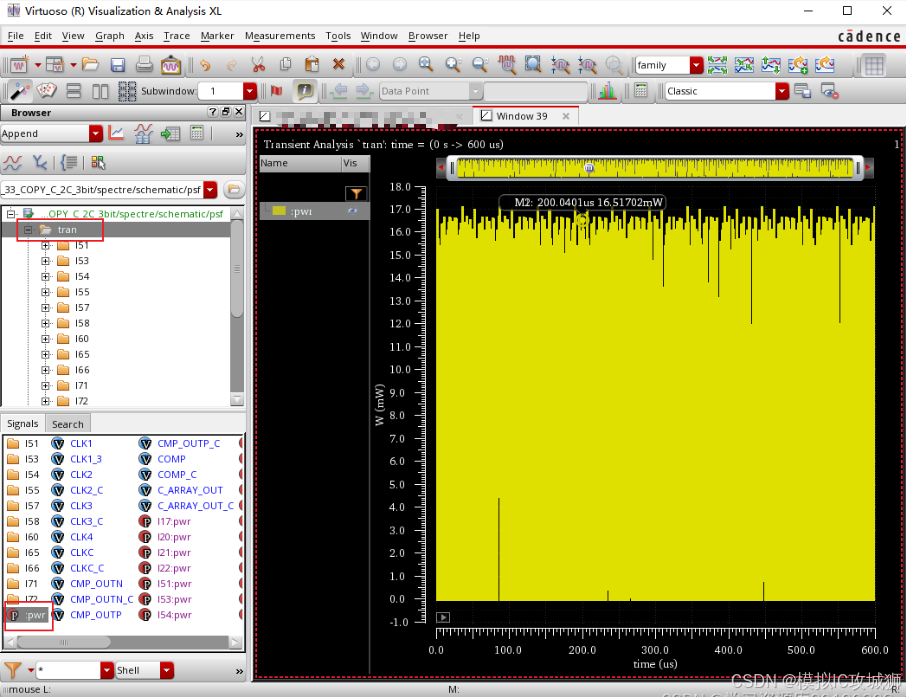

下面是计算电路的平均功耗

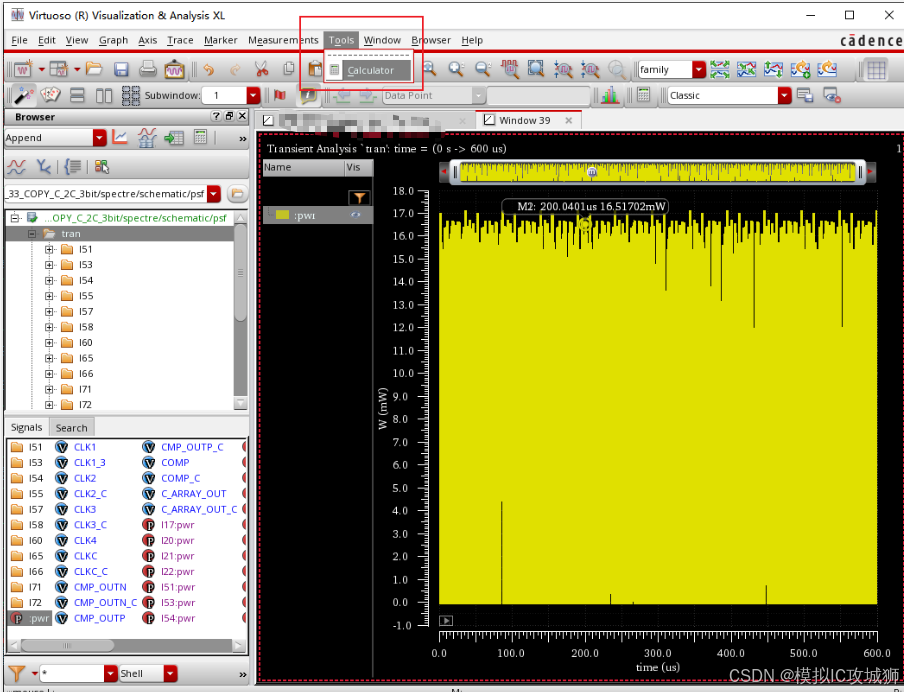

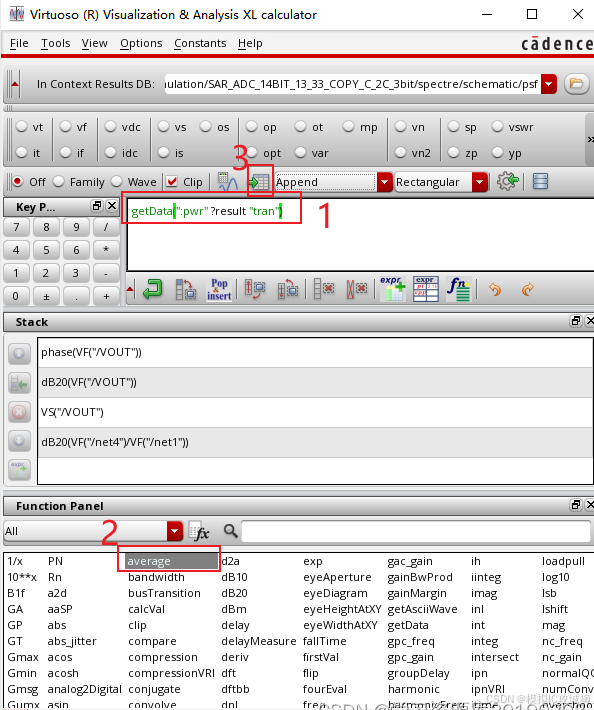

点击tool—calculator

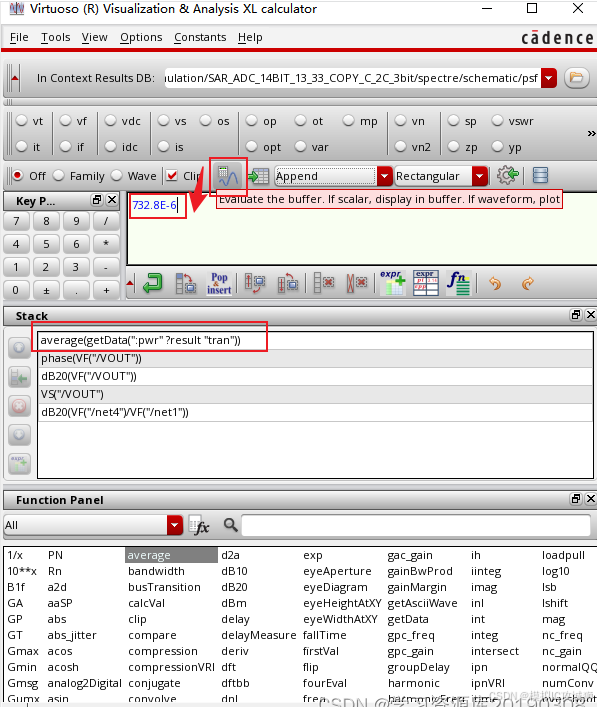

1处即为提取的功率信号,点击2计算平均值

点击3出现数值

或者点击下面,在框内出现数值

2、查看仿真信号某一点的数值

快捷键:M

3、cadence Virtuoso中加速仿真——使用服务器多核仿真

设置Threads为少于自己服务器核的数量

4、查看ADE仿真的进度

5、cadence 后仿真不收敛

ERROR (SPECTRE-16080): No DC solution found (no convergence).

解决方法:SKIP DC (跳过DC仿真)

操作:

将skip dc勾选上就可以了

九——电路学习项目

SAR ADC 详细介绍

SAR ADC详细介绍传送门

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?