在TriCore系统中,多个中断源(如外设或外部中断)可以生成中断请求(如cpu或DMA通道)。本文描述了CPU的中断处理能力,包括中断优先级方案和对向量表的访问。

一、常规操作

每个中断源被分配一个唯一的中断优先级编号,称为服务请求优先级编号(SRPN)。从中断源接收到中断请求时,中断控制单元(ICU)使用SRPN在多个并发中断请求之间确定优先级。获胜请求的SRPN作为Pending Interrupt Priority Number (PIPN)与请求触发器一起提供给CPU。CPU通过比较PIPN和当前CPU优先级数(CCPN)来决定是否接受请求的中断。如果CPU决定接受请求的中断,它响应一个中断确认,并返回被占用的中断的优先级号。然后ICU将清除请求中断源。

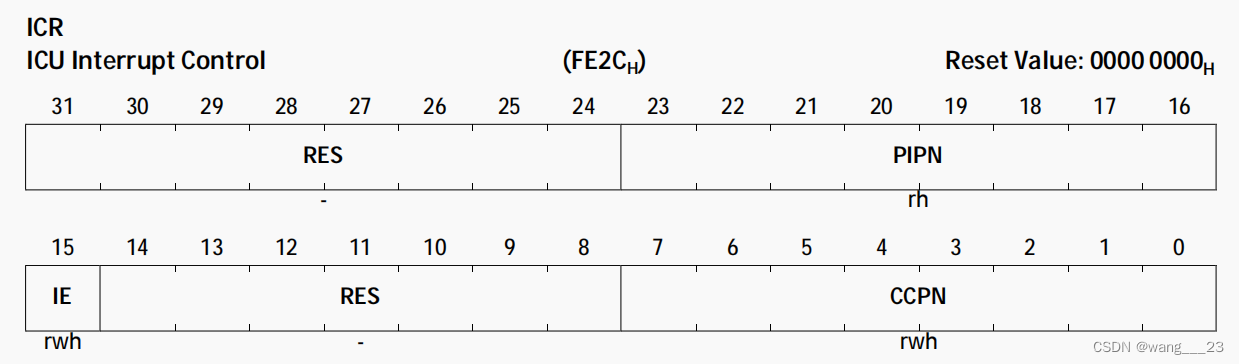

1、 ICU 中断控制寄存器 (ICR)

ICU中断控制寄存器(ICR)保存:

当前CPU优先级号(CCPN),Current CPU Priority Number

全局中断启用/禁用位(IE),Interrupt enable

当前等待中断优先级号(PIPN),current Pending Interrupt Priority Number

2 、CPU 中断请求的操作

CPU检查全局中断使能位ICR.IE的状态,并比较当前CPU的优先级数ICR.CCPN和PIPN。CPU只有在ICR.IE == 1且PIPN大于CCPN时才会中断。中断发生时CPU进入中断例程。PIPN用于确定中断向量表入口点并确认ICU, ICU反过来将确认发送回挂起的中断请求。

有几种情况可能会阻止CPU立即响应ICU生成的中断请求。这些都是:

中断系统被全局禁用(ICR.IE = = 0)。

当前CPU优先级(CCPN)等于或高于Pending Interrupt priority Number (PIPN)

CPU正在进入中断或trap服务程序

CPU正在处理不间断trap业务

CPU正在执行一条多周期指令

CPU正在执行一条修改ICR的指令

只有当这些条件不再为真时,CPU才响应中断请求。

3 、进入中断服务程序 (ISR)

当CPU满足处理中断请求的所有条件时,将执行以下操作以进入中断服务例程(ISR):

保存当前任务的上层上下文

返回地址(A[11])用当前PC更新

如果处理器之前没有使用中断堆栈(PSW.IS = 0),则A[10]堆栈指针设置为中断堆栈指针(ISP)。然后将堆栈指针位设置为使用中断堆栈:PSW.IS= 1

设置I/O模式为Supervisor模式,即开启所有权限:PSW.IO= 10B

当前保护寄存器设置为0:PSW.PRS=000B

清除调用深度计数器(PSW. CDC),并将调用深度限制选择器设置为64:PSW.CDC = 0000000B

开启“调用深度计数器”PSW. CDE= 1

PSW安全位设置为SYSCON寄存器中定义的值。PSW.S = SYSCON.IS

全局寄存器A[0]、A[1]、A[8]、A[9]的写权限关闭:PSW.GW = 0

中断系统全局禁用:ICR.IE = 0。旧的ICR.IE保存为PCXI.PIE

当前CPU优先级号(ICR.CCPN)保存在前一个CPU优先级号(PCXI.PCPN)字段中

等待中断优先级号(ICR.PIPN)保存到当前CPU优先级号(ICR.CCPN)字段中访问中断向量表来获取ISR的第一条指令

二、退出中断服务程序 (ISR)

当ISR以RFE (Return From Exception)指令退出时,硬件会自动恢复上层上下文。上面的上下文包括PCXI寄存器,它保存前一个CPU优先级号(PCPN)和前一个全局中断使能位(PIE)。这些位的值使用如下:

PCXI.PCPN写入ICR.CCPN,将CPU优先级设置为中断前的值

PCXI.PIE被写入ICR.IE恢复此位的状态

然后,中断的例行程序继续进行

三、中断向量表

中断服务例程通过中断向量表与具有特定优先级的中断相关联。中断向量表是中断服务程序(ISR)入口点的数组。

当CPU接受中断时,它在中断向量表中计算与中断优先级对应的地址(ICR.PIPN位字段)这个地址被载入到程序计数器中。CPU开始在中断向量表中的这个地址执行指令。这个地址的代码是所选中断服务程序(ISR)的开始。根据ISR的代码大小,中断向量表可能只存储ISR的初始部分,例如跳转指令,该指令将CPU指向内存中ISR的其余部分。

中断向量表的基址寄存器(BIV)存储了中断向量表的基址。中断向量在表中按优先级递增排序。在启用中断之前,在系统初始化阶段(BIV受ENDINIT保护),可以使用MTCR指令修改BIV寄存器。通过这种安排,可以有多个中断向量表,并通过改变BIV寄存器的内容在它们之间切换。

当中断时,CPU从PIPN和BIV寄存器的内容中计算适当的中断服务程序的入口点。两个矢量表配置可用,矢量之间的间距为32字节到8字节。间距由BIV寄存器的矢量大小选择(VSS)位选择。

为了生成一个指向中断向量表的指针,PIPN左移5位(VSS-0)或3位(VSS-1),并与BIV寄存器中的地址对齐,生成一个指向中断向量表的指针,ISR的执行从这个地址开始。因此,建议将寄存器BIV的bit [14:5] (VSS-0)或者[12:3](VSS=1)设置为0。

if (BIV.VSS == 1’b0)

ISR_Entry_PC = {BIV[31:1],1’b0} | {PIPN<<5};

else

ISR_Entry_PC = {BIV[31:1],1’b0} | {PIPN<<3};如果中断处理程序非常短,它可能完全适合向量代码段中可用的字。否则,存储在入口位置的代码要么可以跨越几个向量项,要么应该包含一些初始指令,然后跳转到处理程序的其余部分

中断向量表(VSS=0)

BIV寄存器允许中断向量表位于可用代码存储器中的任何位置。开机的默认值是特定于实现的。可以使用MTCR指令写入BIV寄存器在系统初始化阶段,在中断被启用之前。也可以有多个中断向量表,并简单地通过修改BIV寄存器的内容在它们之间切换。

四、使用TriCore中断系统

下面的部分包含了一些示例,展示了如何使用TriCore架构的灵活中断系统来解决典型和特殊的应用需求

1、 跨越中断服务例程

Spanning Interrupt Service Routines across Vector Entries

因为矢量入口没有绑定到中断源,所以很容易跨过矢量入口位置到中断服务例程(isr)。如果跨越不适合输入位置之间可用的8个字,则不需要跳转到中断处理程序的其余部分。

请注意,与跨服务例程占用的条目相关的优先级编号不得用于从同一服务提供者请求服务的任何活动服务请求节点(srn)。

入口2的服务例程覆盖了向量位置3和向量位置4。因此,这些数字不能分配给请求CPU服务的srn,尽管它们可以用来请求另一个服务提供者。下一个可用的矢量入口是入口5。这种技术的使用增加了给定系统中所需的优先级数的范围,但是必须相应地调整向量表的大小。

2 、中断优先级组

中断优先级组描述了一组不能中断彼此服务程序的中断。使用TriCore中断系统架构可以很容易地创建这些组。当CPU启动中断服务时,中断系统全局被禁用,CPU优先级CCPN被设置为正在服务的中断的优先级。这将阻止所有进一步的中断得到服务,直到中断系统通过软件再次启用,或者服务例程被RFE(异常返回)指令终止

注:RFE指令自动重新安装ICR.IE的先前状态。这将是一个(ICE.IE = 1),否则该中断将不会被服务

当中断服务程序(ISR)软件通过设置ICR重新启用中断系统时。IE不改变CCPN,其效果是所有与CCPN相同或更低优先级的中断请求仍然被阻止服务。这包括当前中断的重新发生,也就是说,它不能中断此服务。然而,这个ISR将被每个具有比CCPN更高优先级的请求中断。

一个潜在的问题(在TriCore体系结构中很容易克服)是,应用程序需求通常需要将具有类似重要性的中断请求分组在一起,这样组中的任何请求都不能中断同一组中另一个成员的ISR。在中断系统中创建这些中断优先级组很容易完成。对于一组已定义的中断请求,在再次启用中断系统之前,它们各自的服务例程的软件将CCPN设置为该组中使用的最高SRPN的数量。

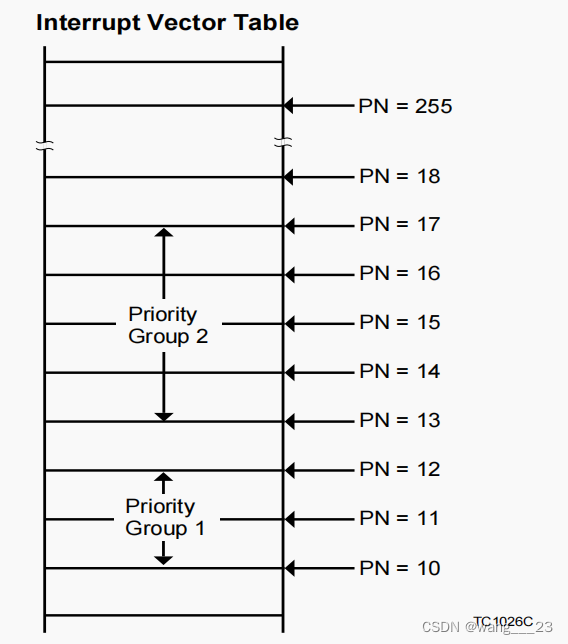

中断优先级组

优先级号为11和12的中断请求组成一组,而优先级号为14到17的请求组成另一组。每次来自第一组的一个中断被服务时,服务例程在重新启用中断系统之前将CCPN设置为12,这是该组中最高的数字。每次来自第二组的一个中断被服务时,服务例程在重新启用中断系统之前将CCPN设置为17。例如,如果中断14被服务,它只能被优先级高于17的请求中断,而不能被来自其自身优先级组的请求或低优先级的请求中断。

我们可以看到这个系统的灵活性以及它相对于具有固定优先级的系统的优越性。在上面的例子中,优先级为13的中断请求形成了它自己的单个成员“组”。将每个服务例程中的CCPN设置为最大255与不再启用中断系统具有相同的效果;也就是说,所有的中断请求都可以被认为是在一个组中。中断优先级级别的灵活性范围从所有中断在一个组中,到每个中断请求建立自己的组,以及两者之间的所有可能组合。

3、 将isr划分为不同的优先级

中断服务例程可以很容易地分成具有不同优先级的部分。例如,中断被置于非常高的优先级,因为响应时间和对事件的反应是至关重要的,但该服务例程中的进一步操作可以在较低的优先级上运行。在这种情况下,服务例程将被分成两个部分,一部分包含关键操作,另一部分包含不那么关键的操作。中断节点的优先级首先设置为高优先级,以便在中断发生时立即执行必要的操作。然后,这个中断的优先级被降低,中断请求位再次通过软件设置(表示一个挂起的中断),而仍然在服务例程中。返回到被中断的程序将终止高优先级服务例程。当CPU的优先级比它自己的优先级低时阻塞的中断被服务。进入服务例程后,它现在位于程序内存中执行中断的未完成但优先级较低的操作。

在其他情况下,服务请求的优先级可能较低,因为对事件的响应时间并不重要,但是一旦授予了服务,就不应该中断它。为了防止任何中断,TriCore体系结构允许在ISR中提高服务请求的优先级级别,并且还允许完全禁用中断。

4 、对同一中断源使用不同的优先级

对于某些应用程序,中断请求相对于其他请求的优先级不是固定的,而是取决于系统中的当前情况。这可以通过根据应用程序需要在不同时间为中断源分配不同的服务请求优先级编号(srpn)来实现。通常,该中断的ISR根据其优先级执行不同的代码。在传统的中断系统中,ISR必须检查该中断请求的当前优先级,并对适当的代码段执行分支,从而导致对请求的响应延迟。

然而,在TriCore系统中,中断将自动为不同的优先级具有不同的向量条目。不需要在ISR中进行额外的检查和分支,因此减少了中断延迟。如果ISR独立于中断的优先级,则需要在该中断的每个向量项上的公共ISR代码上放置分支。

注:在创建向量表时,必须考虑对一个中断使用不同的优先级号

5 、中断控制寄存器

两个csfr支持中断处理:

ICR:中断控制寄存器

BIV:基本中断向量表指针

ICR包含当前CPU优先级号(CCPN),中断系统(IE)的启用/禁用位,等待中断优先级号(PIPN),以及中断仲裁方案的特定实现控制。BIV寄存器保存着中断向量表的基址。特殊指令控制中断系统的启用和禁用。

ICU中断控制寄存器(ICR)

表示当前CPU的优先级。它在中断服务例程(isr)的进入或退出以及BISR指令的执行时由硬件自动更新。CCPN也可以通过MTCR指令进行更新。

基本中断向量表指针(BIV)BIV寄存器包含中断向量表的基址。当一个中断被接受时,中断向量表中的入口地址由该中断的优先级号(从PIPN中获取)生成,左移3位或5位,然后与BIV寄存器的内容对齐。中断优先级号的左移导致向量表中各个条目之间的间隔为8字节或32字节,这取决于VSS位选择的向量间隔。

BIV Base Address of Interrupt Vector Table

BIV寄存器中的地址必须对齐为偶数字节地址(半字地址)。由于左移的优先级数和BIV寄存器的内容的简单对齐,向量表的基址的对齐必须是2边界的幂,这取决于所使用的中断项的数量。

VSS Vector Spacing Select

0:32字节矢量间距

1:8字节矢量间距

1304

1304

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?