说明:用到的一些寄存器,参考用户手册,记录如下:

目录

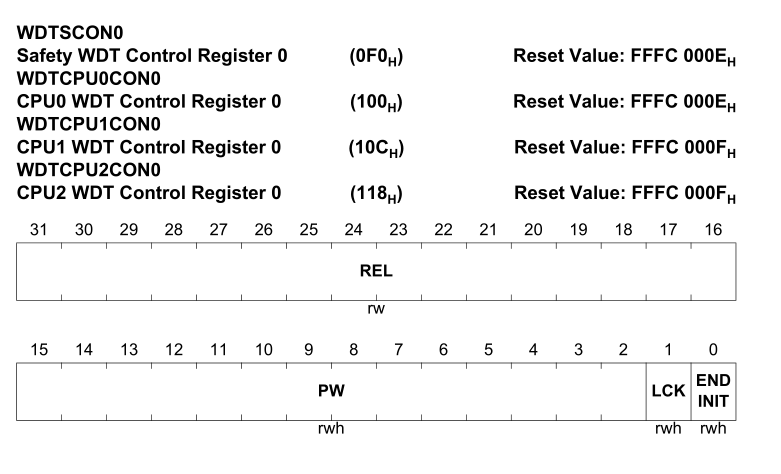

Watchdog Timer Control Register

CPU Core Special Function Registers

Watchdog Timer Control Register

看门狗定时器控制寄存器

该寄存器在检查访问和密码访问(Password Access or Check Access)中使用检查数据写入。在修改访问Modify Access期间,它还存储计时器重新加载值(REL)、密码更新和相应的初始化结束(ENDINIT)控制位。每个看门狗Watchdog x都有一个WDTxCON0寄存器。

P651-讲了Password Access相关内容

END INIT位:

End-of-Initialization Control Bit

0: 允许访问Endinit-protected寄存器, default after Application Reset

1: 不允许访问Endinit-protected寄存器

密码访问或检查访问期间( Password Access or Check Access),此位必须用“1”写入(尽管此写入仅用于密码保护机制,不存储)。在修改访问(Modify Access)期间,必须使用所需的ENDINIT更新值写入该位

在Modify Access时set 0以开始访问WDT_CON1, BTV, BIV, ISP, PCON0寄存器许可

在Modify Access时set 1以结束访问WDT_CON1, BTV, BIV, ISP, PCON0寄存器许可

LCK位:

Lock Bit to Control Access to WDTxCON0

0: 寄存器unlock

1: 寄存器lock,default after Application Reset

LCK的当前值由硬件控制。当使用有效密码访问WDTxCON0时,WDTxSR将被清除。US为0(或WDTxSR.US为1且SMU处于运行模式时),在对WDTxCON0进行有效的修改访问(Modify Access)后,它会自动重新设置。在写入WDTxCON0期间,写入该位的值仅用于密码保护机制,不存储。

LCK在Password Access or Check Access时必须必须set 0,在Modify Access时必须set 1

检查访问Check Access无法清除LCK。

PW位 :

User-Definable Password Field for Access to WDTxCON0

用于访问WDTxCON0的用户可定义密码字段

此位字段在修改访问期间(Modify Access)使用初始密码值写入。从该位字段读取将返回该初始密码,但位[7:2]会被反转(切换),以确保简单的读/写操作不足以为WDT提供服务。

如果对应WDTxSR.PAS=0则在密码访问 Password Access或检查访问Check Access期间,必须使用其当前内容写入此位字段。如果对应WDTxSR.PAS=1则在密码访问Password Acces或检查访问Check Access期间,必须使用LFSR序列中的下一个密码写入该位字段

应用程序重置后的默认密码为00000000 111100B (0x3c)

在密码访问 Password Access和修改访问Modify Access期间,位[7:2]必须用111100B写入。读取返回这些位的000011B。

REL位:

Reload Value for the WDT (also Time Check Value)

WDT的重新加载值(也是时间检查值)

在修改对WDTxCON0的访问期间,可以更改重新加载值(ApplicationReset后的默认值为FFFCH)。如果看门狗定时器已启用且处于正常定时器模式,则在正确的看门狗服务后,它将从此值开始计数。

读取此位字段时,始终返回当前的重新加载值。

在密码访问或检查访问 Password Access or Check Access期间,此位字段可用于其他检查。此类检查期间的写入对重新加载值没有影响。

如果对应WDTxSR.TCS=0则在密码访问或检查访问Password Access or Check Access期间,必须使用其当前内容写入该位字段。

如果对应WDTxSR.TCS=1则在密码访问或检查访问Password Access or Check Access期间,必须使用当前WDTxSR.TIM的反向估计值写入该位字段。

用户手册里只有后面三位,前面的在哪里得到的?

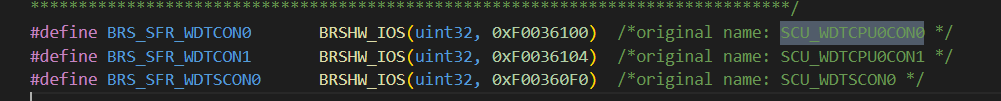

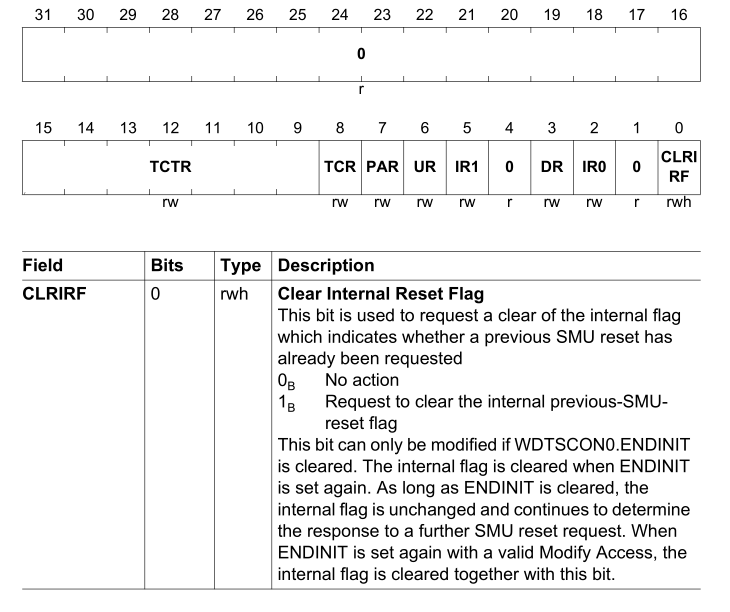

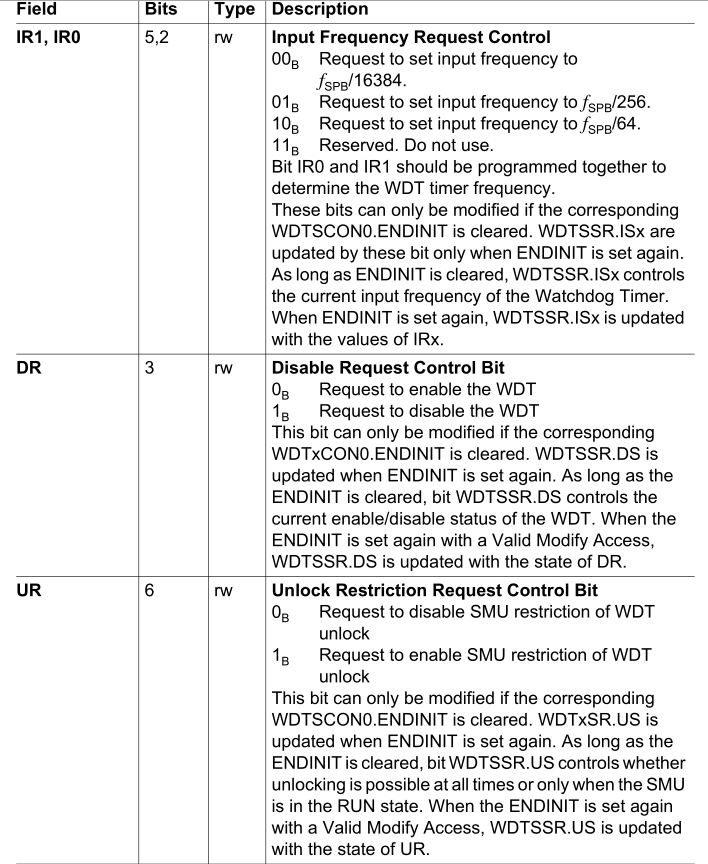

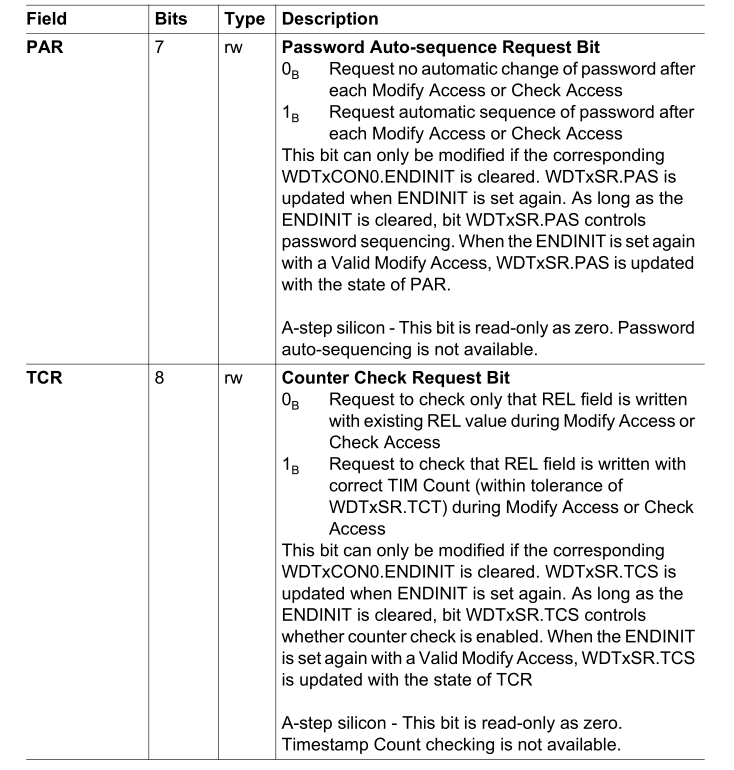

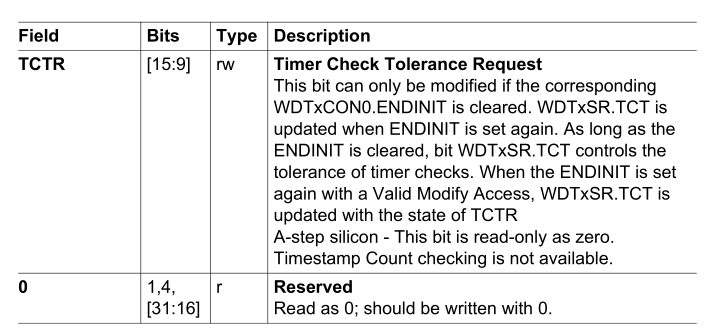

WDTSCON1

Safety WDT Control Register 1 安全看门狗控制寄存器 (0F4H) Reset Value: 0000 0000H

主要用的是DR位,在操作寄存器之前,需要解除endinit保护

Disable Request Control Bit 禁用请求控制位

0B Request to enable the WDT

1B Request to disable the WDT

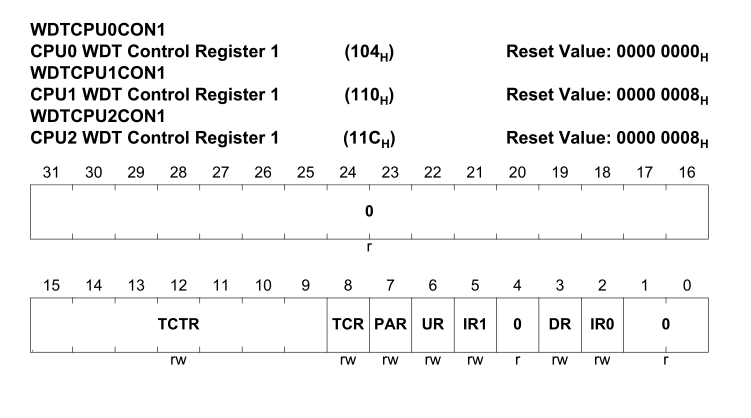

WDTCPU0CON1

主要也是用DR位,跟上面的差不多

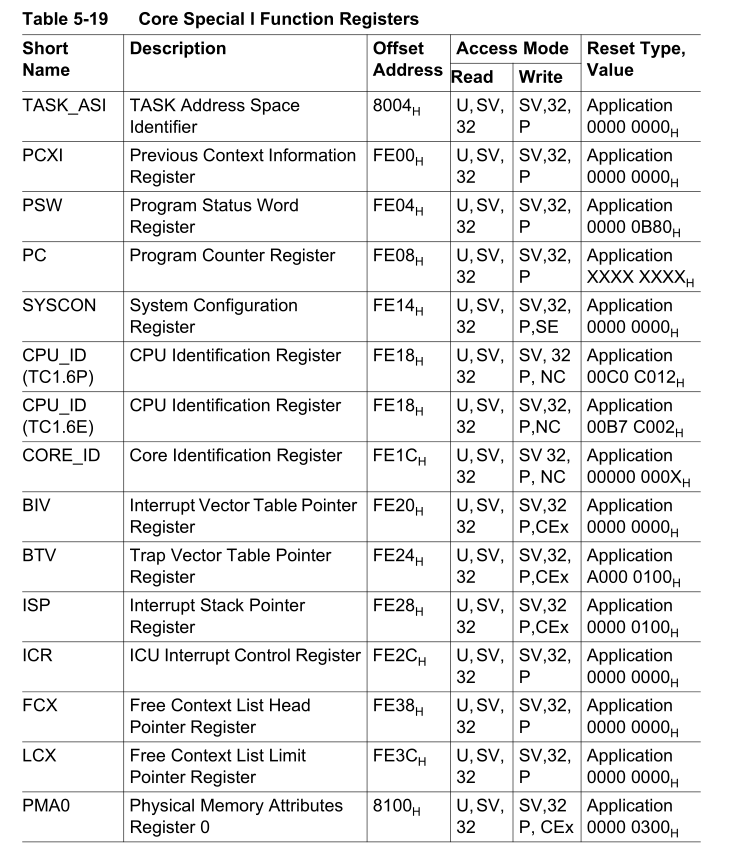

CPU Core Special Function Registers

CPU核心特殊功能寄存器(CSFR)

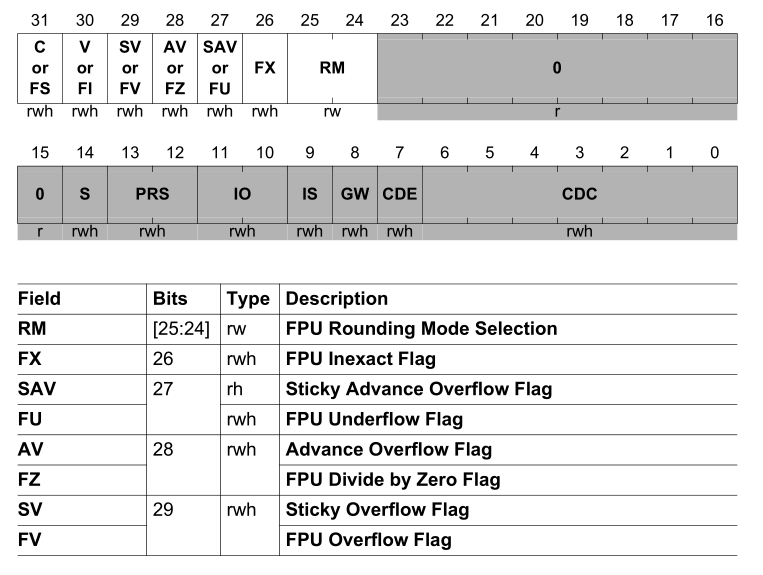

PSW

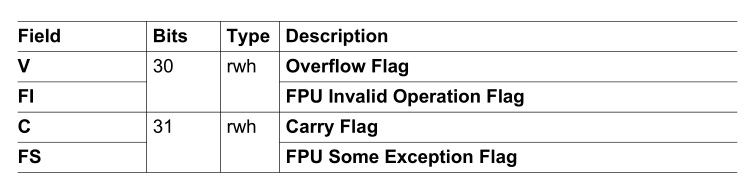

Program Status Word Register (CSFR_Base + FE04H)PSW程序状态字寄存器Reset Value: 0000 0B80H

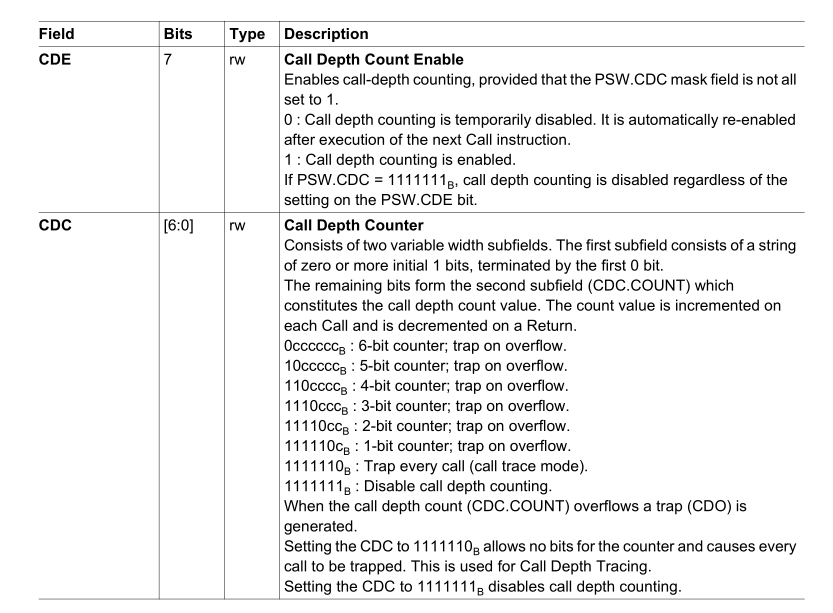

CDC:呼叫深度计数器 Call Depth Counter

两部分组成:0之前的为一部分,0之后的为counter位数,counter在每次调用时增加,返回时减少。

counter溢出时会产生一个陷阱(CDO)

全为1(1111111)时关闭Call Depth计数 1111110时没有counter位,每次都会触发陷阱,用作call trace mode

CDE:Call Depth Counter使能位,前提是CDC位不全为1

0:呼叫深度计数暂时禁用。在执行下一条Call指令后,它会自动重新启用

1:启用呼叫深度计数。

如果PSW.CDC=1111111 B,无论PSW.CDE位上的设置如何,都会禁用Call Depth计数。

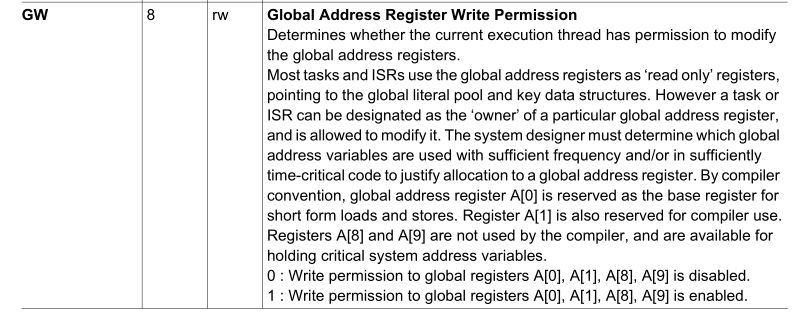

GW:全局地址寄存器写入权限 Global Address Register Write Permission

0 : Write permission to global registers A[0], A[1], A[8], A[9] is disabled.

1 : Write permission to global registers A[0], A[1], A[8], A[9] is enabled.

按照编译器约定,全局地址寄存器A[0]保留为基址寄存器,用于短格式加载和存储。寄存器A[1]也保留给编译器使用。编译器不使用寄存器A[8]和寄存器A[9],它们可用于保存关键的系统地址变量。

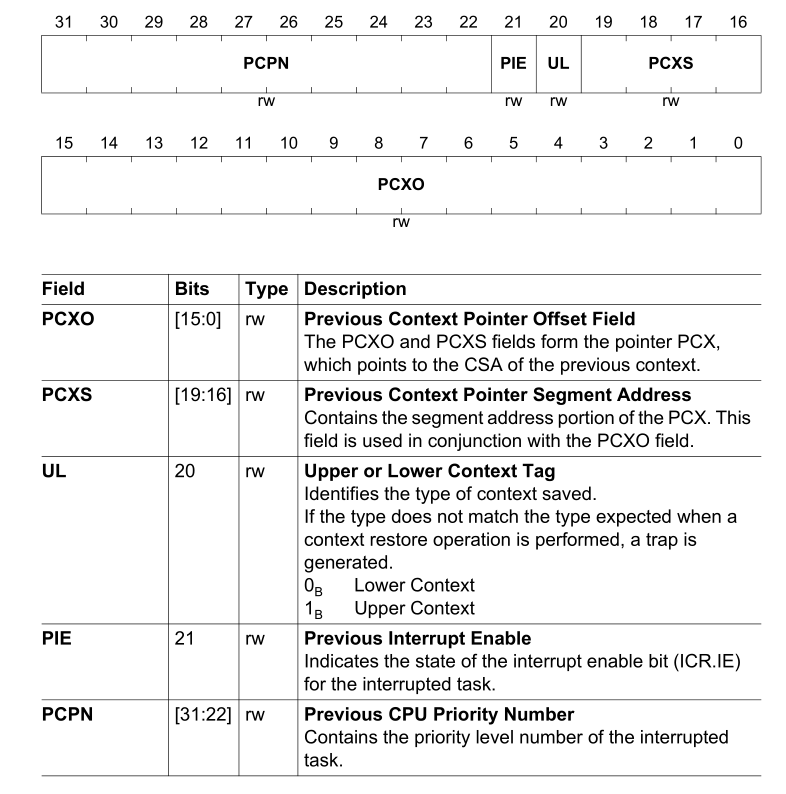

PCXI

Previous Context Information Register 先前上下文信息寄存器 (CSFR_Base + FE00H) Reset Value: 0000 0000H

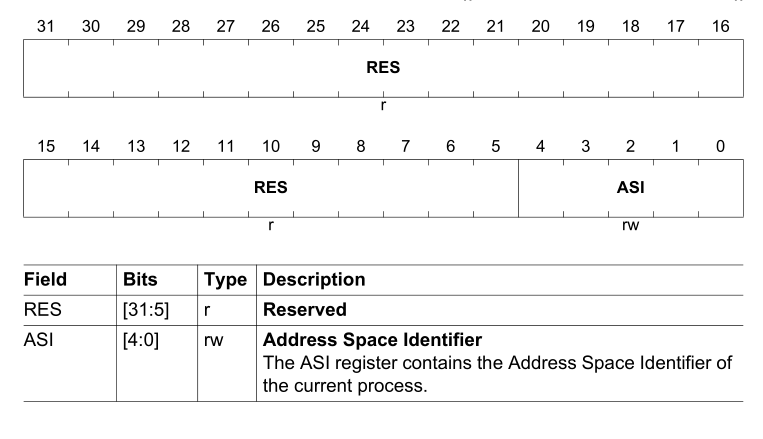

TASK_ASI

Task Address Space Identifier Register(CSFR_Base + 8004H) 任务地址空间标识符寄存器Reset Value: 0000 001FH

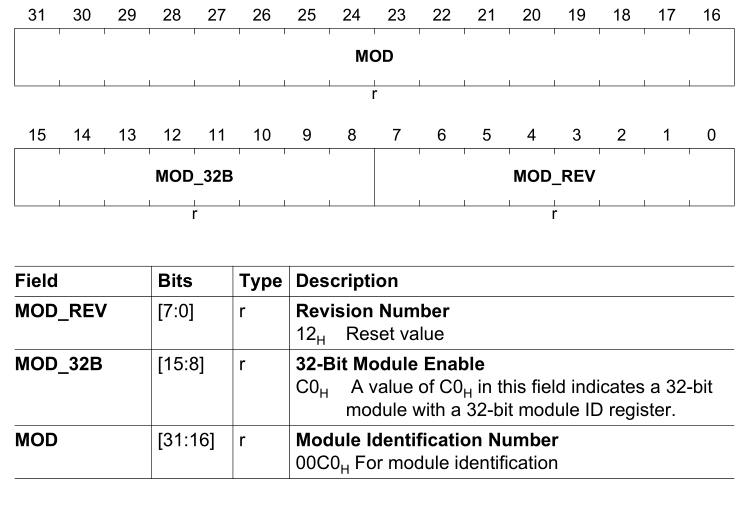

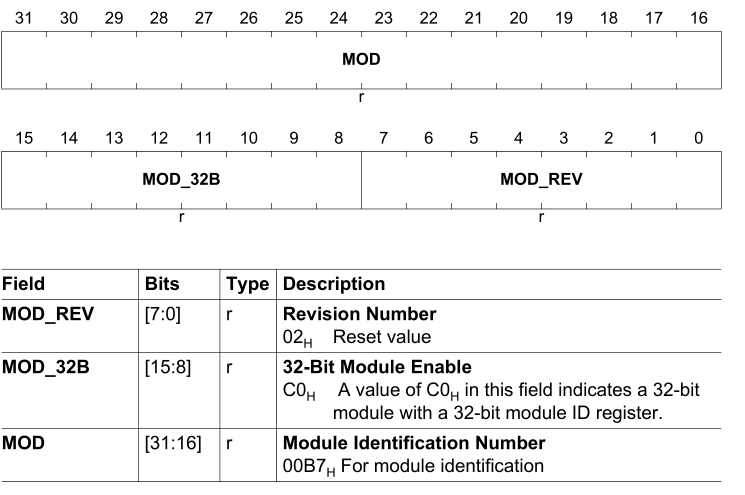

CPU_ID

CPU标识寄存器(TC1.6P)

CPU Identification Register (CSFR_Base + FE18H) Reset Value: 00C0 C012H

(TC1.6E) (CSFR_Base + FE18H) Reset Value: 00B7 C002H

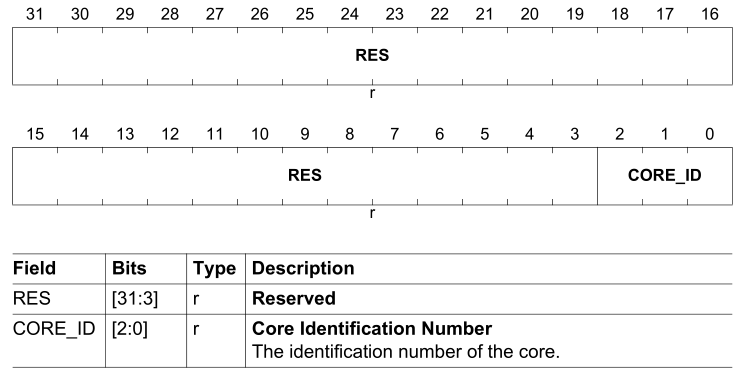

CoreID

Core Identification Register(CSFR_Base + FE1CH) Reset Value: 0000 000XH

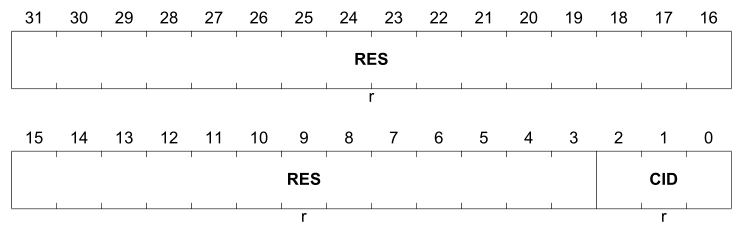

CUS_ID客户ID寄存器

Customer ID register (CSFR_Base + FE50H) Reset Value: 0000 000X

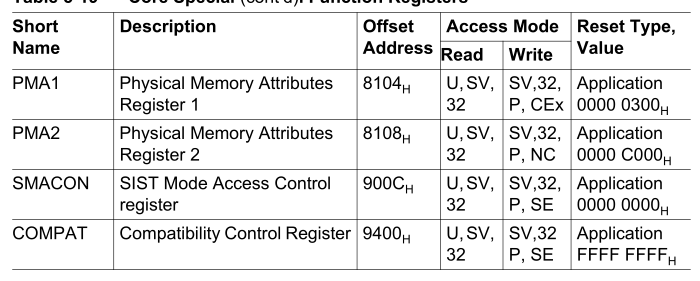

PMA

Physical Memory Attributes Registers物理内存属性寄存器

物理内存属性寄存器(PMA0、PMA1、PMA2)定义物理地址空间中每个段的物理内存属性。寄存器受ENDINIT保护,可以用MFCR指令读取,也可以用MTCR指令写入。

请注意,当更改寄存器的值时,指令和数据缓存都应失效,DSYNC(同步数据)指令应在MTCR(写入数据)之前立即执行,ISYNC(同步指令)指令在MTCR之后立即执行。这是保持处理器内存视图一致性所必需的。

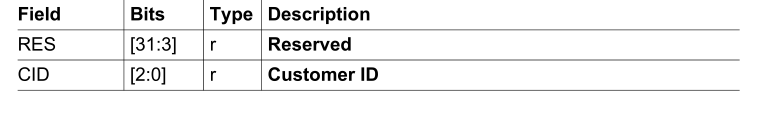

寄存器PMA0定义了物理地址空间中段的数据访问可缓存性。如果寄存器中的位n被设置,那么段n将被视为可缓存的数据访问。

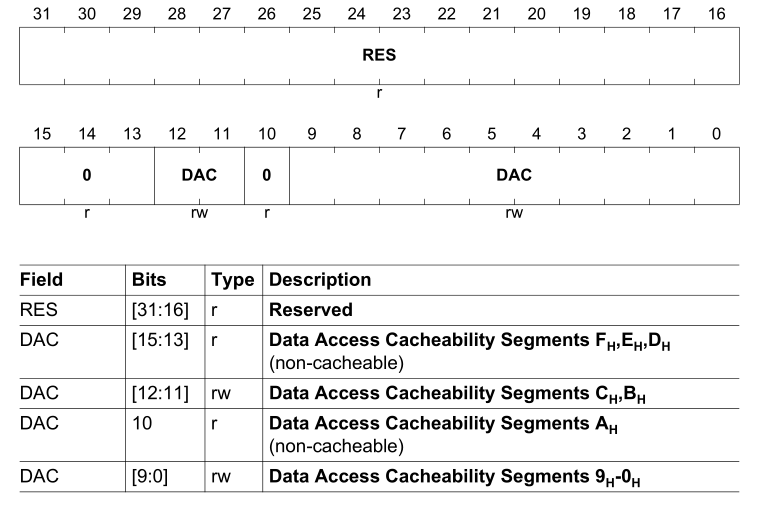

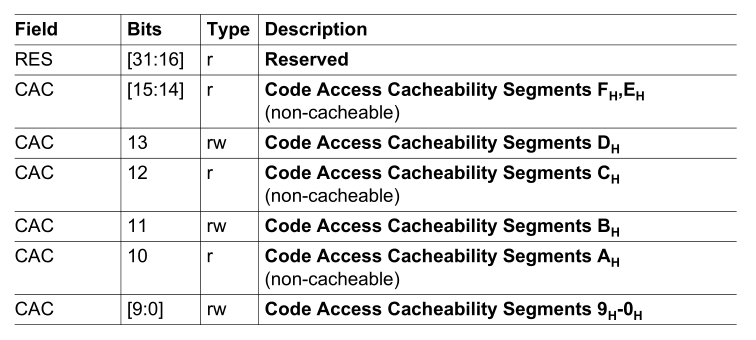

寄存器PMA1定义了段在物理地址空间中的代码访问可缓存性。如果寄存器中的位n被设置,那么段n将被视为可缓存的代码访问。

寄存器PMA2定义物理地址空间中段的外围空间标识符。如果寄存器中的位n被设置,则段n将被视为外围段。PMA2是一个只读寄存器。

寄存器PMA0和PMA1可自由编程,但有以下限制:-在PMA0 Segment-C和Segment[7-CoreID] 中必须具有相同的值。•在PMA1中,Segment-D和 Segment[7-CoreID] 必须具有相同的值。

无论PMA寄存器的设置如何,始终强制执行以下约束。

段-F和段-E被限制为外围空间,因此不可访问

A段被限制为不可缓存内存 non-cacheable

•D段和[7-CoreID]段被限制为不可缓存数据访问。

•段C和段[7-CoreID]被限制为不可缓存的代码访问。

PMA0

Data Access Cacheability Register(CSFR_Base + 8100H) Reset Value: 0000 0300H

数据访问可缓存性寄存器

PMA1

Code Access Cacheability Register(CSFR_Base + 8104H) Reset Value: 0000 0300H

代码访问可缓存性寄存器

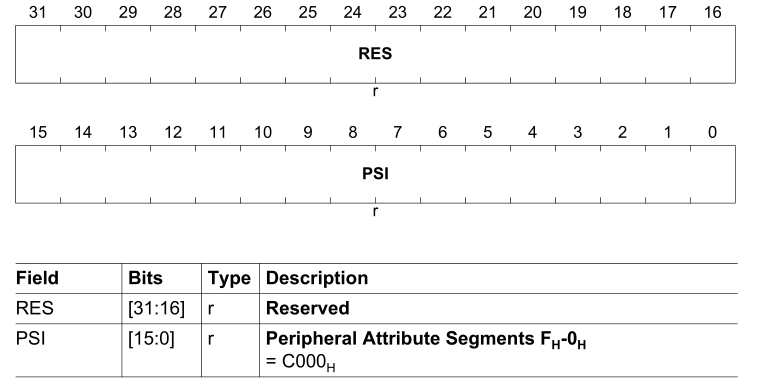

PMA2

Peripheral Space Identifier Register(CSFR_Base + 8108H) Reset Value: 0000 C000H

外围空间标识符寄存器

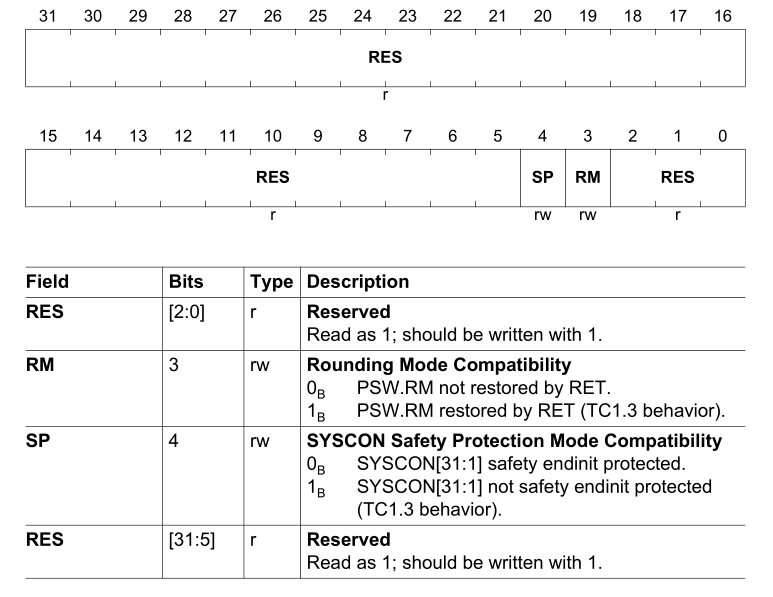

COMPAT

兼容性控制寄存器兼容性控制寄存器(COMPAT)是一种特定于实现的CSFR,允许某些元素向后兼容TriCore 1.3。要强迫的行为。COMPAT寄存器的重置值确保默认情况下启用与TriCore 1.3的向后兼容性。此寄存器受安全保护。

Compatibility Control Register(CSFR_Base + 9400H) Reset Value: FFFF FFFFH

CSFR表

’

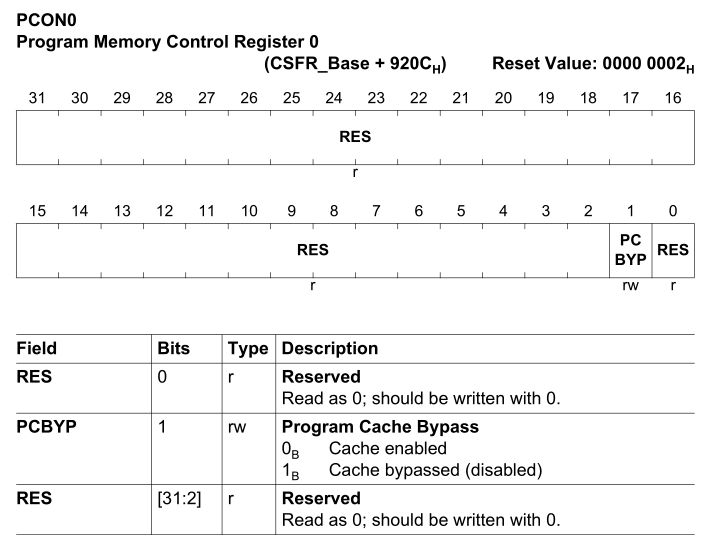

PMI

Program Memory Interface.

三个控制寄存器控制程序存储器接口的操作。

PCBYP写0表示允许程序缓存

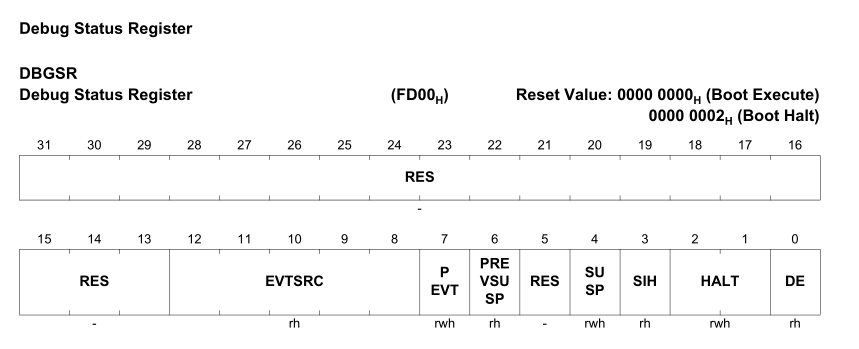

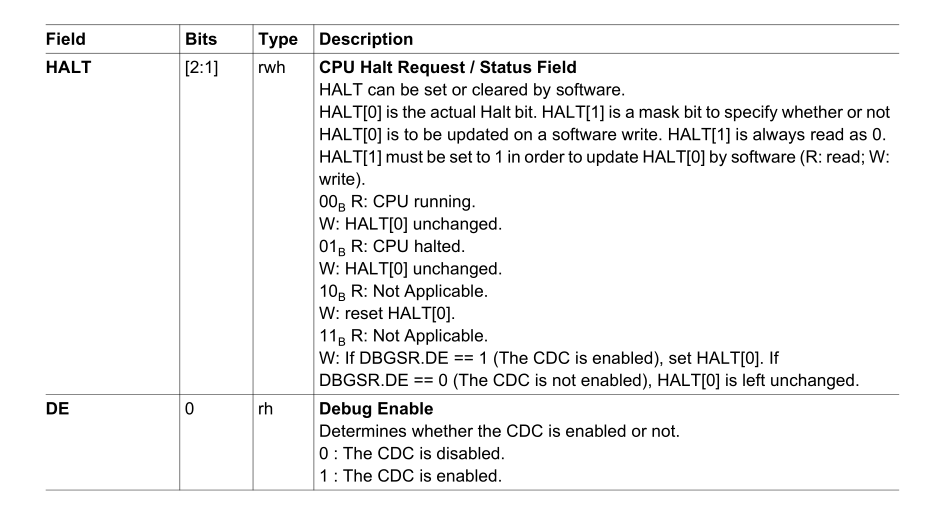

DBGSR

调试状态寄存器,对HALT位写2可以启动CPU

主要也就是对HALT位写2来启动CPU1和CPU2

1735

1735

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?