(一)设计原理:使用计数器count对时钟周期进行0-99循环计数,分别将两位的red,yel,gen的高位作为南北朝向,低位作为东西朝向,置位1为亮。

0-45:东西绿灯亮,红灯和黄灯灭;南北绿灯和黄灯灭,红灯亮。

45-50:东西绿灯和红灯灭,黄灯亮;南北绿灯和黄灯灭,红灯亮。

50-95:东西绿灯和黄灯灭,红灯亮;南北绿灯亮,红灯和黄灯灭。

95-100:东西绿灯和黄灯灭,红灯亮;南北绿灯和红灯灭,黄灯亮。

对上述逻辑关系使用数据流建模语句进行书写。

仿真实现原理:利用initial语句进行变量初始化,对reset置位1,间隔一段时间置位0。

(二)设计方案

module test(clk,reset,red,yel,gre,count);

input clk;

input reset;

output [1:0] red;

output [1:0] yel;

output [1:0] gre;

output reg [6:0] count;

always @(posedge clk)

begin

if(reset)

count <= '0;

else

if(count==7'd100)

count <= '0;

else

count <= count+1;

end

//east-west

assign gre[0] = (count<7'd45)? 1:0;

assign yel[0] = (count<7'd50)? ~gre[0]:0;

assign red[0] = ~yel[0]&&~gre[0];

//south-north

assign red[1] = (count<7'd50)? 1:0;

assign gre[1] = (count<7'd95)? ~red[1]:0;

assign yel[1] = ~red[1]&&~gre[1];

endmodule(三)仿真测试

`timescale 1ns/1ns

module test_tb();

reg clk;

reg reset;

wire [1:0] red;

wire [1:0] yel;

wire [1:0] gre;

wire [6:0] count;

test i1(clk,reset,red,yel,gre,count);

always #50 clk=~clk;

initial

begin

clk=0;

reset=0;

#10 reset=1;

#100 reset=0;

end

endmodule(四)结果分析

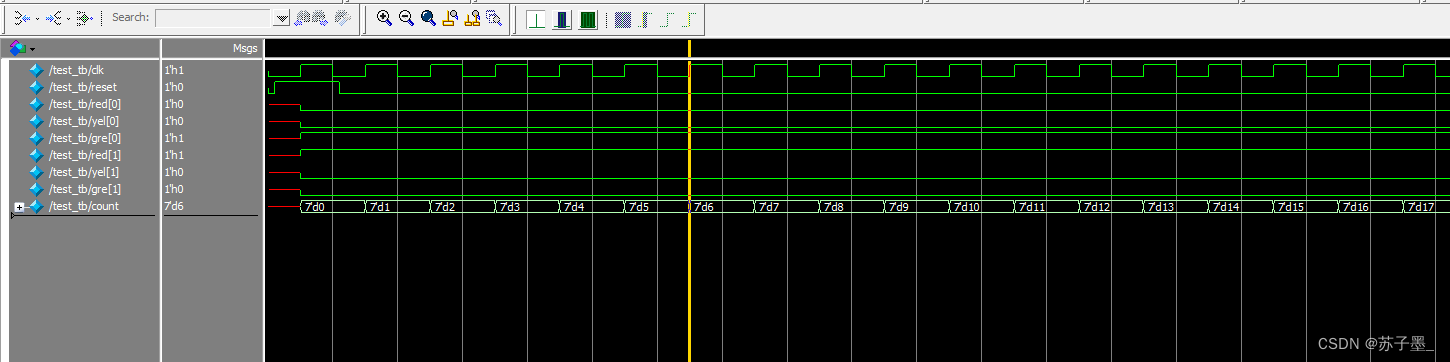

从图中可以看出置位reset功能正常,一开始东西绿灯亮,南北红灯亮。

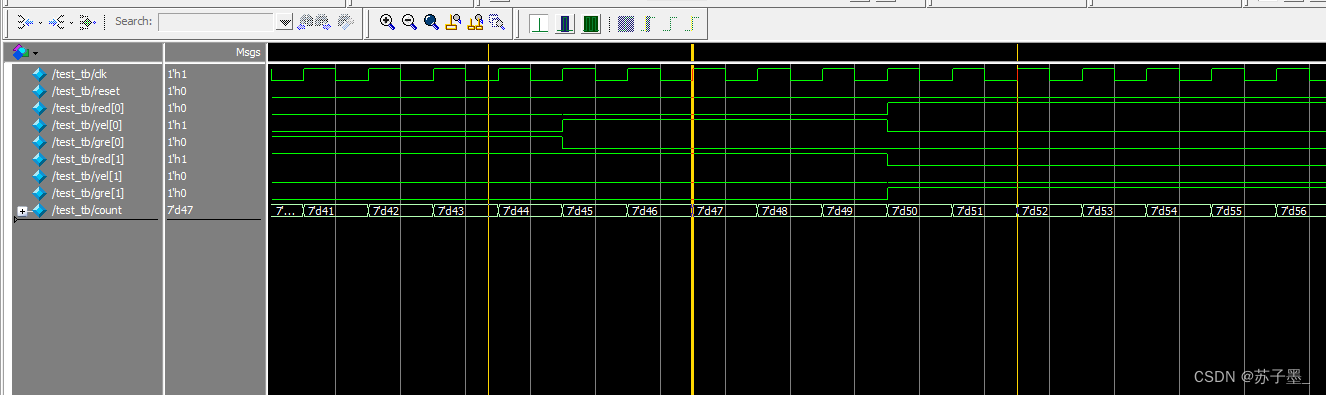

从图中可以看出在45个时钟周期时,开始改变,此时东西变为黄灯,南北仍旧为红灯,在50个时钟周期时,东西变为红灯,南北变为绿灯。

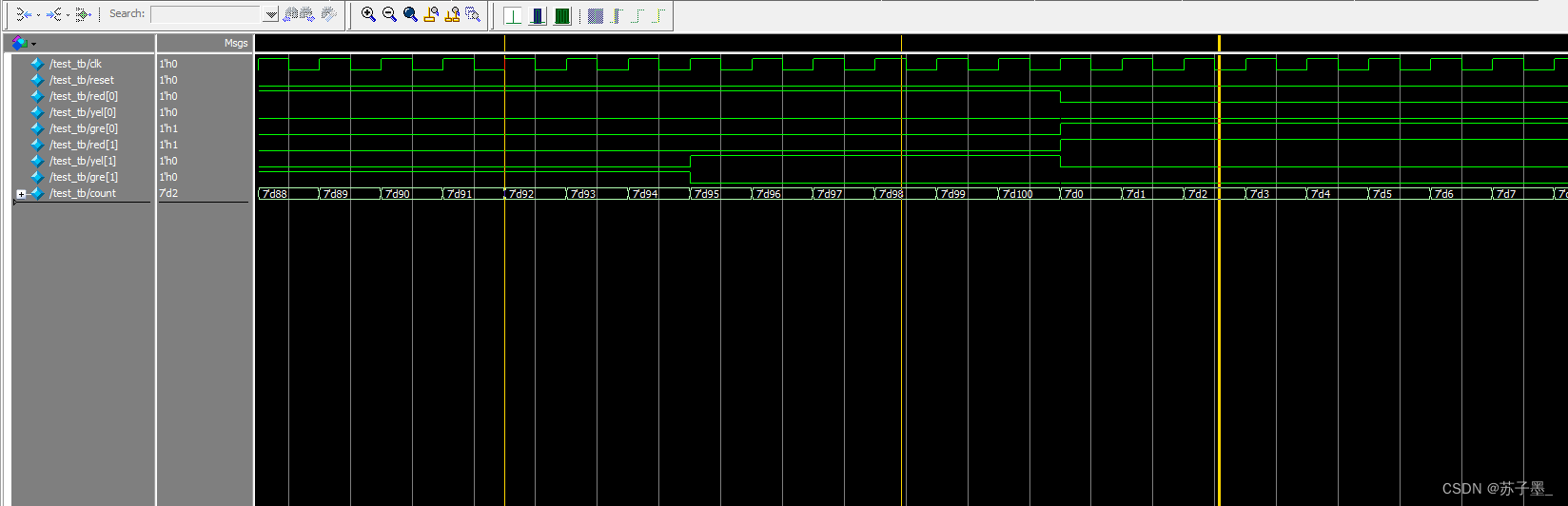

从图中可以看出在95个时钟周期时,开始改变,此时东西仍旧为红灯,但是南北变为黄灯持续5个时钟周期,当计数100时进行循环。

1713

1713

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?