1.时钟设置的步骤分析:

第1步:先选择不使用PLL。让外部24MHz原始时钟直接过去,绕过APLL那条路

第2步:设置锁定时间。默认值为0x0FFF,保险起见我们设置为0xFFFF

第3步:设置分频系统,决定由PLL出来的最高时钟如何分频得到各个分时钟

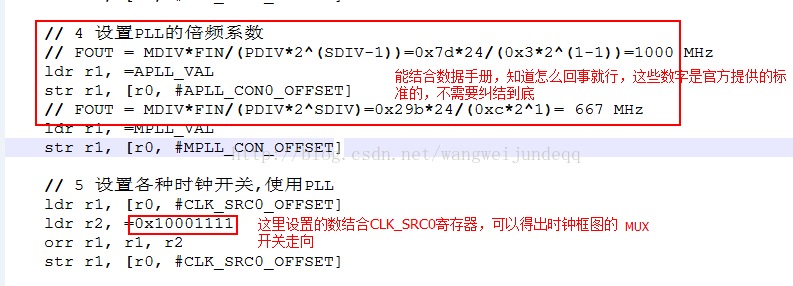

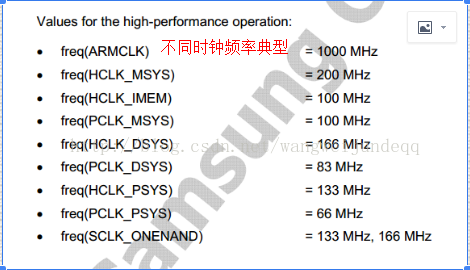

第4步:设置PLL,主要是设置PLL的倍频系统,决定由输入端24MHz的原始频率可以得到多大的输出频率。我们按照默认设置值设置输出为ARMCLK为1GHz

第5步:打开PLL。前面4步已经设置好了所有的开关和分频系数,本步骤打开PLL后PLL开始工作,锁定频率后输出,然后经过分频得到各个频率。

2.下面按步骤来说明各个寄存器的使用:

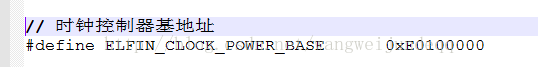

在这里定了一个基地址,通过使用 基地址 + 偏移地址 的方法来定位到我们要访问的寄存器位

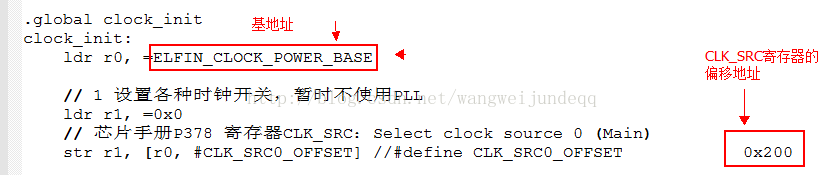

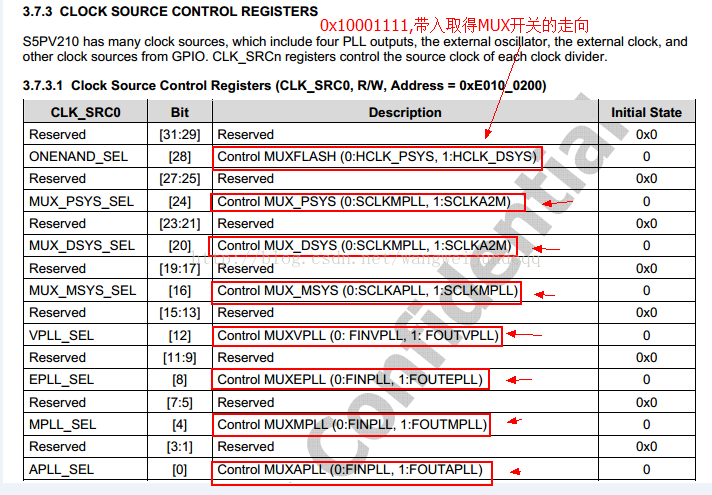

第1步:先选择不使用PLL。让外部24MHz原始时钟直接过去,绕过APLL那条路

CLK_SRC寄存器的设置分析

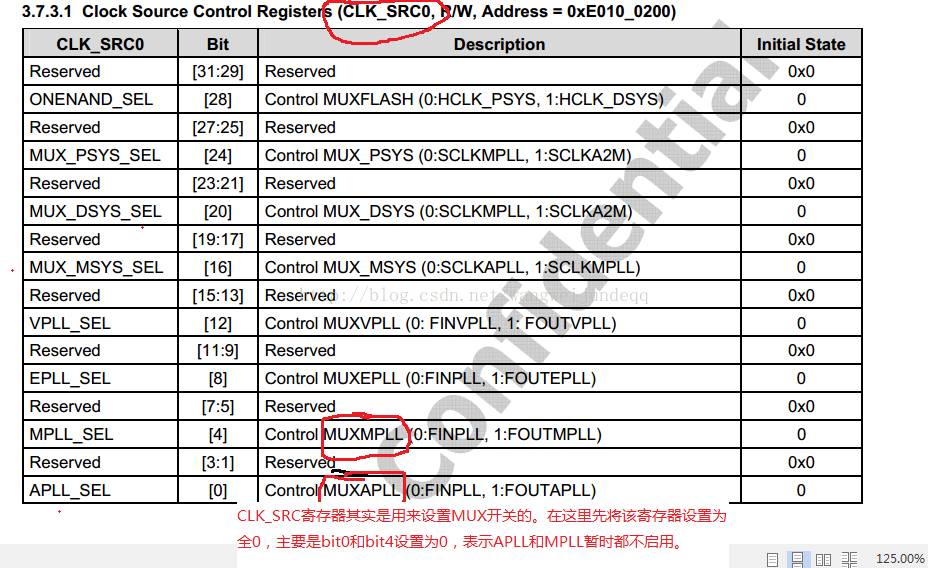

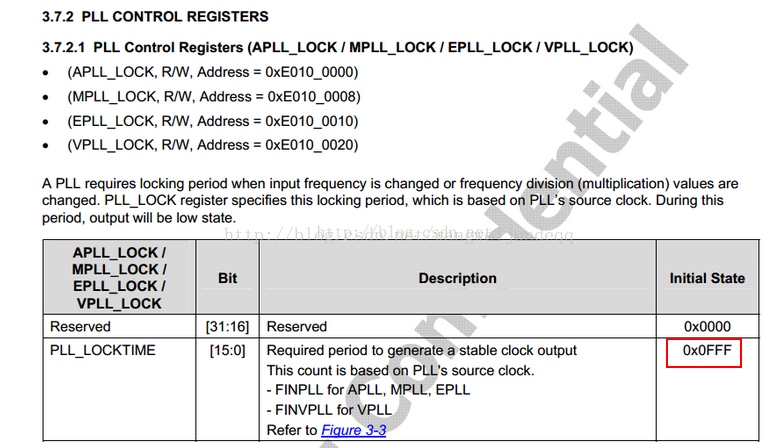

第二步:设置锁定时间。默认值为0x0FFF,保险起见我们设置为0xFFFF

CLK_LOCK寄存器的设置分析

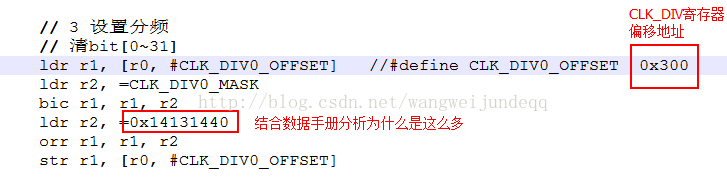

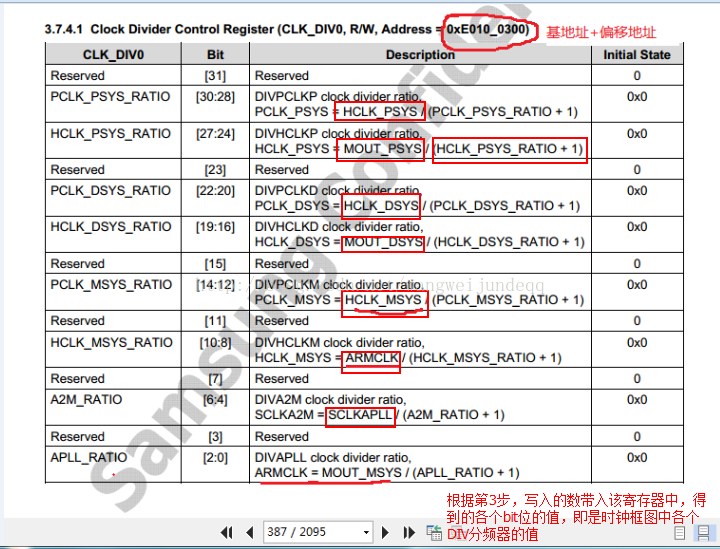

第3步:设置分频系统,决定由PLL出来的最高时钟如何分频得到各个分时钟:

CLK_DIV寄存器的设置分析

结合数据手册CLK_DIV寄存器的设置分析

0x14131440这个值的含义分析:

PCLK_PSYS = HCLK_PSYS / (PCLK_PSYS_RATIO + 1) 这里对应为(1+1)

HCLK_PSYS = MOUT_PSYS / (HCLK_PSYS_RATIO + 1) 这里对应为(1+4)

PCLK_DSYS = HCLK_DSYS / (PCLK_DSYS_RATIO + 1) 这里对应为(1+1)

HCLK_DSYS = MOUT_DSYS / (HCLK_DSYS_RATIO + 1) 这里对应为(1+3)

PCLK_MSYS = HCLK_MSYS / (PCLK_MSYS_RATIO + 1) 这里对应为(1+1)

HCLK_MSYS = ARMCLK / (HCLK_MSYS_RATIO + 1) 这里对应为(1+4)

SCLKA2M = SCLKAPLL / (A2M_RATIO + 1) 这里对应为(1+4)

ARMCLK = MOUT_MSYS / (APLL_RATIO + 1) 这里对应为(1+0)

第4步:设置PLL,主要是设置PLL的倍频系统,第5步:打开PLL,结合一起理解

总结:通过第3步分析数字的代表的各个bit位的数,即是时钟体系框图的DIV分频器中取得值,通过第5步分析数字的代表的各个bit位的数,即是时钟体系框图的MUX开关中取得值

最后,求的不同路线的时钟频率值与官方给的典型值是可以匹配的。

结合寄存器、时钟框图、代码三者综合分析S5PV210的时钟系统如下:

2528

2528

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?