1、复位系统

1.1 上电复位

*复位后单片机的初始状态:*

- RST引脚被设置为复位模式

- 所有的I/O口引脚被设置为输入

- 外围模块被初始化

- 状态寄存器SR复位

- 看门狗激活,进入工作模式

- 程序计数器PC装入0XFFFEH处的地址,从此地址开始执行程序

1.2 上电清除

*产生情况:*

- POR产生时

- 启动看门狗时,看门狗定时器计满

- 看门狗写入错误安全参数值

- 片内Flash写入错误的安全参数

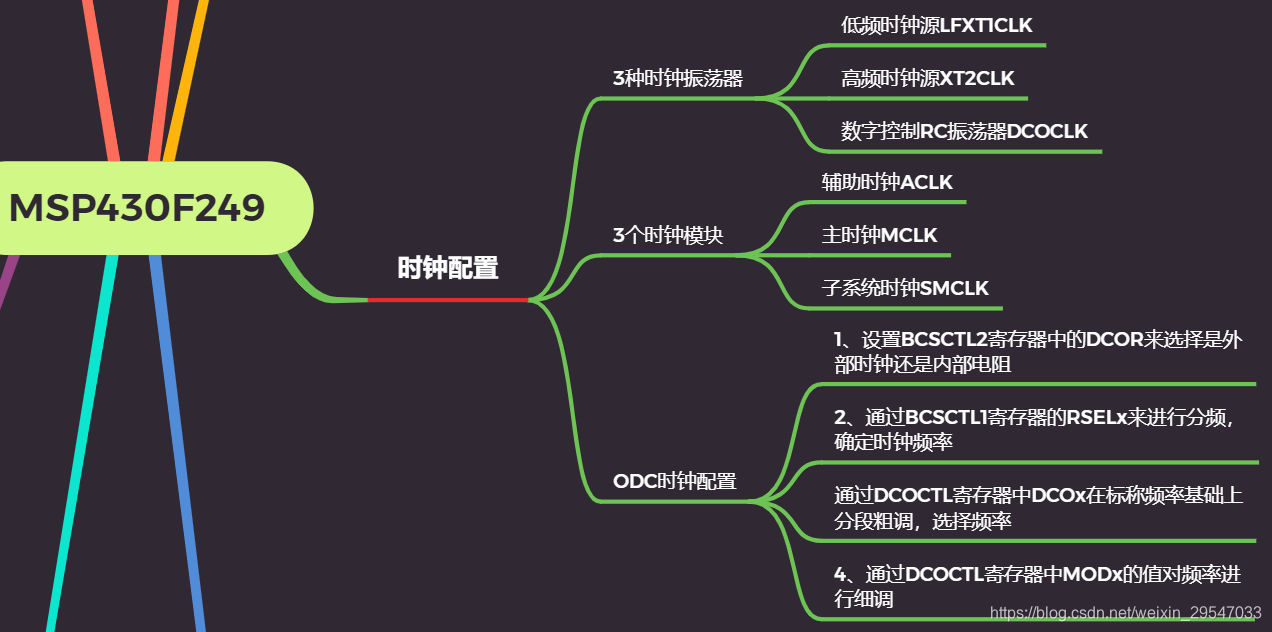

2、时钟系统

2.1时钟知识图谱

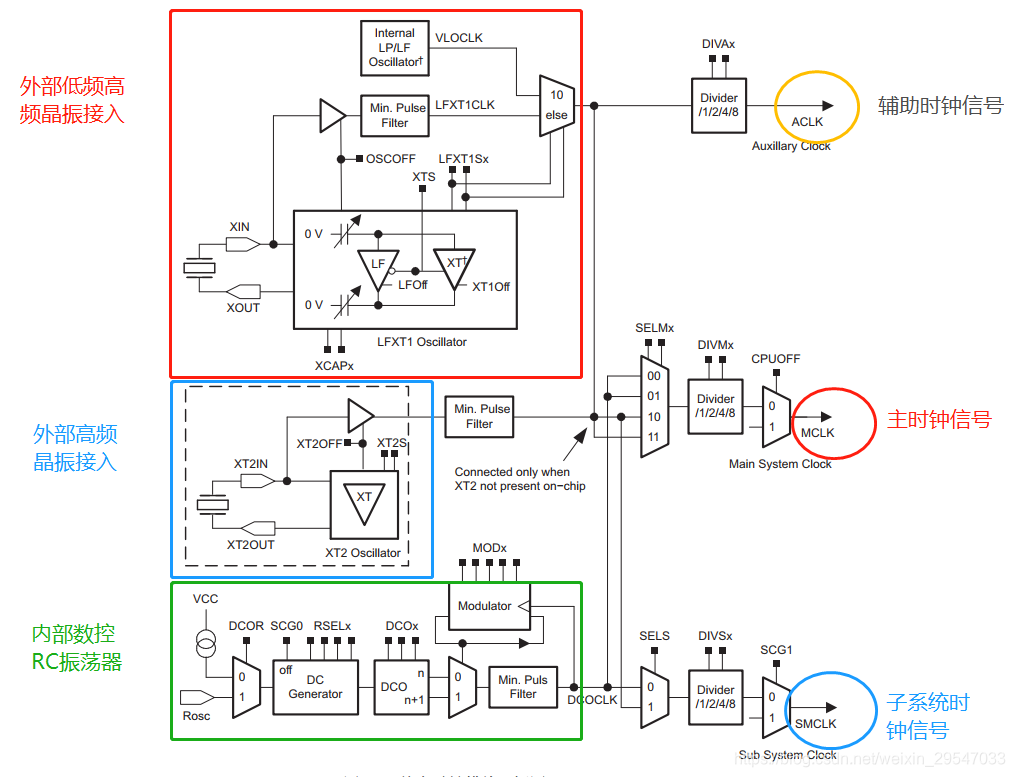

2.2时钟系统结构原理图

2.3 时钟信号描述

通过这些基本的时钟模块,我们可以得到 3 个有用的时钟信号:

[1] ACLK 辅助时钟(Auxillary Clock)

- ACLK 是 LFXT1CLK 时钟源经 1、2、4、8 分频后得到的。

- ACLK 可由软件选择作为各个外围模块的时钟信号,一般用于低速外设。

[2] MCLK 主系统时钟(Main System Clock) - MCLK 可由软件选择来自 LFXT1CLK、XT2CLK、DCOCLK 三者之一,然后经 1、2、4、8 分频。

- MCLK 通常用于 CPU 运行,程序的执行和其他使用到高速时钟的模块。

[3] SMCLK 子系统时钟(Sub System Clock) - SMCLK 可由软件选择来自 XT2CLK 或 DCOCLK,然后经 1、2 、4、8 分频。

- SMCLK 通常用于高速外围模块。

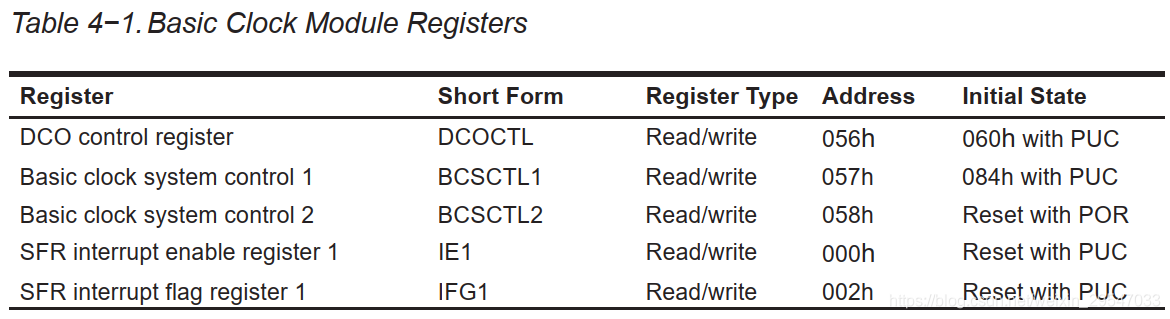

寄存器

2.4 例程

时钟配置例程:

// 设 ACLK=MCLK=LFXT1=HF,将 MCLK 通过 P5.4 输出

#include<msp430x16x.h>

void main(void)

{

unsigned int i;

WDCTL = WDTPW + WDTHOLD; // 停看门狗

P5DIR |= 0x10; // P5.4 输出

P5SEL |= 0x10; // P5.4 = MCLK

BCSCTL1 |= XTS; // ACLK = LFXT1 = HF 模式

do

{

IFG1 &= ~OFIFG; // 清除振荡器失效标志

for(i = 0Xff;i > 0;i--); // 稳定时间

}

while((IFG1 & OFIFG) != 0); // 如果振荡器失效标志存在

BCSCTL2 |= SELM1 + SELM0; // MCLK = LFXT1

While(1){_NOP();}

}

// 时钟设置函数

// 系统时钟设定

// DCO 设置为 3030KHz

// ACLK 为 LFXT1(低频模式)

// MCLK 为 XT2CLK

// SMLCK 为 XT2CLK

void BCSInit (void)

{

DCOCTL = 0x60 + 0x00;

BCSCTL1 = DIVA_0 + 0x07;

BCSCTL2 = SELM_2 + DIVM_0 + SELS + DIVS_0;

}

4258

4258

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?