Cadence设计时一般不主张在PCB文件中更改Logic(PADS的ECO更改),不过Auto Rename仍然是非常实用的功能,按照布局重排位号,可以让PCB的丝印标识更清晰,容易检查,位号易找,方便维修等。下面简略记录一下Auto Rename简单方法。

1. 备份好Rename前的PCB.brd文件及原理图.DSN文件,并确保Capture导入Allegro文件无异常,防止操作失误导致前功尽弃。

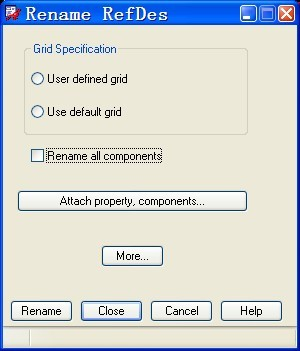

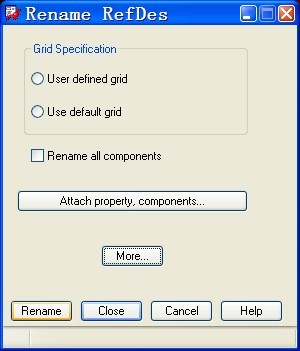

2. Allegro中点击Logic-->Auto Rename RefDes-->Rename,出现如下对话框:

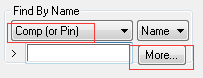

3. 点击Attach property,components,然后在find栏中选择Comp(or Pin),然后点击More(如下图所示),

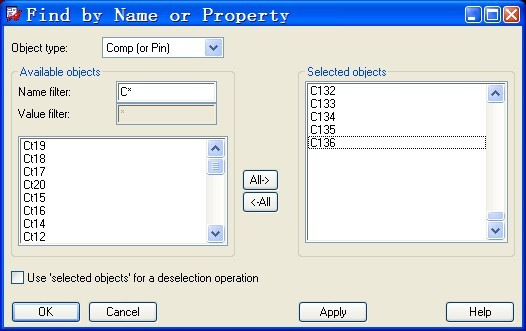

在下面对话框中选择Comp(or pin)

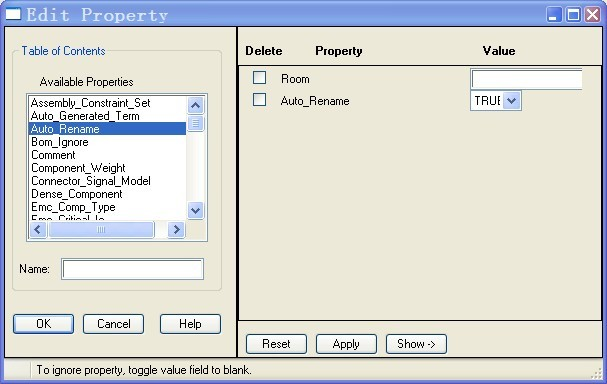

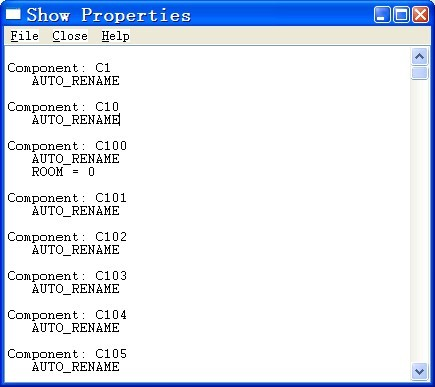

4. Name filter中选择C*,点击按钮,选择到右边框,注意将CON*,CT*单击位号移出。检查没有问题后点击Apply。会弹出Edit property对话框。点击Auto_Rename,再点击Apply,将Auto_Rename属性加到需要C*元件中,Show Properties对话框也会显示AUTO_RENAME属性,如下图所示

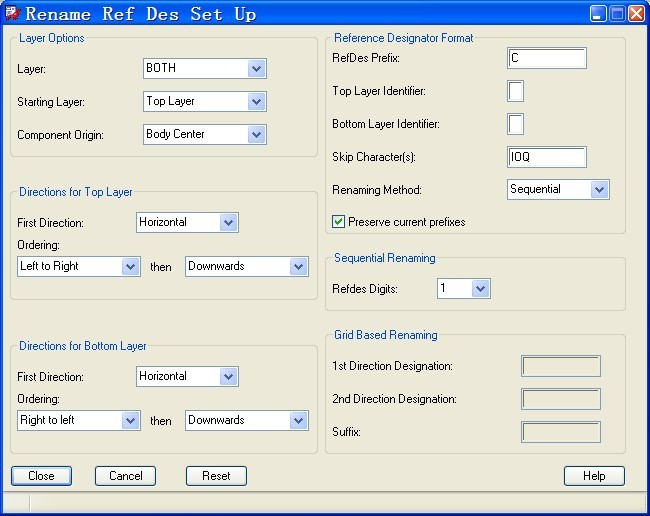

5. 重新激活Rename RefDes对话框,点击More,将RefDes Prefix中*更改为C

并检查Ordering的方向,Left to Righ then Downwards无误后点击Close.

6. 回到Rename RefDes对话框,点击Rename

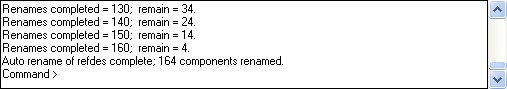

7. 即完成C* Rename。Allegro Command对话框中会提示Rename完成的情况。如下图:

8. 重复上述步骤2-->7, 完成R*, RN*(排阻) D*,Q*,X*, L*, CON*,J*, CN*等元件的Rename。

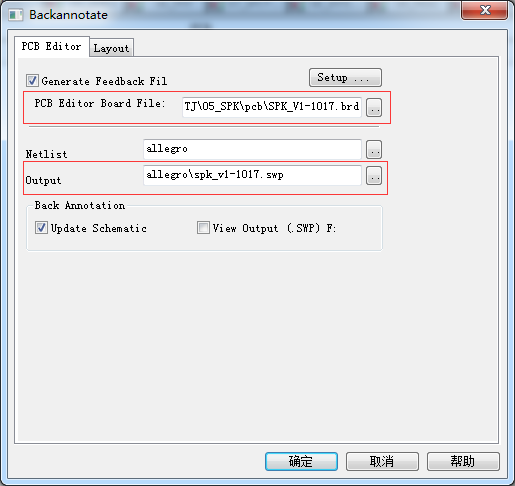

9. 打开原理图工程文件,点击Tools-->Back Annotate,如下图所示。

10. 确认反标PCB文件及目录,反标注文件输出目录。

11. 点击确认,即完成反标,反标完成后保存原理图。

12. 反标注完成后,可在原理图中重新导出生成网表,然后pcb中导入网表,确认反标注正确。

1280

1280

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?