一. SPI总线协议

SPI(Serial Peripheral Interface)接口,中文为串行外设接口。它只需要3根线或4根线即可完成通信工作(这里讨论4根线的情况)。

这4根通信线分别为NCS/NSS(片选信号)、SCK/SCLK(串行同步时钟)、MOSI/SDO(主机输出从机输入,Master Output Slave Input)、MISO/SDI(主机输入从机输出)。

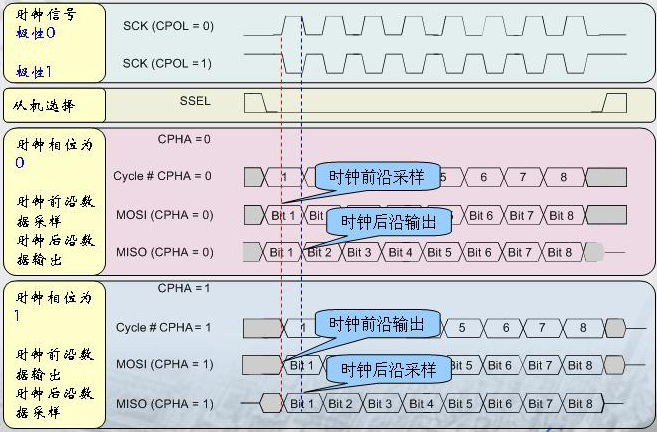

SPI通信有四种方式,由CPOL(时钟极性)、CPHA(时钟相位)的4种组合决定的。CPOL决定总线空闲时,SCK是高电平还是低电平(CPOL=,0,无数据传输时,SCK=0;CPOL=1,无数据传输时,SCK=1)。CPHA决定在数据开始传输时,SCK第几个跳变沿采集数据(CPHA=0,开始传输时,在第一个跳变沿采集数据,第二个跳变沿改变发送数据(即改变MISO或者MOSI线上电平);CPHA=1,开始传输是,在第一个跳变沿改变发送的数据,在第二个跳变沿采集数据)(见图1)。

图1

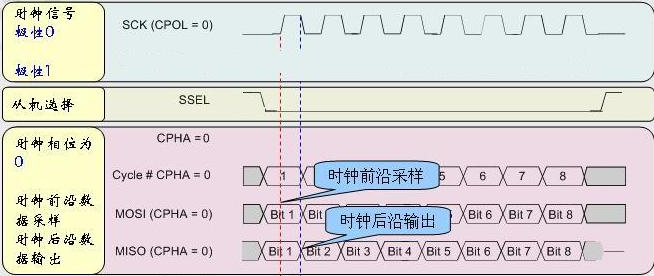

确立可靠通信前,必须保证主从机处于同一种的传输方式,这里为方便起见,专门以CPOL=0,CPHA=0的传输方式进行讨论。

需要注意的是:在CPOL=0,CPHA=0的情况下,主从机都在SCK上跳沿对数据进行采集,SCK下跳沿改变总线电平(见图2)。

本文详细介绍了如何在FPGA中实现SPI从机模块,包括SPI总线协议解析和具体的实现步骤,如确定管脚、SCK跳变沿检测、接收与发送数据的逻辑实现。

本文详细介绍了如何在FPGA中实现SPI从机模块,包括SPI总线协议解析和具体的实现步骤,如确定管脚、SCK跳变沿检测、接收与发送数据的逻辑实现。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

8万+

8万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?