作者:Jack,来源:知乎

据观察,HLS的发展呈现愈演愈烈的趋势,随着Xilinx Vivado HLS的推出,intel也快马加鞭的推出了其HLS工具。HLS可以在一定程度上降低FPGA的入门门槛(不用编写RTL代码),也可以在某些场合加速设计与验证(例如在FPGA上实现OpenCV函数),但个人还是喜欢直接从RTL入手,这样可以更好的把握硬件结构。Xilinx官方文档表示利用HLS进行设计可以大大加速设计进度:

XIlinx官方文档片段

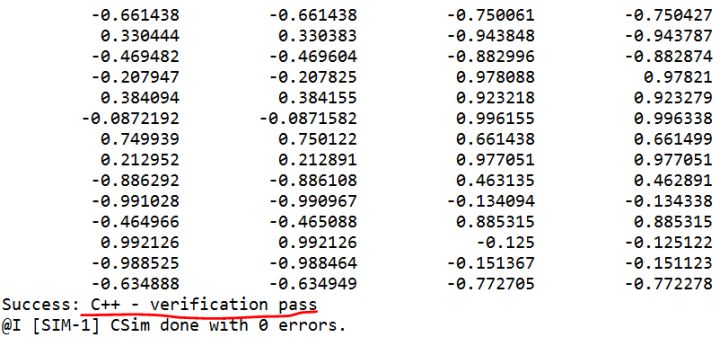

所以为了紧随时代潮流,所以也抽空玩了一下Xilinx的HLS工具,下面把整个过程分享给大家。我这里选择Cordic算法作为我的实现目标。Cordic算法原理很简单,所以这里不再赘述。首先介绍一下Vivado HLS设计流程:

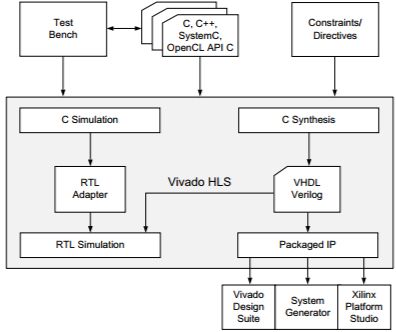

Vivado HLS设计流程

可以看出我们需要做的是完成C/C++设计、Testbench编写以及Constraints/directives的添加。其中Constraints/directives是指利用约束/指令使HLS综合出的RTL代码更符合要求。接着,我们就可以利用HLS进行C层仿真与验证、C/RTL混合仿真与验证以及RTL代码的生成与打包。综上,HLS设计的主要工作内容包括三点:C/C++设计、Testbench设计以及约束的添加。下面就从这三点开始介绍。

一. Cordic算法的C++实现

算法头文件Cordic.h代码如下:

#include #include

#define WA 17

#define FA 14

#define WS 16

#define FS 14

typedef ap_fixeddi_t;

typedef ap_fixeddo_t;

typedef ap_uint flag_t;

const do_t Kn = 0.607252935;

const di_t PI = 3.1415926;

void cir_cordic(di_t alpha, do_t &mysin, do_t &mycos);

头文件的重点是声明数据类型。这里采用HLS中特有的定点数形式,包含ap_fixed.h与ap_int.h即可。由于输入为有符号弧度制(-3.1415~+3.1415),输出为-1~+1,所以定义两种数据精度:

di_t :17bits = 1bit

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

559

559

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?