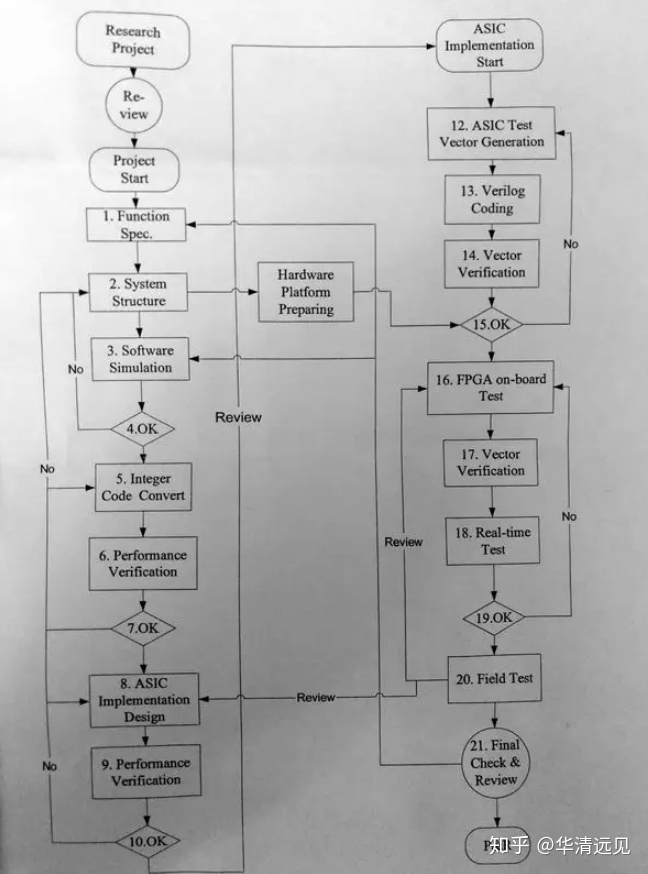

最近收拾书架,翻出一张多年以前的ASIC项目开发流程图,一起回顾一下。典型的瀑布式开发流程:

- 以算法设计为主导

- 算法C代码手工转换为RTL

- RTL与算法C代码生成的测试向量对比进行验证

- 依赖FPGA做大量实时、现场测试

- 适合通信信号处理,音视频处理产品

1. 算法预研

确定了产品方向之后,算法工程师开始进行调研。

要学习研究行业内最新的研究成果、论文,提出创造性的方法来获得最好的性能。要使用真实的测试数据和仿真结果进行评估。最终交付为算法描述的C语言源码。

算法调研结束后需要进行审核(review):确定算法性能,确定系统架构设计,确认是否可以正式立项。审核过程需要算法设计、RTL设计、软件、硬件系统、市场、管理层共同参与。

正式立项时,需要提供功能spec,以及算法C代码功能仿真环境。与此同时,硬件组需要根据项目需求开始搭建硬件FPGA测试平台。

2. 算法优化

接下来进行算法的优化,主要考虑以下几个方面:

- 算法复杂度

- 算法运算量

- 变量精度

- 算法设计以及状态机控制要具有自恢复能力

- 算法代码要足够stable,对于各种滤波器系数和变量要有一定的噪声容忍度。

算法最终确定需要通过审核:算法架构,算

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1474

1474

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?