//来自微信公众号 "数字芯片实验室"

有限状态机(Finite State Machines)是设计中控制逻辑的重要部分。 本节讨论各种类型的FSM编码风格的差异。

同步状态机和异步状态机之间有什么区别?

同步状态机和异步状态机是状态机的两种基本类型。

异步状态机状态在输出信号经过一段时间延时后变化时,时间无法预测。同步状态机状态变化由时钟信号控制。

Mealy和Moore状态机之间的差异。

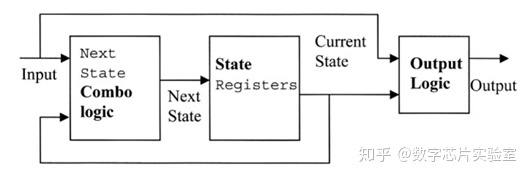

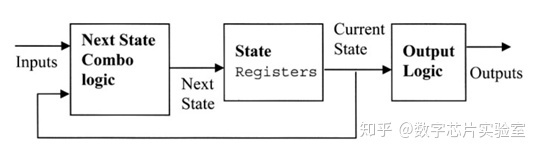

Mealy状态机和Moore状态机是两种常用的状态机编码风格。 这两种状态机的基本框图如下所示:

Mealy状态机输出是当前状态和输入信号的函数。

Moore状态机输出仅是当前状态的函数。

如果输入信号没有被寄存,Mealy状态机可能会有毛刺,并且组合逻辑路径比Moore状态机长。所以,Mealy状态机相对于Moore状态机可能有更低的工作频率。

二进制编码和onehot编码状态机之间的差异。

二进制编码需要更少的触发器,onehot编码需要的触发器和状态机状态一样多。因为输出存在组合逻辑,二进制编码时序没有onehot编码状态机好。在ASIC中,如果输出路径时序不是很关键的话,推荐使用二进制编码。在FPGA中,触发器资源较多,可以使用onehot编码。

1451

1451

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?