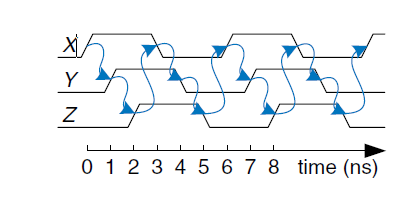

好了,来看上一次的答案分析: 。首先人为地设置初始状态。这里假设x=0,y=1,z=0。当时间0的时候X拉高,经过一个Inverter的延迟(1s)把变化传播给Y同时自己,Y在1s的时候拉高,同理Z在2秒的时候拉高。此时Z而Z的输出则在3s的时候为低电平。看电路就会发现Z和X是连在一起的。。也就是形成了一个 循环回路(Cyclic path)这样导致在3s的时候X自然被拉低,继而影响Y,Z,如此循环往复。。。。这就是一个 周期为6的 环振荡器(ring oscillator)。我们虽然理论上可以用它来做时序计数器,但是注意这里的周期我们不能精确控制,因为是由每一个MOS内禀延迟决定的(。。。用了个高端的词汇,就是内在特有)。

。首先人为地设置初始状态。这里假设x=0,y=1,z=0。当时间0的时候X拉高,经过一个Inverter的延迟(1s)把变化传播给Y同时自己,Y在1s的时候拉高,同理Z在2秒的时候拉高。此时Z而Z的输出则在3s的时候为低电平。看电路就会发现Z和X是连在一起的。。也就是形成了一个 循环回路(Cyclic path)这样导致在3s的时候X自然被拉低,继而影响Y,Z,如此循环往复。。。。这就是一个 周期为6的 环振荡器(ring oscillator)。我们虽然理论上可以用它来做时序计数器,但是注意这里的周期我们不能精确控制,因为是由每一个MOS内禀延迟决定的(。。。用了个高端的词汇,就是内在特有)。

这样逻辑电路里有循环路径的一定会发生我们控制不了的时间因素,更重要的是,大多数这种回路一定都会存在 竞争(race)。大家在前几章做的那个关于Race的时序分析感觉很费劲吧--是的大规模的逻辑回路根本无法进行调整--即使是100块一样的Dlacth你怎么能保证每一个MOS的延迟相同。(虽然这种电路的时序分析很费劲,但是初学者往往就会那么设计,所以最后要给大家留习题哦~~)。我们怎么解决它呢?当然想到的是用额外的外部时钟统一对电路发号施令,这样可想而知,虽然人为地外部控制一定会导致逻辑回路的运行速度减慢,而带给我们的是可控性!我们把不能控制的变为能控制的了,所以无论如何这个Trade off 是值得的。

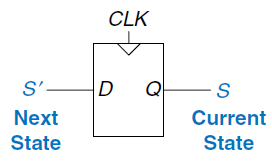

那么我们怎么设计实现这个想法?大家也可以试着想一想。多了时序,我们的逻辑回路回路到底多了什么?这里给出一个普遍的答案:状态(State)。也就是说每一个时刻,整个系统可以被看作为一个状态的集合{S0,S1,S2,。。。。}。这样就可以说在T1时刻我们的某个系统处于S2状态,而又例如我们的系统现在处于S2状态在下一个上升沿的时候会改变到下一个状态--S3状态。那么这个可以把当前状态“刷新”成 新的状态 应该用什么呢?当然是我们的寄存器咯。也就是D FlipFlop。 给个示意图: 。这样 同步时序逻辑回路 就可以被定义为:

。这样 同步时序逻辑回路 就可以被定义为:

1.整个回路中必须有一个寄存器存在

2.所有寄存器接受相同的时序

3.每个循环回路上必须存在一个寄存器

4.回路只由寄存器和组合回路构成

--话说定义有什么用?还记得之前讲的组合逻辑回路的定义么?如果在一个很大的系统里面,你只要依照这些特征去分析,马上就能知道那一块东西是干什么用的。这里与其说是定义,不如说是特征。

而异步时序回路顾名思义寄存器可以接受不同的时序--当然生活中比同步时序更常用到,而设计起来更复杂。所以这个要在这个系列的高级篇降到。目前大家只要考虑 SYNCHRONOUS SEQUENTIAL CIRCUITS就好咯。

那么下面就是承诺给大家的习题还有一个简单的附加题~:

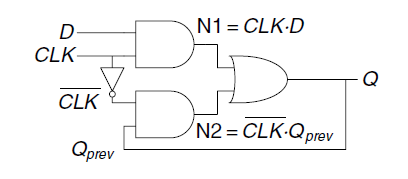

1.分析下面的逻辑回路的作用,画出时序图(提示:分析对了的话会发现Race Condition 的哦)。

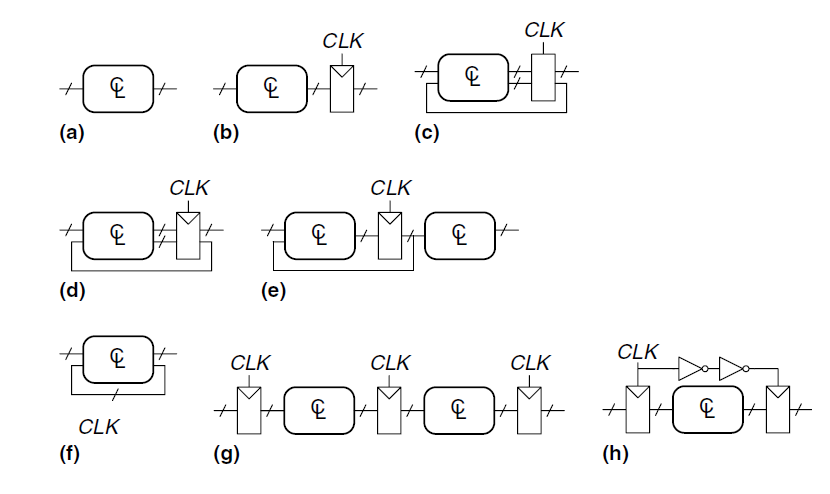

2.猜猜看,把下面的所有是 Sequential Circuit 的挑出来:

好了,下一次我们进入初学者的地狱--FSM(有限状态机)初步。为什么叫地狱呢?因为大多数搞单片机,FPGA的菜鸟们都对这个不能灵活应用,综合性比较强(组合回路+寄存器+时序分析),而实际应用中基本都是状态机--所以是基础中的基础,重点中的重点。一定要牢固掌握这节以前的所有知识否则后果自负~~(其实就是会导致自己失去信心),这样我才能帮助大家通过地狱~。

转载于:https://blog.51cto.com/physic/1319913

2194

2194

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?