CMOS和TTL门电路的对比

- TTL门电路的输入端悬空时相当于高电平输入输入端接有电阻时其电阻阻值大于1.4K时该端也相当于高电平电阻值小于0.8K时该端才是低电平. ------而CMOS逻辑门电路输入端不管是接大电阻还是接小电阻该端都相当于低电平即地电位.

- TTL电路输入阻抗较低.COMS电路输入阻抗很高.

- TTL对于与非门可以直接接电源vcc或是接个1--10k电阻接电源.若前级驱动允许可将闲置的输入端悬空(相当于1).在外界干扰很小时,与非门的闲置端可以悬空.或非门不用的应接地,与或门中不适用的与门至少有一个输入端接地.---------CMOS端不允许悬空.

- 在COMS和LSTTL门电路中,输入端接高电平1同接电源VDD逻辑等效。√

- LSTTL门电路和COMS门电路的温度特性同样好。×

- 所有门电路都会有传输延迟时间。√

- VIL和VOH越低,抗干扰特性越好。×

- 当输入为低电平时,LSTTL和COMS门电路输入端没有电流流出。×

- 在COMS和LSTTL门电路中,在输入端接低电平0同接地逻辑等效。√

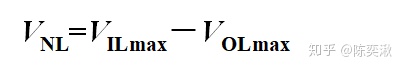

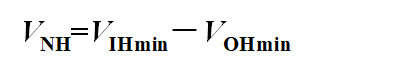

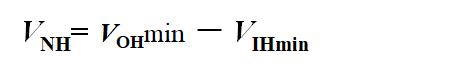

噪声容限

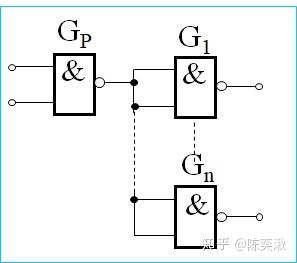

TTL门的扇出系数

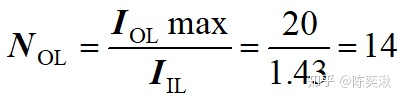

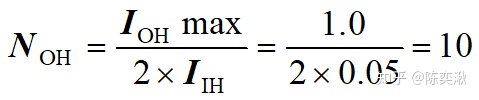

例:已知门电路的参数

试求 门 GP 的扇出系数No应为多少?

N应选取{ NOL,NOH}min,即10

目前更新指路

OD门 | OC门 | CMOS三态门 | TTL三态门blog.nowcoder.net

1908

1908

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?