移位寄存器应用举例 || 可编程分频器 || 串行加法器 || 串行累加器 || 数电

前面介绍了移位寄存器,这一节介绍移位寄存器的几个应用例子。

1 可编程分频器

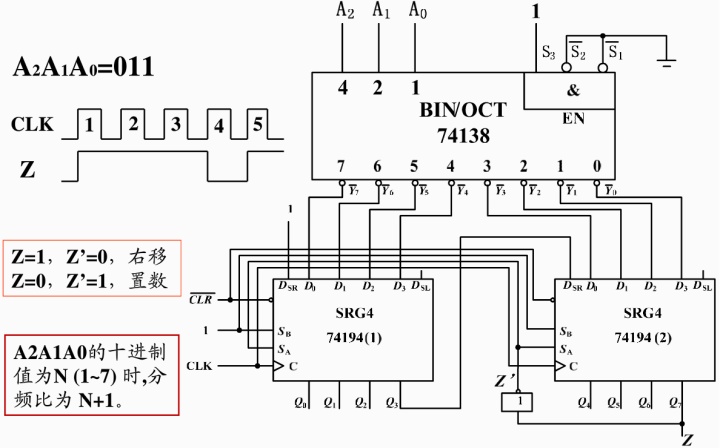

如下图,当3-8译码器的地址输入A2A1A0给定为011时,输出Z的频率与时钟CLK的频率之间,有某个分频关系,下面来分析一下这个分频关系。

初始状态Q7Q6Q5Q4Q3Q2Q1Q0=00000000,

此时Z=0,Z'=1,即SASB=11,寄存器处于置数模式,

此时寄存器会置入译码器的输出Y7Y6Y5Y4Y3Y2Y1Y0=11110111,

寄存器的状态变为Q0Q1Q2Q3Q4Q5Q6Q7=11110111,

此时Z=1,Z'=0,即SASB=01,寄存器处于右移模式,右移3次后再次变为置数模式,再来一次时钟脉冲后置数,寄存器的状态回到Q0Q1Q2Q3Q4Q5Q6Q7=11110111,这个过程中,每经过3+1=4个时钟周期,Z端的输出脉冲循环一个周期,形成一个4分频分频器。

以此类推,可以得到下图左下角的结论。

2 串行加法器

下面来看移位寄存器应用的第二个例子,串行加

本文通过移位寄存器的应用,详细介绍了如何设计8位可编程分频器,以及串行加法器和串行累加器的工作原理。在可编程分频器部分,阐述了如何利用3-8译码器实现不同分频比。接着,讨论了4位串行加法器的电路设计和工作流程。最后提及了串行累加器的结构与功能。

本文通过移位寄存器的应用,详细介绍了如何设计8位可编程分频器,以及串行加法器和串行累加器的工作原理。在可编程分频器部分,阐述了如何利用3-8译码器实现不同分频比。接着,讨论了4位串行加法器的电路设计和工作流程。最后提及了串行累加器的结构与功能。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

2800

2800

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?