数字IC设计实现之hierarchical flow系列(一)

文章右侧广告为官方硬广告,与吾爱IC社区无关,用户勿点。点击进去后出现任何损失与社区无关。

最近这段时间小编又比较忙起来了,今天抽空来咖啡厅码字来了,刚到时脑子一片空白,不知道要分享些什么(项目结束后将会在知识星球上分享数字 IC 设计实现 Tapeout 前要review的那些 checklist)。突然间想起来有个星友希望小编分享些数字 IC 设计实现 hierarchical flow 的相关内容。考虑到现在大都采用这种方式来做 design 和实现,那就选这个 topic 了。限于篇幅和时间限制,今天只分享逻辑综合部分和布局布线部分,下期会继续分享寄生参数提取,静态时序分析和物理验证等过程。

2019 年数字 IC 后端校招笔试题目(附数字后端培训视频教程)

Flatten Or Hierarchy

随着工艺制程的不断升级,芯片的规模越来越大。以小编最近流片的 GF22 FDSOI 工艺的一颗芯片为例,整个芯片 instance 数量高达 9000 万,其中 GPU 模块的 instance 就高达 1800 万。对于这样的 design,如果采用 Flatten 方式来设计实现,只需对设计进行一遍逻辑综合,产生一个 gate level netlist,然后进行后续的 Synthesis, place&route,静态时序分析等工作。但是对于这种规模的 design,你敢用 flatten 方式进行设计实现吗?先不要说整芯片了,就整个 GPU System 都不可能用 Flatten 方式来设计实现。

如果你不相信,请大胆去试试跑一个这样规模 deisgn 的综合或者 place。如果你能跑出 placement 的结果,小编只能对你竖起大拇指,为你点赞,大写的赞!

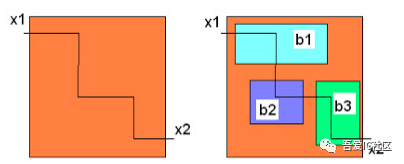

因此,针对这种规模比较庞大的设计,我们需要将这样的 design A 进行切分,切分为 Design1,Design2,…,Design N。然后采用 Hierarchy 方式对 design 进行 N 次逻辑综合,布局布线,寄生参数提取,静态时序分析,物理验证等工作。

Why hierarchy?

- 设计规模

上面讲述过了,如果设计规模太大,如果用 flatten 方式来做设计实现,基本上是跑不出来的。

- Timing Signoff

进行 flatten timing signoff 时,Prime time 本身的 runtime 会非常慢,而且极度消耗内存,特别是当芯片时钟结构比较复杂,对时序要求比较高的时候,经常会出现 Prime Time 跑不出结果的情况。

如果采用 hierarchy 方式,各个阶段的工作都是并行做的,一方面大大节省了 run time,加速 timing signoff 进程。另外一方面各个子模块可以单独 timing signoff,特别是当某个模块对时序要求比较高,但是模块大小又不大时,此时该模块一天可能可以进行两三轮 hold fixing,而别的模块可能一天只能做一轮 hold fixing。这样切分出来后可以有更多的时间对模块 timing 进行细调优化。

数字 IC 设计实现之 hold violation 修复大全

听说 Latch 可以高效修 hold 违例(Timing borrowing 及其应用)

- 应用需求

在某个时刻,设计可能需要对芯片中的某部分逻辑进行 power down 操作,如果此时采用 flatten 方式进行设计实现,势必需要额外编写 upf,需要对 powerplan 进行重新规划,powerplan 需要对整芯片划分为两个区域。这样就给数字 IC 后端工程师添加额外的工作量。

数字 IC 后端设计实现 floorplan 及 powerplan 规划

此时如果对设计进行切分,将需要 power domain 的逻辑单独切出来,做成一个 power domain。那么整个数字 IC 设计实现 flow 就非常流畅,省心省事。

如果在数字 IC 后端实现阶段发现某个模块,含有特别多的高 pin density cell,导致绕线非常困难。此时也可以同前端工程师进行沟通协商,是否可以将该模块单独切出。但是切分时需要考虑接口处的 timing。

如何用工具自动修复数字 IC 后端设计实现绕线后的 Physical DRC?

Hierarchy 方式实现 IC Flow

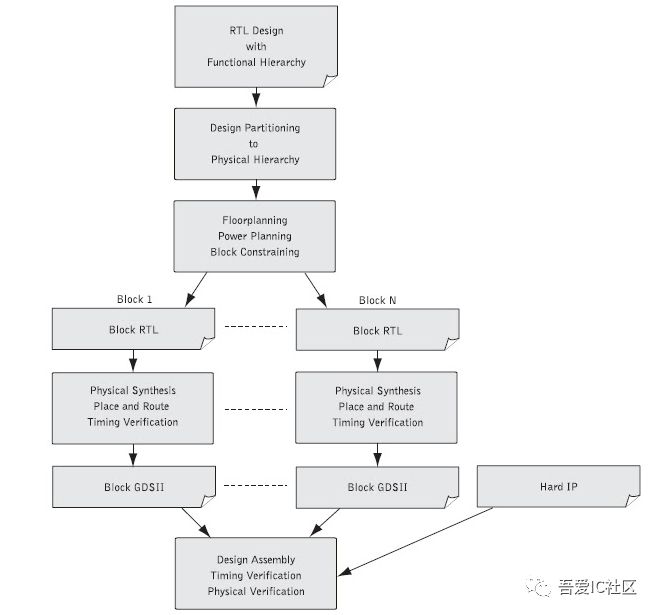

数字 IC Hierarchical 方式设计实现流程大致如下图所示,整个过程涉及前端设计集成,逻辑综合,布局布线,寄生参数提取,静态时序分析,物理验证等环节。限于篇幅今天先分享一部分内容。

- 逻辑综合

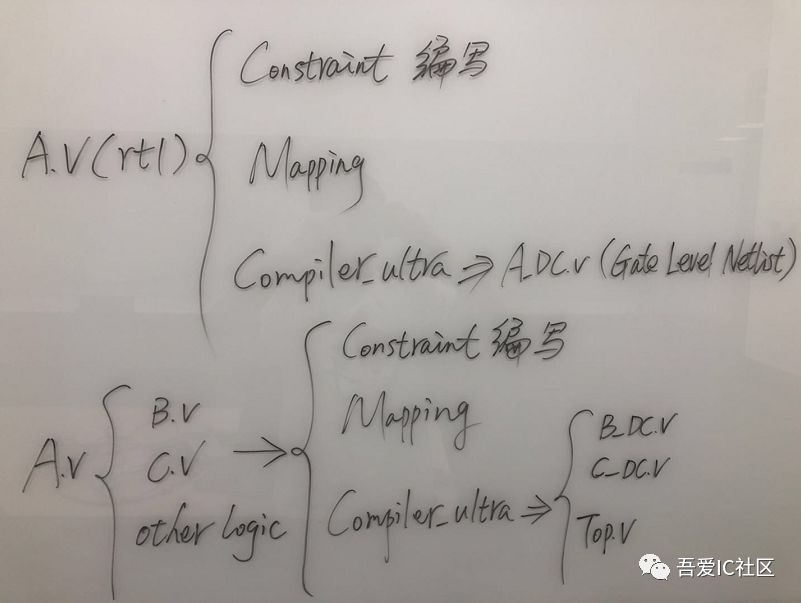

逻辑综合阶段的流程如下图所示,其中上半部分为 flatten 综合方式,下半部分为 hierarchical 综合方式(DC 综合)。如果是采用 DCT 综合,则还需要提供模块 B 和模块 C 的 ETM model,Fram View 以及工艺的 tluplus 文件。关于如何产生子模块 B,C 的 ETM 和 Fram View,以及对应的生成脚本,请移步小编知识星球查看。

教你轻松调 DCT 和 ICC 之间 Timing 与 Congestion 的一致性

- P&R 布局布线

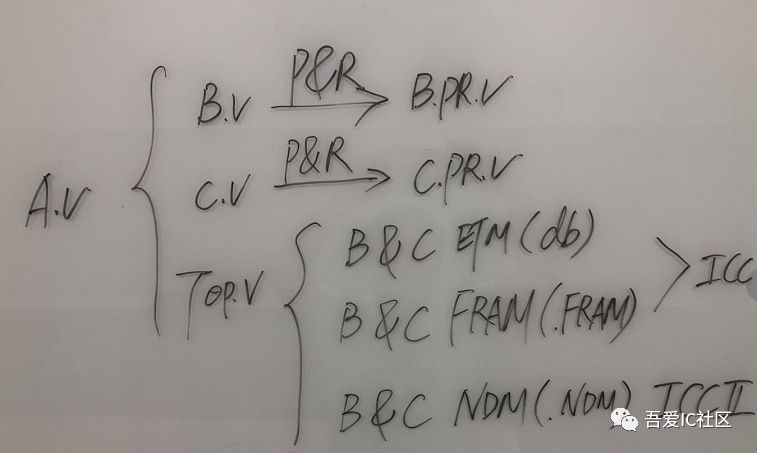

布局布线的 hierarchy 实现流程如下图所示。需要分别对子模块 B 和 C 进行布局布线,然后生成对应的 post layout 的 etm,最后 load 进 B 和 C 的ETM 和 FRAM,进行顶层 TOP 的布局布线。其中使用 ICC2 flow 需要用到NDM(New Data Model)。产生 NDM 时需要用到 DB 和 LEF 文件。关于 LEF 写出方法,NDM 制作方法和脚本,之前已经在知识星球分享过,需要的朋友可以前往下载查看。

需要特别注意的是,在这种 hierarchy 实现方式中制作 Fram View 时,千万别漏提取 database 中的antenna 和绕线信息,否则 ICC 或者 ICC2 在 route 阶段可能无法看到内部绕线情况,从而容易出现接口处的天线效应(antenna effect)。

教你轻松玩转天线效应 (Process Antenna Effect)

Hierarchical design flow 的优点

-

数字后端 P&R(Place&Route)实现时能够有效控制好每个子模块的实现过程,因为 run time 可以大量减少,而且不同子模块可以并行实现

-

将设计中新添加的模块单独切出来,预防因为新设计模块存在 bug 而导致大规模 block 重做,大大降低项目风险

-

解决绕线问题(为什么?大家好好思考,涉及 logical hierarchical 和 physical hierarchical 的概念)

-

寄生参数抽取(RC Extraction)时间大量减少

-

加速 Timing Signoff 进程

Hierarchical design flow 的缺点

- Interface timing buget

P&R 实现时,需要考虑 IO 接口的 timing(预留 timing buget),防止因接口相关的逻辑没有进行充分的优化而导致的 timing violations。至于预留多少 timing margin,留给大家思考。这个技能是数字后端工程师最基本的技能之一。各大公司的面试经常也会问到这个问题。

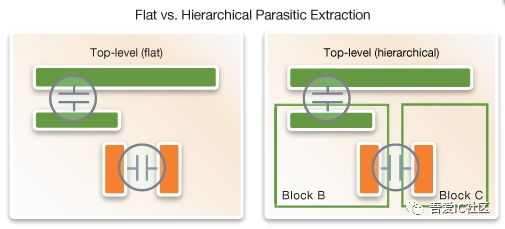

- RC 准确性

第一,dummy 的插法往往是 flatten 抽取出来的。如果是 hierarchical 的 rc extraction,模块接口处的 RC 是否可信

第二,相邻子模块边界处的 RC 是否准确

- Timing 的准确性

比如一个 chip 中,有的模块频率要求比较低,我们想用 7Track 的 libray 来实现。而对频率要求比较高的模块,我们则可以用 9Track 甚至 12Track 来实现。

那么问题来了,如果有一条 path,startpoint 是 7Track 中的,而 endpoint 是 9Track 中的。你们觉得应该如何处理呢?

如果 top level 的 clock tree 上存在 crosstalk(等效于之前介绍过的 common clock tree 上存在 crosstalk,分析对 setup,hold 的影响),子模块 timing 的准确性是否可信?

以上为今天分享的内容,关于数字 IC hierarchical 设计实现 Flow 中寄生参数提取 (RC Extraction),静态时序分析和物理验证过程的内容分享,敬请关注下期内容。

小编知识星球简介(如果你渴望进步,期望高薪,喜欢交流,欢迎加入 ****):

在这里,目前已经规划并正着手做的事情:

-

ICC/ICC2 lab 的编写

-

基于 ARM CPU 的后端实现流程

-

利用 ICC 中 CCD(Concurrent Clock Data)实现高性能模块的设计实现

-

基于 ARM 四核 CPU 数字后端 Hierarchical Flow 实现教程

-

时钟树结构分析

-

低功耗设计实现

-

定期将项目中碰到的问题以案例的形式做技术分享

在这里,各位可以就公众号推文的内容或者实际项目中遇到的难题提问,小编会在 24 小时内给予解答(也可以发表你对数字后端设计实现中某个知识点的看法,项目中遇到的难点,困惑或者职业发展规划等)。

反正它是一个缩减版的论坛,增强了大家的互动性。更为重要的是,微信有知识星球的小程序入口。星球二维码如下,可以扫描或者长按识别二维码进入。目前已经有 213位星球成员,感谢这 213 位童鞋的支持!欢迎各位渴望进步,期望高薪的铁杆粉丝加入!终极目标是打造实现本知识星球全员年薪百万的宏伟目标。

点击下方 “阅读全文” 了解更多

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?