第一部分:技术科普篇(导言)

从历史的眼光来看半导体行业,我们会发现看似只有指甲盖大小的芯片,其产业链非常长。这条产业链横跨多个基础学科,早期的半导体相关工程师的技术背景主要来自物理、化学等领域。随着计算机技术的发展,计算机辅助设计(CAD)促使分工的逐渐细化,最终导致电子设计自动化(EDA)成为了一门独立的技术分支。

从上世纪 60 年代后期开始,半导体集成电路技术开始蓬勃发展起来,最大的推动力是军事需求。集成电路不仅能提供比分立器件更强的性能,而且大大提高了电路系统的稳定性。特别是 CMOS 集成电路工艺出现之后,无论是芯片的产量,还是良率都进一步得到提高。

由此,在短短二十年内,集成电路开始从小规模集成(SSI)时代,跳跃到大规模集成(LSI)时代,而后快速推进到了超大规模集成(VLSI)时代。“摩尔定律”就像一只看不见的手,在背后推动集成电路的发展。

此外,技术的发展也需要人来推动。作为电路和计算机学科发展的核心院校之一的加州大学伯克利分校,起初并不是一所顶尖名校。今天,它的电子工程和计算机(EE&CS)学院已经是享誉全球的工程学科摇篮。 其实,EE&CS 学院从创立到发扬都和一位中国人有关系,他就是葛守仁(Ernest Kuh)。通过了解他的人生,我们可以将电路设计与EDA发展的很多历史瞬间串起来。这往往比直接推导公式和介绍概念要来得更加有趣。

本篇将分成四个部分。

在第 1 章里,我们会讨论一些关于 EDA 的基础概念来认识 EDA;

在第 2 章里,我们会了解 CAD 的诞生过程,看看它是如何走出大学的研究院而面向工业应用;

在第 3 章里,我们会继续观察 CAD 的发展,逐渐聚焦 CAD 在集成电路行业的应用,并过渡到今天的 EDA。

最后,在第 4 章里,我们会追随葛守仁的脚步,体验早期电路设计和 EDA 的创立与发展。

第1章:重新认识 EDA

作为半导体集成电路工业皇冠上的明珠,在集成电路设计和制造的过程中,电子设计自动化(EDA)技术无处不在。但是,EDA 究竟指的是什么?我们又要如何认识与理解它们?本章将给出关于认识 EDA 的三个角度,然后讨论它的早期发展过程,最后提出基于 EDA、IP 和晶圆代工的集成电路增长飞轮。

1.1 三个角度

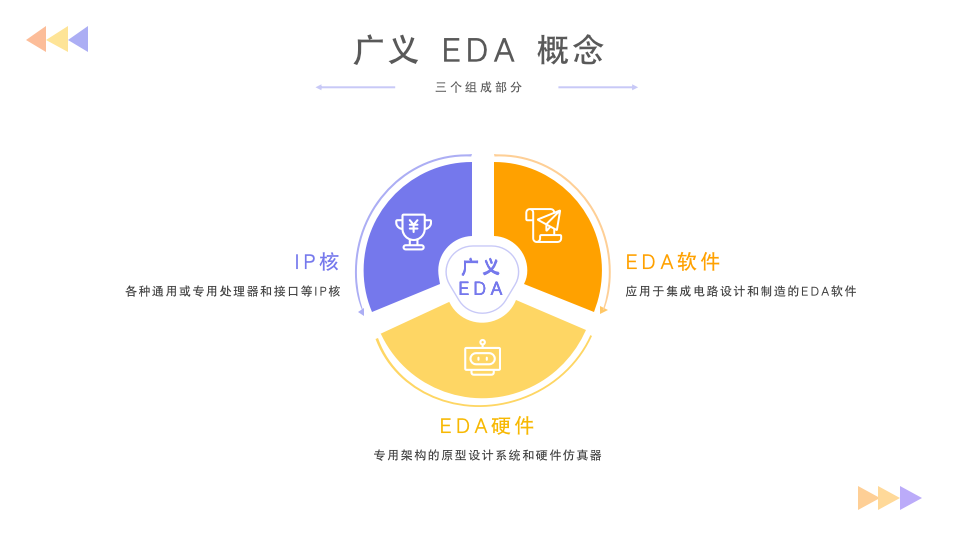

EDA(Electronic Design Automation,电子设计自动化)这个名字表示了它所能实现的目标,不仅仅限于电子设计类的软件,同样包含了硬件和 IP 等内容。有三个关于“认识 EDA ”的角度,需要提前进行澄清,有助于大家对于 EDA 的理解。

第一个角度:EDA 是用于电子设计的软件、硬件和 IP 等的总称。

很多人听到 EDA 就会自然而然地谈起 EDA 软件。诚然,EDA软件是这个领域非常重要的组成部分,也是我们集成电路设计工程师日常接触的核心工具。

不过,为了提高设计效率,EDA 行业在软件的基础之上,也开发出来了专用的硬件加速器等产品来进一步提高设计效率。同时,新千年以来的数字集成电路设计领域,IP 和 SoC 方法学也成为了我们继续沿着摩尔定律不断发展的有力武器。

因此,软件、硬件、IP 等等共同组成了 EDA 行业的基石。

第二个角度:EDA 与 CAD 的区别。

CAD(Computer-Aid Design,计算机辅助设计)的核心思想是用计算机来辅助工程师进行设计。CAD 的崛起要提到1960年代之前的早期计算机发明和应用。当时,计算机主要用在军事领域。

今天,我们使用 PhotoShop 等软件代替在实际纸面上的绘画工作,并且直接输出成电子格式来打印或者生产。这样做的优势,无论是设计和修改,都可以在极短的时间内完成,从而极大提高了生产效率。

CAD 可以应用在很多设计领域,并不限于电子设计、建筑设计、船舶设计、管道设计等等。EDA 相比 CAD,其针对的应用领域主要是电子设计。

到了1960年代,随着集成电路的发明,半导体行业对 CAD 工具的要求变得越来越高。我们已经不能满足于让计算机来辅助设计,而是需要计算机来帮我们自动化地进行设计和优化,才能驾驭在摩尔定律引导下设计复杂度的暴涨。

另一个角度来说,集成电路的制造是一种高精度、不可逆的过程。我们无法在制造完成之后轻松对其进行修改,即便要修改,也需要花费很长的时间,以及不菲的费用。

因此,电路模拟器的出现就代表了 EDA 工具从 CAD 工具的范畴中脱颖而出,开始另辟蹊径进行升级迭代,从而发展出了一个新的市场。

第三个角度:EDA和集成电路(IC)的关系。

1965年,戈登·摩尔发表了对于未来集成电路复杂度趋势的预测。此后,加州理工学院的卡弗·米德(Carver Mead)将这个预测纳入了大学教材。由此,半导体行业开始了围绕“摩尔定律”的追逐战。

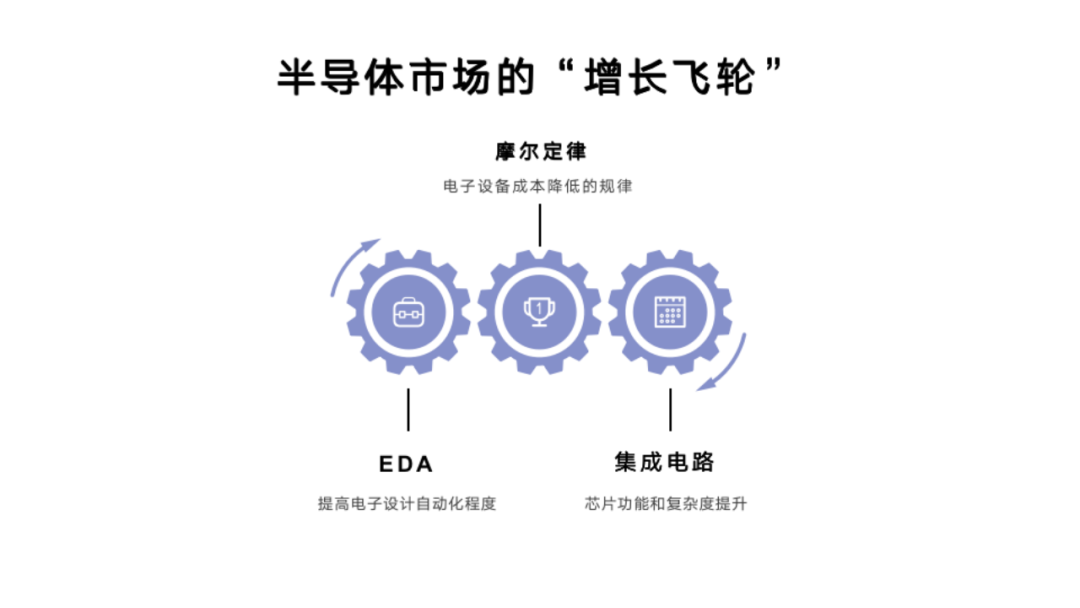

集成电路复杂度的提升,一方面得益于市场对于电子产品需求的激增,另一方面是集成电路设计能力的提升。对于后者,主要得益于 EDA 的发展。同理,集成电路复杂度的提升也增强了服务器硬件的性能,让 EDA 能发挥出更强的能力。

于是,一个快速旋转的“飞轮”就形成了。著名的管理学家吉姆·柯林斯与他的研究团队在《飞轮效应》一书中,用旋转的“飞轮”来比喻企业从小到大的发展历程。摩尔定律、EDA 和半导体集成电路,三者嵌套成了一组技术迭代的飞轮,推动着整个电子系统行业的飞速发展。未来,这个飞轮将高速运转超过 50 年,推动着整个半导体市场步入万亿时代。

1.2 早期发展

上世纪60年代以前,集成电路的版图设计由设计师通过彩色铅笔来绘制。当时,设计师把版图的草稿画在一种特制的牛皮纸上。由于设计师都喜欢用Rubylith 品牌的纸,索性大家就直接用这个品牌名来指代用于版图设计的工具纸了。

设计完成的草稿,经过一些修改之后,被拍照保存或用于分发。后来,随着集成电路制造设备的更新换代,基于数字化程序的设备开始出现,例如数控机床等。因此,草图需要被格式化成专用的电子格式,输入到设备中用于自动化的生产与制造。

到了上世纪70年代,一些早期的版图布局程序和电路仿真程序出现了。

随着电路规模开始扩大,通过设计师肉眼识别设计错误已经很难实现。到了上世纪70年代末期,用于自动化版图检查的程序,以及逻辑设计检查程序开始出现。可见,机器来做辅助检查仍旧属于 CAD 的范畴。

同时,当芯片制造并封装完成之后,由于无法打开封装去观察或者测试,我们为了对其进行分类筛选而开发了一套自动测试模式生成(ATPG)程序。它通过测试引脚来灌入测试向量,并在输出引脚观察信号来判断芯片的质量。

在电路规模增大的基础上,随着工艺的发展,更多金属层被引入芯片制造中。于是,芯片的内部性能开始受到越来越多物理效应的制约。而且随着设计规则的数量越来越多,以至于设计师已经完全无法自行规避,不得不全权依赖检查程序进行作业。

到了上世纪80年代早期,版图检查工具和寄生参数提取工具得到了迅猛发展,特别是针对电阻、电容和电感等的精确分析,成为了一项必须具备的流程。同时,芯片内部的集成组件越来越多,逻辑功能越来越复杂,通过设计师手动摆放功能模块或者标准单元的方式已经被逐步淘汰。

到了80年代中期,商用的自动化布局和布线工具开始活跃起来。设计师可以在很短的时间之内,利用 EDA 工具进行成千上万个模块的自动化布局和布线。相比和纯手工布局相比,在自动化布局发展的早期,尽管会损失一部分硅的面积利用率,但生产率得到了大幅度的提高。

另一方面,随着逻辑功能的复杂度提升,逻辑设计效率提升的需求也接踵而来。上世纪60年代之后,集成电路行业的玩家们提出了很多种硬件描述语言(HDL),一时间百花齐放,百家争鸣。为了适配这些描述语言,各家也推出了对应的逻辑仿真器、逻辑解析器、硬件仿真器等等工具。

随后,为了避免内卷,美国国防部主导了超高速集成电路(VHSIC)计划,让这些描述语言最终在上世纪80年代聚合到了 VHDL 语言上。不过,因为 VHDL 语言不够灵活,逻辑设计师们又把眼光放在了 Verilog 语言上。

到了上世纪80年代末期,数字集成电路的规模继续膨胀,如何将这些硬件描述语言设计的逻辑功能,快速而高效地转化为用于物理版图设计的门级网表(Netlist)就成为了发展的瓶颈。因此,一些电子系统公司和初创的EDA公司开始研发逻辑综合工具来应对这些挑战。

大约在上世纪80年代末到90年到初,商用 EDA 公司崭露头角。一方面是因为 EDA 开发的投入较大,回报并不高,系统公司内部的 CAD 团队已经难以为继。因此,这些团队要么被剥离,要么被裁撤。由此,初创的 EDA 公司获得了更加集中的资源和资金,迎来了雨后春笋般的发展。

当时,初创的 EDA 公司只要能生存三、五年的时间,基本上能陆陆续续地完成 IPO 或者被并购。另一方面,EDA 工具太多并不意味着行业生产效率的倍增,反而因为各家工具所用的数据格式不一致,而带来了设计流程集成化的麻烦。一些利用性能更加优异的数据库而打造的 EDA 工具就成为了市场上的新利器,促使着 EDA 公司新一轮的并购与整合。

摩尔定律走过三十年后,到了上世纪90年代,随着工艺特征尺寸的不断缩小,电磁噪声问题成为了新的挑战。EDA 公司纷纷针对电源与信号完整性等等方面进行了优化与加固,同时也有一些新的公司和产品出现,给予市场更多的选择。

紧接着,工艺制造方面也遇到了新的瓶颈,针对纳米级工艺的可制造性(DFM)问题也被着重提出。于是,新工艺的研发和EDA工具也紧紧绑定在了一起,从而提出了设计与工艺联合优化(DTCO)的方法学。

到了上世纪90年代末期和新千年初,IP 与 SoC 设计方法学被提出。这种方法让设计师可以用标准的 IP 来组建整个芯片系统,因此系统逻辑功能验证的工作变得越来越重要。一些基于断言(Assertion)和形式化(Formal)等等方式的静态验证方法学开始出现,填补了数字逻辑仿真器和硬件仿真器的功能空白。

最近的二十年,IP和SoC设计方法已经成为了数字集成电路设计的标准方法,除了一些自行定制的功能模块,大部分的处理器、接口协议等等功能模块,市面上已经有了成熟的IP供用户选择。由此一来,专注于 IP 开发的 EDA 公司也开始占据一定市场。

1.3 增长的飞轮

上世纪90 年代中后期,IP 和 SoC 设计方法学逐渐确立,超大规模数字集成电路的设计流程也基本定型。EDA 三巨头(Synopsys、Cadence、Mentor Graphics)开始了设计流程的整合,希望通过各种互补的方法来继续提高生产效率。由此,PPAC 的概念,也就是性能、功耗、面积和成本开始深入人心。

为了不断提高 PPAC,EDA 供应商们开始与IP供应商、晶圆代工厂等进行深度合作,从而造就了另一个发展的“飞轮”。

原本,晶圆制造(Fab)还是芯片大厂独有的部门。上世纪80年代,随着以台积电(TSMC)和联电(UMC)为代表的晶圆代工(Foundry)模式的兴起,各具特色的无晶圆设计(Fabless)企业开始奔涌出现,使得 EDA 用户的数量一度剧增。这些企业之间的竞争,表面上是产品市场的竞争,而实际上是设计效率和技术能力的竞争。

芯片行业是赢家通吃的行业,只要产能没有遇到问题,谁能更早推出优异产品,谁就有可能迅速占据最大的市场份额。因此,无晶圆设计企业会将 EDA 工具的使用推动到极限。

不仅如此,大型的无晶圆设计企业还会综合各家 EDA 工具的特性来打造自己的专用设计流程,并且和晶圆代工厂深度合作,从而确保自己的产品良率、封测效率都优于对手。

与此同时,EDA 厂商也在和无晶圆设计企业的合作中吸取到了很多宝贵的设计经验,并且精选出那些值得做成通用算法或者应用的方案添加到新版本的 EDA 工具中。这样一来,其它的 EDA 用户就可以通过软件升级和更新的方式获得这些新的技术。

同理,IP 供应商也会采用 EDA 工具进行开发。在某些方面,IP 企业和无晶圆设计企业之间是一种微妙的竞合关系。它们在某些项目上互相合作,促成新的芯片开发项目;同时,在某些项目上,无晶圆设计企业会倾向于使用自研的 IP 来完成设计。这背后的其实就是成本计算的逻辑。

正是这样的发展飞轮促使着 EDA 公司在竞争中更倾向于构建统一的工具链。到了2010年代,头部的 EDA 厂商开始不断推出平台型的 EDA 整合方案。例如,RTL 和 SDC 静态质量检查的整合、逻辑动态仿真和调试平台的整合、逻辑综合和物理设计的整合、PPAC 签核流程的整合等等。

这样一来,新入局的 EDA 初创公司将面临更高的竞争门槛,其表现为 EDA 行业在美国变成了看似“夕阳”的技术行业。

站在今天的角度来看,全球EDA的市场战争可以说已经结束,但这并不代表EDA行业行将没落,而是说它似乎很难有革命性的技术突破。例如,EDA软件普遍使用 C/C++ 等语言来编写,同时大部分也只能运行在基于 x86 架构的 CPU 服务器上。一些需要大数据量与批处理的 EDA 软件,也只能运行在 Linux 操作系统上。相比于同样超大规模数据量的互联网应用,EDA技术仍旧局限在二三十年前定型的IT架构上。

随着摩尔定律的失效,芯片架构开始朝着小芯片(Chiplet)和异构封装等方向发展,给 EDA 提出了更多的挑战。三维异构封装不仅可以实现多个裸片的堆叠,而且还可以将不同工艺制造的裸片进行封装。

让我们想象一条这样的逻辑路径。它可能从裸片A(12nm)中出发,经过硅通孔(TSV)抵达另一个裸片B(7nm),然后通过硅介质层(interposer)进入外部高速存储器。如果说在单裸片中进行分析的难度是N,那么这样一条路径的分析难度将可能是N的二次方以上。而且,裸片和裸片之间的堆叠还会引入更多的电气问题,如散热、噪声等等。特别是工艺敏感性上,其影响不是简单的相加,可能是相乘关系。

1.4 小结

总之,未来 EDA 面对的挑战和趋势总结有三:

第一,需要分析的数据量还会继续增长,我们可以期待云计算和新型计算范式在EDA上的应用;

第二,EDA 开发的资金投入会继续扩大,头部 EDA 厂商的市场份额会更加集中;、

第三,一些特色工艺或者其它计算介质(光子、量子)也会促使新 EDA 市场的诞生。

本文讲述了半导体行业尤其是集成电路技术的发展历程,从早期的电子设计自动化(EDA)起源,到CAD技术的兴起,再到摩尔定律驱动的集成电路飞跃,以及加州大学伯克利分校的角色。文章详细阐述了EDA的定义、与CAD的区别,以及与集成电路、IP和晶圆代工的关系,同时展望了未来EDA面临的挑战,如数据量增长、技术集中化和新兴计算介质的影响。

本文讲述了半导体行业尤其是集成电路技术的发展历程,从早期的电子设计自动化(EDA)起源,到CAD技术的兴起,再到摩尔定律驱动的集成电路飞跃,以及加州大学伯克利分校的角色。文章详细阐述了EDA的定义、与CAD的区别,以及与集成电路、IP和晶圆代工的关系,同时展望了未来EDA面临的挑战,如数据量增长、技术集中化和新兴计算介质的影响。

2303

2303

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?