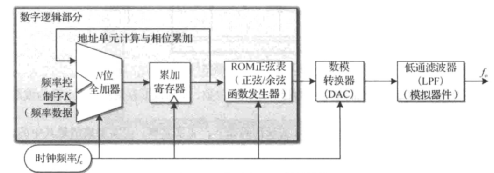

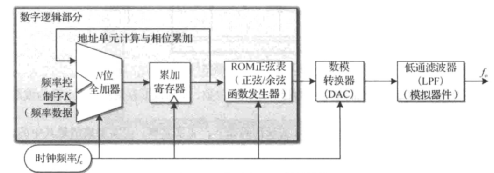

(一)分频器相关原理 1 . DDS原理 任意分频原理起源于DDS( Direct Digital Synthesizer ,直接频率合成法)的原理,DDS是重要的频率合成方法,在波形发生器中占有举足轻重的地位。 D DS 是一种从相位概念出发,直接合成所需要的波形的频率合成技术,其实质是以基准频率源(系统时钟)对相位进行等间隔采样。对于正余弦类型的频率合成,DDS基本上等效于NCO加上DA实现。 DDS由相位累加器和波形存储器、数模转换器(DAC)以及模拟低通滤波器(LPF)三部分组成,实现原理与NCO完全一致,只是存储的ROM由NCO替代为需要发生的波形文件,并通过数模转换器转换为模拟信号,最后由具有内插作用的LPF将其平滑转化为连续的正弦波形以输出。一个典型的DDS硬件结构如 图 1‑75 所示

图 1 ‑ 75 典型的DDS硬件结构 2 . 任意分频发生器的实现 直接频率合成法通过相位累加原理,实现了通过步长可配置的任意波形输出。根据这个原理,通过对相位累加的地址进行处理,可以直接计算得到相应的频率。这一原理应用于Verilog HDL中,理论上也能实现任意频率的分频电路。设计实现的框图如 图 1‑76 所示。

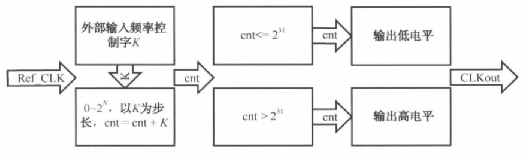

图 1 ‑ 75 典型的DDS硬件结构 2 . 任意分频发生器的实现 直接频率合成法通过相位累加原理,实现了通过步长可配置的任意波形输出。根据这个原理,通过对相位累加的地址进行处理,可以直接计算得到相应的频率。这一原理应用于Verilog HDL中,理论上也能实现任意频率的分频电路。设计实现的框图如 图 1‑76 所示。

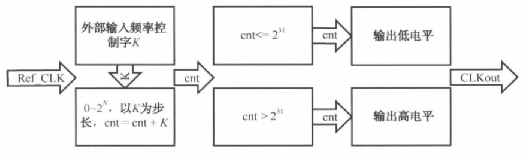

图 1 ‑ 76 相位累加原理的实现框图 假定FPGA基准时钟为1 00 M Hz ,即基准时钟为: f

c =100x10

6 Hz 同时规定计数器的位数 N

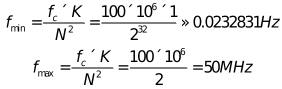

2 =32 , K 为频率控制字,则相位累加后输出的最大频率与最小频率分别为:

图 1 ‑ 76 相位累加原理的实现框图 假定FPGA基准时钟为1 00 M Hz ,即基准时钟为: f

c =100x10

6 Hz 同时规定计数器的位数 N

2 =32 , K 为频率控制字,则相位累加后输出的最大频率与最小频率分别为:

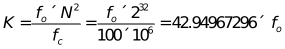

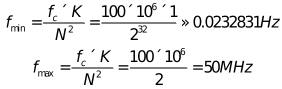

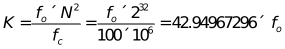

2 1 (.) 变换公式,可以计算得到固定基准频率下每增/减1 Hz的频率控制字K的大小,如下所示:

2 1 (.) 变换公式,可以计算得到固定基准频率下每增/减1 Hz的频率控制字K的大小,如下所示:

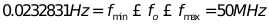

2 2 (.) 由此公式可知,每增、减1 H z ,K的步进为4 2.949 672 96 。 另外,与前面的分析一致,最大的频率、最小频率(频率分辨率)分别为:

2 2 (.) 由此公式可知,每增、减1 H z ,K的步进为4 2.949 672 96 。 另外,与前面的分析一致,最大的频率、最小频率(频率分辨率)分别为:

2 3 (.) 根据以上公式可以得到固定基准时钟下的任意频率发生器,其精度为0 .0232831 H z 。不过相位累加器得到的只是cnt累加的结果,为了得到频率,还需要对相位累加值cnt进行一定的处理,即采用类似于AD 9850 内DDS核的比较器,来实现方波 à 频率的转换。 3 . 实验验证 假定FPGA基准时钟为1 00 M Hz ,即基准时钟为: f

c =100x10

6 Hz 当使用UART时,波特率BPS=1 15200 bps 。 (一)直接分频法 一个位的周期 = 1 / bps = 1/ 115200 = 0.000

2 3 (.) 根据以上公式可以得到固定基准时钟下的任意频率发生器,其精度为0 .0232831 H z 。不过相位累加器得到的只是cnt累加的结果,为了得到频率,还需要对相位累加值cnt进行一定的处理,即采用类似于AD 9850 内DDS核的比较器,来实现方波 à 频率的转换。 3 . 实验验证 假定FPGA基准时钟为1 00 M Hz ,即基准时钟为: f

c =100x10

6 Hz 当使用UART时,波特率BPS=1 15200 bps 。 (一)直接分频法 一个位的周期 = 1 / bps = 1/ 115200 = 0.000

图 1 ‑ 75 典型的DDS硬件结构 2 . 任意分频发生器的实现 直接频率合成法通过相位累加原理,实现了通过步长可配置的任意波形输出。根据这个原理,通过对相位累加的地址进行处理,可以直接计算得到相应的频率。这一原理应用于Verilog HDL中,理论上也能实现任意频率的分频电路。设计实现的框图如 图 1‑76 所示。

图 1 ‑ 75 典型的DDS硬件结构 2 . 任意分频发生器的实现 直接频率合成法通过相位累加原理,实现了通过步长可配置的任意波形输出。根据这个原理,通过对相位累加的地址进行处理,可以直接计算得到相应的频率。这一原理应用于Verilog HDL中,理论上也能实现任意频率的分频电路。设计实现的框图如 图 1‑76 所示。

图 1 ‑ 76 相位累加原理的实现框图 假定FPGA基准时钟为1 00 M Hz ,即基准时钟为: f

c =100x10

6 Hz 同时规定计数器的位数 N

2 =32 , K 为频率控制字,则相位累加后输出的最大频率与最小频率分别为:

图 1 ‑ 76 相位累加原理的实现框图 假定FPGA基准时钟为1 00 M Hz ,即基准时钟为: f

c =100x10

6 Hz 同时规定计数器的位数 N

2 =32 , K 为频率控制字,则相位累加后输出的最大频率与最小频率分别为:

2 1 (.) 变换公式,可以计算得到固定基准频率下每增/减1 Hz的频率控制字K的大小,如下所示:

2 1 (.) 变换公式,可以计算得到固定基准频率下每增/减1 Hz的频率控制字K的大小,如下所示:

2 2 (.) 由此公式可知,每增、减1 H z ,K的步进为4 2.949 672 96 。 另外,与前面的分析一致,最大的频率、最小频率(频率分辨率)分别为:

2 2 (.) 由此公式可知,每增、减1 H z ,K的步进为4 2.949 672 96 。 另外,与前面的分析一致,最大的频率、最小频率(频率分辨率)分别为:

2 3 (.) 根据以上公式可以得到固定基准时钟下的任意频率发生器,其精度为0 .0232831 H z 。不过相位累加器得到的只是cnt累加的结果,为了得到频率,还需要对相位累加值cnt进行一定的处理,即采用类似于AD 9850 内DDS核的比较器,来实现方波 à 频率的转换。 3 . 实验验证 假定FPGA基准时钟为1 00 M Hz ,即基准时钟为: f

c =100x10

6 Hz 当使用UART时,波特率BPS=1 15200 bps 。 (一)直接分频法 一个位的周期 = 1 / bps = 1/ 115200 = 0.000

2 3 (.) 根据以上公式可以得到固定基准时钟下的任意频率发生器,其精度为0 .0232831 H z 。不过相位累加器得到的只是cnt累加的结果,为了得到频率,还需要对相位累加值cnt进行一定的处理,即采用类似于AD 9850 内DDS核的比较器,来实现方波 à 频率的转换。 3 . 实验验证 假定FPGA基准时钟为1 00 M Hz ,即基准时钟为: f

c =100x10

6 Hz 当使用UART时,波特率BPS=1 15200 bps 。 (一)直接分频法 一个位的周期 = 1 / bps = 1/ 115200 = 0.000

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

2663

2663

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?