CIC滤波器设计原理总结

一、CIC滤波器应用概述

在通信数字信号上下变频时,经常会用到对数字信号的升采样和降采样,即通过CIC数字速率器实现变采样率,下面将总结CIC滤波器设计原理,便于FPGA实现参考。

二、基本原理理解

在研究CIC滤波器前,需要真正弄明白并理解一些基本概念,具体整理如下。

1、模拟与数字信号关于频率的理解

模拟信号的频率:1秒内信号周期变化或重复了多少次,在日常生活中,以电风扇为例,频率指风扇1秒钟转了多少圈,模拟信号频率一般用f表示

模拟信号角频率:用弧度表示1秒内信号变化多少弧度,即Ω=2πf=2π/T(其中f为模拟信号的频率,T为模拟信号的周期),可以理解1秒钟旋转了多少个2π,或者1秒内经历了多少个信号周期T。

数字信号频率(数字角频率,或数字频率):数字信号是模拟信号的采样,为了建立模拟信号与数字信号的联系,以及与采样频率的关系,引入了数字频率,w=2πf/fs(其中f为模拟信号的频率,fs为采样频率),由于那奎斯特采样定律,f≤fs/2,因此数字频率的范围一般为(0,π),可以理解数字频率是模拟信号角频率相当于fs的归一化处理,基于按照2π归一化,可以表示的归一化频率为(0,0.5),在matlab或滤波器设计软件中设计数字滤波器起始或截止频率门限时,经常用归一化频率表示。

2、变采样对信号频率搬移变化的理解

首先采样率的变化对信号基带模拟频谱(物理频率)是没有影响的。

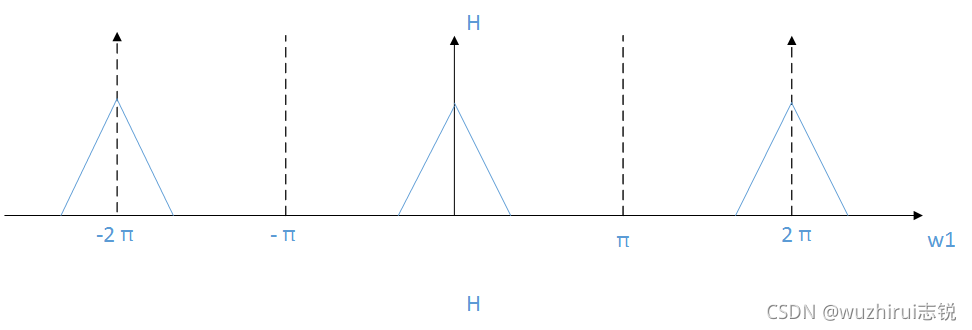

下面以3倍升采样为例,原数字频率的w1=2πf/fs,其数字频谱如下图:

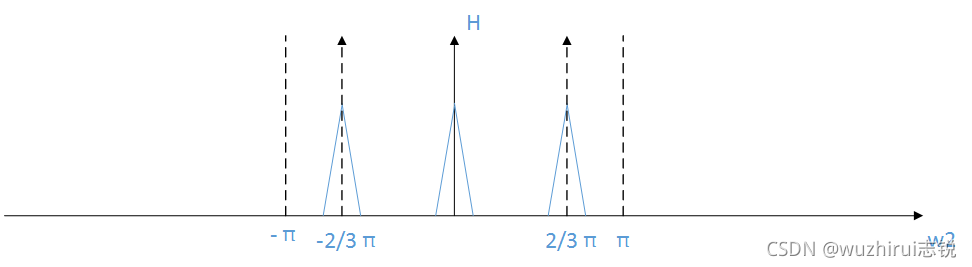

3倍升采样后w2=2πf/3fs,即w2=w1/3,w2在w1三分之一处的数字频谱与w1的数字频谱是一致的,w2相当于w1的频谱在频率上压缩了三分之一,w2的数字频谱如下图所示:

3、升采样(内插)与降采样(抽取)方法

升采样(内插)的方法是在原两个采样点之间插入零,然后进行抗镜像低通滤波。在上面数字频谱中,可以看出在-π~π内出现了镜像信号,同样在对应的模拟信号频谱中,采样率的增加信号频谱周期性延拓的周期将增加,期间出现了多余的镜像信号,低通滤波器的作用是滤除镜像信号。

降采样(抽取)的方法是先进行抗混叠滤波器,然后再进行抽取。在模拟信号频谱中,抽取后信号频谱的周期延拓的周期将减少,如果过渡抽取将导致无法满足奈奎斯特采样定律,出现频谱混叠,或者干扰进入带内,同样在数字频谱中,抽取相当于信号扩展,抗混叠滤波器都是为了避免出现频谱混叠及干扰。

三、CIC滤波器幅频响应直观认识

CIC(Cascade Intergrator Comb):级联积分梳妆滤波器,是由积分器和梳妆滤波器级联而得。由于滤波器系数为1,无需对系数进行存储,无需乘法器,在设置抽取/插值因子时候不改变滤波器整体结构。

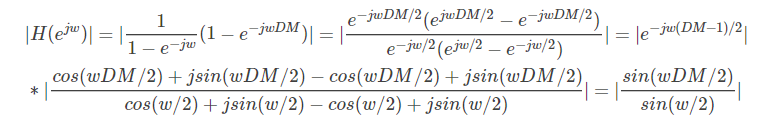

CIC的幅频响应函数如下,其中D为抽取倍数,M为延迟因子(一般为1)。

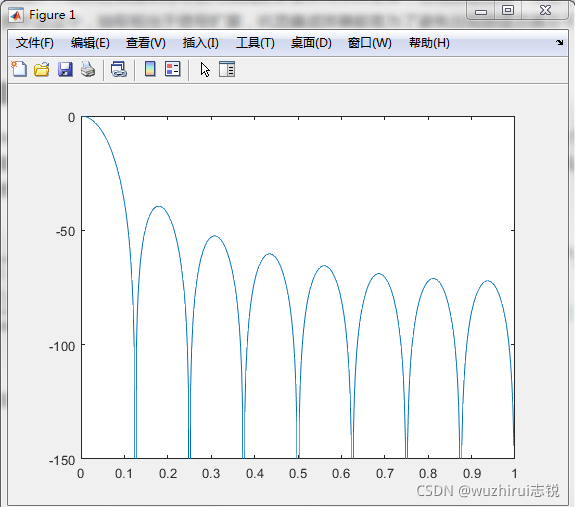

在CIC的幅频响应如下图所示:

matlab仿真参考代码如下:

%CIC frequence analyze

close all;

clear all;

clc;

resampleRate=16;%升采样倍数

cicFilerOrder=3;%阶数或级联数

sampleNum=400;%采样点数

n=0:sampleNum-1;

w=n.*(pi/sampleNum);%在0~pi间频率采样,pi对应fs/2

Hz=((sin(resampleRate*w/2))./(sin(w/2))).^(cicFilerOrder);

H_gui=abs(Hz)./max(abs(Hz));

plot(w/pi,20*log10(H_gui));

axis([0,1,-150,0]);%横轴显示0~1,纵轴显示-150到0.

四、CIC滤波器设计级联框图

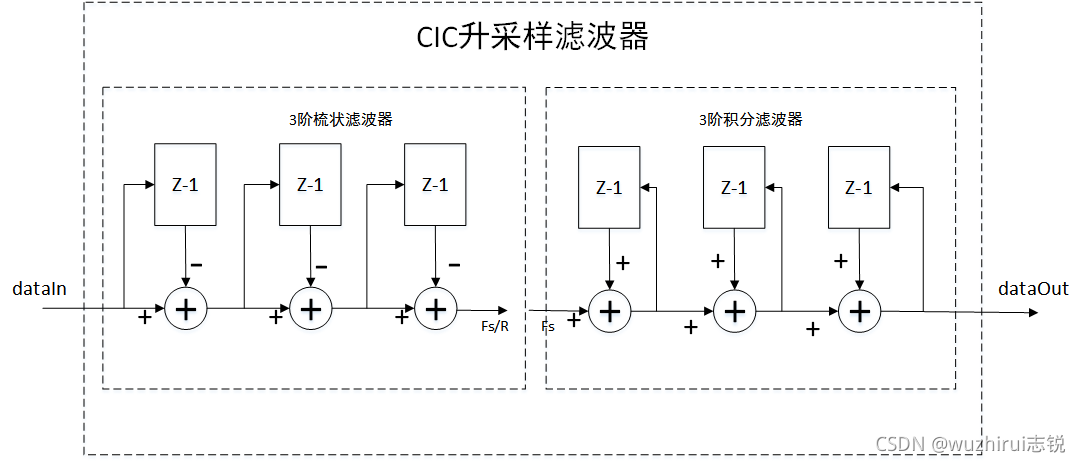

下面是3阶升采样(内插)CIC滤波器级联框图:

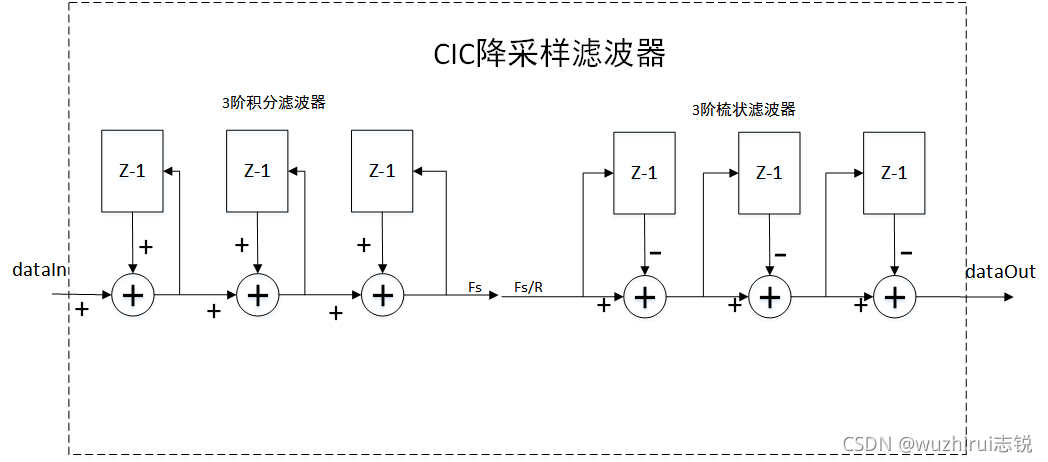

下面是3阶降采样(抽取)CIC滤波器级联框图,将梳妆滤波器与积分滤波器对调即可。

本文详细介绍了CIC滤波器在数字信号处理中的应用,包括升采样和降采样的原理,以及CIC滤波器的幅频响应和级联结构。通过实例展示了3倍升采样和降采样对信号频率的影响,并提供了CIC滤波器的MATLAB仿真代码,帮助读者理解其工作机制。

本文详细介绍了CIC滤波器在数字信号处理中的应用,包括升采样和降采样的原理,以及CIC滤波器的幅频响应和级联结构。通过实例展示了3倍升采样和降采样对信号频率的影响,并提供了CIC滤波器的MATLAB仿真代码,帮助读者理解其工作机制。

2363

2363

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?