来自微信公众号 “数字芯片实验室”

加减法是一类非常基础的运算,本文分析最简单的行波进位加/减法器(Ripple CarryAdder/Subtractor)的硬件开销和性能问题。

在文章的开始控制变量,仅使用工艺库中的基本逻辑门

AND-AND2X1

NOT-INVX1

OR-OR2X1

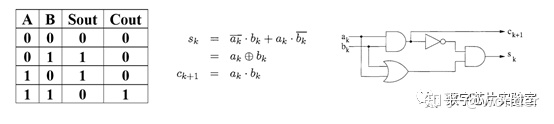

1bit半加器

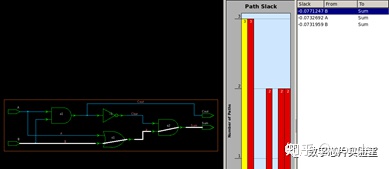

上面分别是1bit半加器的真值表、逻辑关系式和原理图。然后编码Verilog HDL,综合设计,分析以及可视化关键路径。

module ha (Cout, Sum, A, B);

input A, B;

output Cout, Sum;

wire Cbar,p;

AND2X1 a1 (.Y(Cout), .A(A), .B(B)) ;

INVX1 i1 (.Y(Cbar), .A(Cout) ) ;

OR2X1 o1 (.Y(p), .A(A), .B(B)) ;

AND2X1 a2 (.Y(Sum), .A(Cbar), .B(p));

endmodule // ha

1bit全加器

上面分别是1bit全加器的真值表、逻辑关系式和原理图。层次化的设计方法复用半加器逻辑,提高设计效率。然后编码Verilog HDL,综合设计,分析以及可视化关键路径。

module fa(Cout,Sum,A,B,Cin);

input A,B,Cin;

output Cout,Sum;

wire c1,s1;

haha1(.Cout(c1), .Sum(s1), .A(A), .B(B));

wire c2 ;

haha2(.Cout(c2), .Sum(Sum), .A(Cin), .B(s1));

OR2X1 o1(.Y(Cout),.A(c1),.B(c2)) ;

endmodule //fa

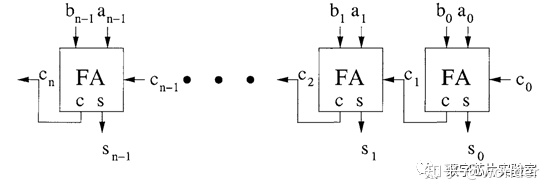

接下来进入本文的重点,行波进位加法器(Ripple Carry Adder,RCA)。

这是最简单的多比特加法器。一个n比特的RCA需要n个全加器,第k-1个全加器的carry out,作为第k个全加器的carry in。虽然设计简单,但是由于这种进位传播方式,会造成随着加法器比特数增加,硬件开销和延时也会线性增加。

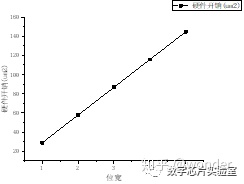

1~5比特行波进位加法器硬件开销

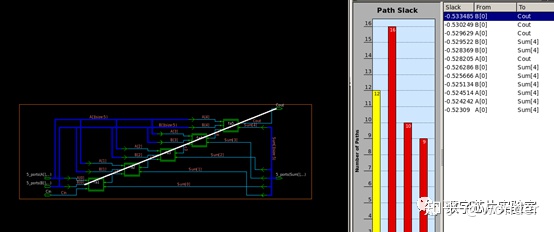

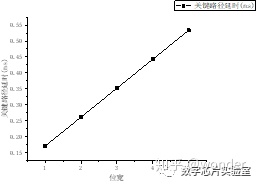

1~5比特行波进位加法器关键路径延时

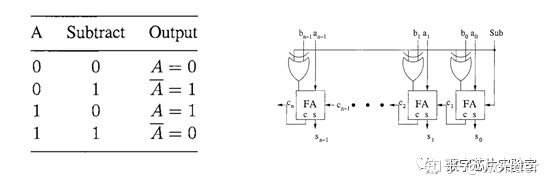

在数字系统设计中加法器和加法器一样重要。根据A-B=A+(-B),对于n比特加法器只需要增加n个异或门即可完成n比特减法器

如果Sub=1,表示执行减法计算,反之执行加法计算。

2602

2602

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?