实验内容

调用一位二进制全加器模块和4位并行进位模块,设计一个4位并行进位加法器模块,并仿真测试,给出时序图

程序代码

module bingxing (output [3:0] F, output c4, input [3:0] A, input [3:0] B, input c0);

wire [3:0] G, P;

wire [4:0] C;

assign C[0]=c0;

PalC palc1(G,P,C[4:1],A,B,c0);

quanjiaqi qj0(A[0],B[0],C[0],,F[0]);

quanjiaqi qj1(A[1],B[1],C[1],,F[1]);

quanjiaqi qj2(A[2],B[2],C[2],,F[2]);

quanjiaqi qj3(A[3],B[3],C[3],,F[3]);

assign c4=C[4];

endmodule

module PalC (output [3:0] G, output [3:0] P, output [4:1] C, input [3:0] A, input [3:0] B, input C0);

assign P=A|B;

assign G=A&B;

assign C[1]=G[0]|P[0]&C0;

assign C[2]=G[1]|P[1]&G[0]|P[1]&P[0]&C0;

assign C[3]=G[2]|P[2]&G[1]|P[2]&P[1]&G[0]|P[2]&P[1]&P[0]&C0;

assign C[4]=G[3]|P[3]&G[2]|P[3]&P[2]&G[1]|P[3]&P[2]&P[1]&G[0]|P[3]&P[2]&P[1]&P[0]&C0;

endmodule

module quanjiaqi(A,B,CIN,COUT,F);

input A,B,CIN;

output F,COUT;

assign F=A^B^CIN;

assign COUT=A&B|((A^B)&&CIN);

endmodule

测试用例

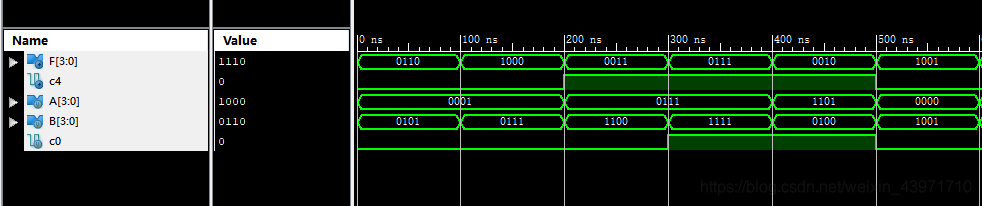

initial begin

A=4'b0001;B=4'b0101;c0=1'b0;

#100 A=4'b0001;B=4'b0111;

#100 A=4'b0111;B=4'b1100;

#100 B=4'b1111;c0=1'b1;

#100 A=4'b1101;B=4'b0100;

#100 A=4'b0000;B=4'b1001;c0=1'b0;

#100 A=4'b1000;B=4'b0110;

end

仿真波形图

2372

2372

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?