源自:微信公众号 “数字芯片实验室”

在IC设计中,如果寄存器之间的组合逻辑延时过大,可能会称为设计中的关键路径,从而降低整个电路的工作频率。

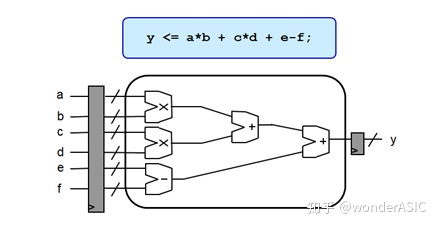

如下图所示,是一个输入和输出寄存的算术计算逻辑。在set_input_delay和set_output_delay默认为0的情况下,触发器之间的组合逻辑成为限制电路工作频率的因素。

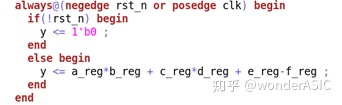

Verilog 代码如下:

我们通过 create_clock –period 10 [get_ports clk]来约束时钟。

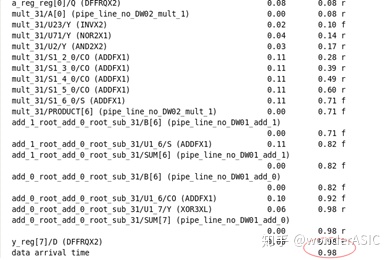

Compile –> report_timing :

关键路径经过了多个乘法器和加法器,延时为 0.98ns

那么,如何能提高该设计的工作频率?

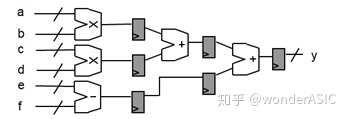

答案就是,流水线设计,即增加“pipeline stage ”

部分Verilog 代码如下:

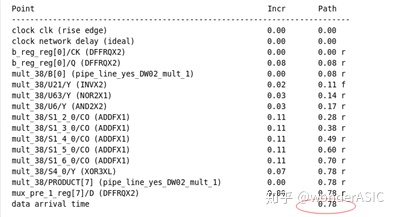

Compile –> report_timing :

关键路径为乘法器,延时为 0.78ns

最后我们得出结论:pipe line 分割了关键路径延时,提高了整体设计的工作频率 25.6%。

并且,在该算术逻辑电路位数增多时,性能提高越明显。

4865

4865

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?