最近在读Xilinx的User Guide,看到时钟使能(Clock Enables)这里比较感兴趣,写下这篇文章做个小结。

本文所讲的Clock Enables与时钟门控电路无关,指的是触发器的Clock Enable输入端口。我将从以下几点对Clock Enables做个小结:

- 什么是 Clock Enables ?

- 如何 Create Clock Enables ?

- Clock Enables 对FPGA设计有什么影响 ?

什么是 Clock Enables ?

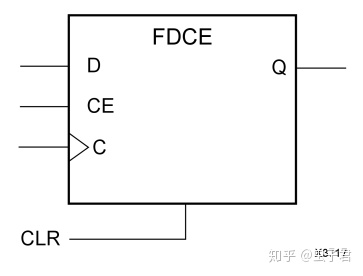

图1是Xilinx D Flip-Flop的示意图。D端是我们熟悉的数据输入端,Q端是数据输出端,C端则是时钟输入端,CLR是复位端(上一篇专栏文章提到的)。CE端便是这次我们要了解的Clock Enable。

那么CE端有什么用呢,Xilinx文档里有这样的描述

When clock enable (CE) is High and asynchronous clear (CLR) is not asserted, the data on the data input (D) of this design element is transferred to the corresponding data output (Q) during the clock (C) transition. When CE is Low, clock transitions are ignored.

简单点说(不考虑复位信号),就是CE端控制这个DFF的输入时钟是否有效。我们都知道DFF是靠时钟沿来采样输入信号,如果CE端为高电平1,则时钟有效,输入D会在时钟跳变时传输到Q端,而如果CE端为低电平0,则时钟无效,无论输入时钟如何跳变,输出端Q始终保持之前的值。

如何 Create Clock Enables ?

这里Create指的是设计综合后的电路会用到CE端。主要有两种方法:

- 在时序逻辑的always块里混合组合逻辑

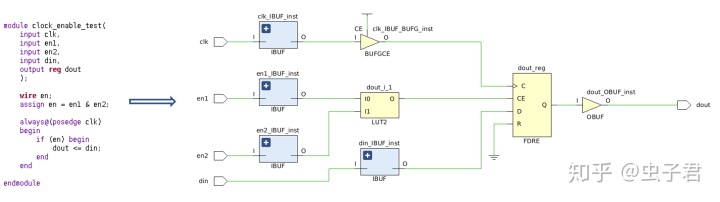

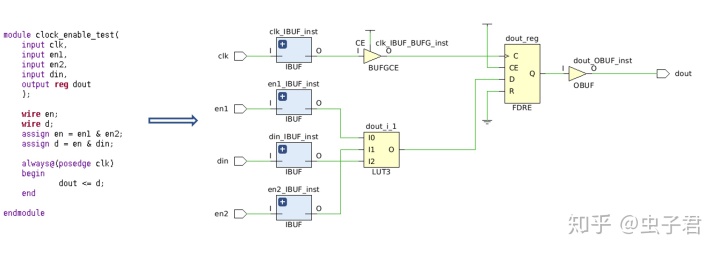

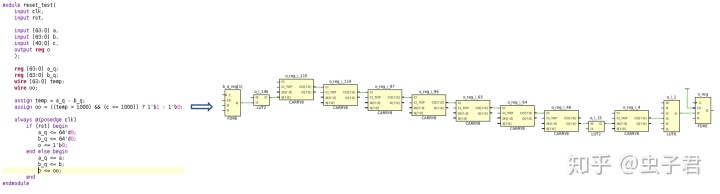

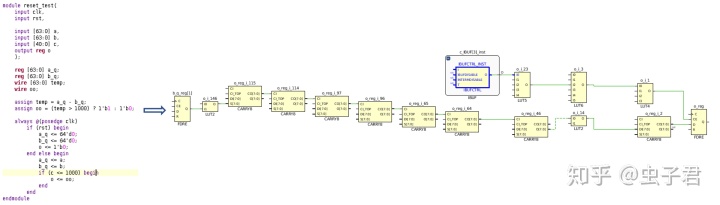

对比图2和图3的Coding风格,可以看到当我们在时序逻辑的always块里混合组合逻辑时,CE端会被用到。而当我们完全隔离组合逻辑与时序always块时,CE端则接电源没有被用到。

- 使用属性 “Direct Enable”

如果对图3的示例中的信号 en 添加属性,则意味着我们强制让工具将该信号connect到寄存器的CE端,综合后也会用到CE端。

wire Clock Enables 对FPGA设计有什么影响 ?

对于Clock Enable对FPGA设计的影响,Xilinx Guide有这么一句话

When used wisely, clock enables can significantly reduce design power with little impact on area or performance.

这里也不难理解,因为CE会使得寄存器的时钟无效,寄存器便不会在时钟跳变时采样输入信号,输入的任何变化对输出无影响。没有“采样”这个操作意味着功耗的降低,因为没有电流的流动。

除了这一点,我对CE对时序的影响也比较感兴趣。工作中,我一般的Coding习惯是图3的样子,即组合逻辑与时序逻辑分开来写。当看到图2与图3的对比,我在想,是不是可以将两个寄存器之间的组合逻辑一部分放在CE端,一部分放在D端,从而增加D端setup time的slack使其更容易meet timing。于是我做了如下尝试,其实是图2和图3对比的复杂版。

可以看到,图4和图5的关键路径都是在D端,但是图5的关键路径确实比图4短,综合后的延迟也要更低一些。这说明CE的使用确实可以达到优化Timing的目的。如果你是习惯于图2写法的人,那么可能你的组合逻辑大部分在CE端,这时想优化Timing则可以类似地将部分组合逻辑推到D端。

总结

Clock Enable是FPGA寄存器的一个输入端,用来控制寄存器输入时钟是否有效。合理地使用CE信号可以降低设计的功耗,也可以优化Timing。

以上只是本人阅读Guide的总结和思考,欢迎留言讨论。

参考资料

- 《UltraFast Design Methodology Guide for the Vivado Design Suite》

7475

7475

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?