前面我们已经讲到内插滤波器的Verilog设计方法。但是我们可能并不是很清楚,内插滤波器到底可以用来干什么。那么本节就带着这些疑问,进一步详细述说内插滤波器的应用。

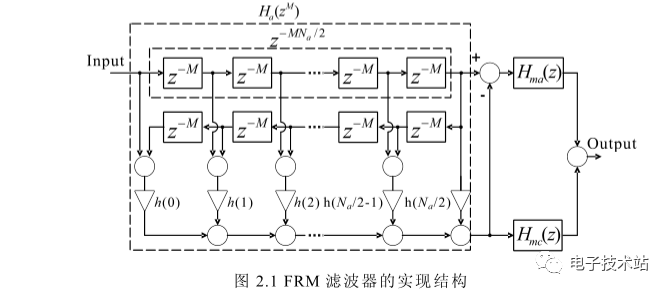

在设计FIR滤波器过程中,当FIR滤波器的过渡带需要设计的很窄的时候,采用直接型FIR滤波器设计结构,所得的滤波器的阶数会做到很高,那么会消耗大量的DSP乘法器资源。因此想要用较少的资源获得同等的滤波器性能就需要对此时的FIR滤波器进行优化。采用频率响应掩蔽(FRM)技术的方法,可以在过渡带很窄的时候,用较少的DSP乘法器实现同等性能的FIR滤波器。此时我们的内插滤波器就派上用场了。接下来介绍运用内插滤波器来设计频率响应掩蔽滤波器的步骤:

1、先对低阶宽带的FIR滤波器的系数内插可以得到高阶滤波器;

2、对低阶宽带FIR滤波器系数插0不会增加实现时消耗的DSP资源;

3、内插会产生频谱镜像;

4、通过频率响应掩蔽滤波器可以滤掉内插而产生的镜像频谱。

其大致的实现机制如图1所示。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?