摘要

高速串行链路系统的 IBIS-AMI 建模已成为业界事实上的标准。IBIS-AMI 建模标准是经过不断演进而确立的,最初只是用于 NRZ 信令的直通(THRU)通道建模,而后逐渐扩展到包含串扰干扰源、包含中继器的链路、反向通道发射机(TX)和接收机(RX)均衡器训练流程,以及 PAM4 和 双二进制信令的建模。

然而,迄今为止,IBIS-AMI 建模还只能支持同步系统,即发射机和接收机共享一个公共参考时钟源。在实际应用中,更多的系统采用的是异步工作模式,即发射机和接收机的参考时钟之间存在一定的频率偏移。因此,在发射机和接收机之间发生频率偏移时,不能通过标准的 IBIS-AMI 仿真验证时钟数据恢复(CDR)特性。后果是无法精确地评测频率偏移的影响,导致对系统性能的估计过于乐观。

在本文中,我们提出了一种方法,确保可以在现有的 IBIS-AMI 架构中构建异步高速链路系统的模型, 从而能够通过时域仿真研究异步状况下 CDR 的动态特征。本文阐述了进行异步链路系统仿真的步骤, 并详细介绍了为捕获异步效应而需要对现有建模和仿真实践做出的改进。我们利用提议的方法分析了异步链路的具体实例,并提供了仿真结果,之后展示了在参考时钟有频率偏移时的 CDR 特性,并测量了由此所导致的计时偏差。我们还利用在不同数据速率下具有不同损耗特征的通道,检查了对频率PPM 偏移的系统容限。最后,文中论述了异步发射机和接收机时钟对链路预算和系统性能的影响。

1. 引言

本文介绍了异步高速链路系统的输入/输出缓冲信息规范算法模型接口(IBIS-AMI)的建模和仿真。然而,迄今为止,IBIS-AMI 建模只支持同步系统,即发射机和接收机共享同一个公共参考时钟源。但是在实际应用中,更多的系统采用异步模式工作,即发射机和接收机的参考时钟之间有一定的频率偏移。在发射机和接收机之间有频率偏移时,时钟数据恢复(CDR)特性无法通过仿真得到验证。因此,用户无法精准评测频率偏移的影响, 导致对系统性能的估计可能过于乐观。

为了精确地仿真串行链路,除了需要设置抖动和噪声等系统参数之外,还必须精确建立链路通道和 SerDes(或其他有源元器件比如继电器或重计时器)的模型。在 SerDes 内部,我们需要建立前馈均衡(FFE)、持续时间线性均衡(CTLE)、决策反馈均衡(DFE)和 CDR 的特性模型,同时包含硬件和自适应。模型内还要体现出减损和设计折中。然而,此类信息通常是 SerDes 供应商的专有信息,不可能提供给系统工程师。这就给系统仿真带来了一个挑战。

另一个挑战是模型互操作性。由于很多应用场景中通常都需要第三方 SerDes IP,因此需要建立一个通用接口标准,以便进行互操作性仿真。还有一个挑战是仿真速度。由于大多数设计技术指标是在 1e-12 或更低的比特误码率(BER)上定义的,设计人员需要运行几百万比特,才能在非常低的 BER 水平下预测链路性能,并且达到比较出色的统计置信度。

IBIS-AMI 标准已经很好地解决了上述挑战。通过定义一个通用的 SerDes 模型接口,IBIS-AMI 标准允许 SerDes 厂商将 SerDes 特性封装在模型可执行文件中,而不会暴露它们的 IP。系统设计人员可以使用这些模型进行端到端链路仿真。另外,在 AMI 仿真中,假定模拟通道是线性时不变(LTI)的,可以由脉冲响应表现出来。那么可以使用高效的卷积方法来计算通道输出端的信号波形。这样就可以在几分钟内完成几百万比特的仿真,实现在低比特误码率下以良好的置信度准确预测链路性能。

本文介绍了对当前 IBIS-AMI 仿真流程进行修改,以便在特定频率 PPM 偏移下仿真异步系统的详细内容。文中提供了 IBIS-AMI 基础的背景信息,并着重介绍了串行接口链路分析以及 PLL 和 CDR 的基础知识。随后,本文详细介绍了如何修改现有系统,以便将仿真范围从单纯的同步系统扩大到同步和异步系统都包括在内。借此, IBIS-AMI 建模向更全面的解决方案又迈进了一步。

本文提供了使用修改后的平台分析异步链路的示例,还举例说明了如果忽略有频率偏移时的 CDR 性能,那么对链路裕量的估计很可能会过于乐观。新提出的 IBIS-AMI 平台将可以帮助业界更好地分析链路性能和编制系统设计预算。

2. IBIS-AMI 建模基础知识

本章节简单介绍了 NRZ 链路的 IBIS-AMI 建模。AMI 定义 SerDes 行为建模接口和一种高效的通道仿真方法。串行链路包括一个发射机、一个物理通道和一个接收机。每个 SerDes 设备(发射机或接收机)都可以用一个IBIS-AMI 模型表示,包括模拟和算法部分。模拟部分是一个普通的 IBIS 模型,而算法部分是数据流模型的一个可执行动态链接库 (DLL)。

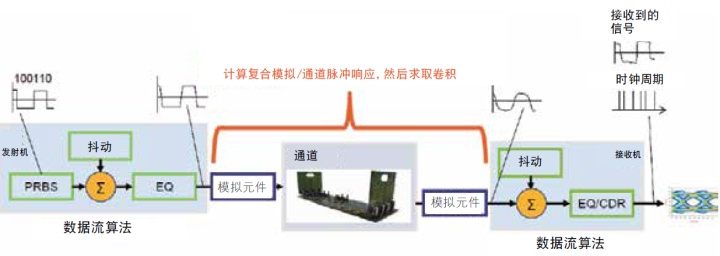

在典型的发射机模型中,模拟部分建立了升降波形,输出阻抗,以及信号还原 DLL 的模型。在典型的接收机模型中,模拟部分呈现输入终端,AGC 功能 DLL、均衡化(比如 CTLE、FFE 和 DFE)以及 CDR。将发射机 DLL 输出作为理想的电压源,而假设接收机 DLL 输入有很高的阻抗。因此,通过电子方式将 DLL 从模拟通道上解耦,其中包括发射机模拟模型、物理通道和接收机模拟模型。另外,假设模拟通道为 LTI,因此可以由合并的模拟通道脉冲响应表示。图形表示如图 1 所示。

图 1.IBIS-AMI 建模的图形显示

在 AMI 仿真中,发射机 DLL 输入是一个方波,在 0.5V 与 -0.5V 之间切换,表示数据模式。发射的数据速率通过 AMI 参数 bit_time 和 sample_interval 控制。利用模拟通道脉冲响应求取发射机输出的卷积。在卷积计算中可以采用高效的 FFT 算法。产生的信号是接收机 DLL 的输入,后者会对信号施行均衡化和 CDR,并返回均衡化的信号和恢复的时钟。

接收机侧的预期数据速率也是根据 AMI 参数 bit_time 和 sample_interval 确定。接收机输出在每个时钟时间被采样,并与 0 V 参考电压和发射比特进行比较,从而计算 BER。如果接收机 DLL 有 AMI_GetWave 函数,接收机信号处理会在函数内进行。在典型设置中,接收机输入波形分为两段。仿真器重复调用 AMI_GetWave,利用每段波形顺序作为每次函数调用的输入,直到处理完所有分段。恢复的时钟周期信息通过 AMI 参数 clock_ times 从接收机 DLL 传递到 EDA 工具。

请注意,发射机与接收机之间的频率偏移未得到显式处理,因此现有平台无法处理异步链路仿真。这就是本文中所讨论并且试图实现的内容。

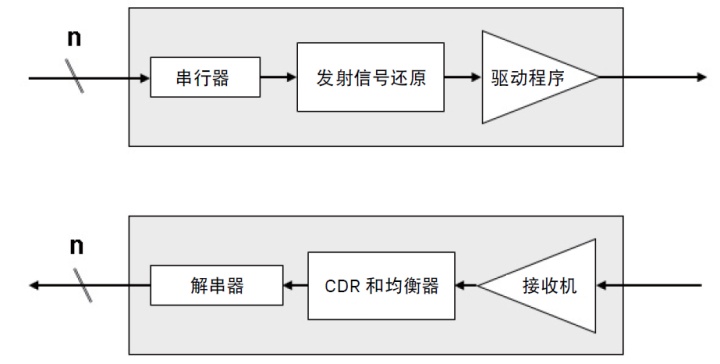

3. 同步和异步系统

在本文中,我们只讨论嵌入式时钟输入/输出体系结构,例如 SerDes。SerDes 是一个接口 IC,能够在发射机端将 n 比特并行数据转换为串行数据,并在接收机端将该串行数据再转换回 n 比特并行数据。SerDes 的发射机端有串行器、去加重和线路驱动器。接收机端有时钟和数据恢复(CDR)电路、均衡器和串并转换器。参见图 2。

图 2. SerDes 框图。 3.1 同步和异步系统

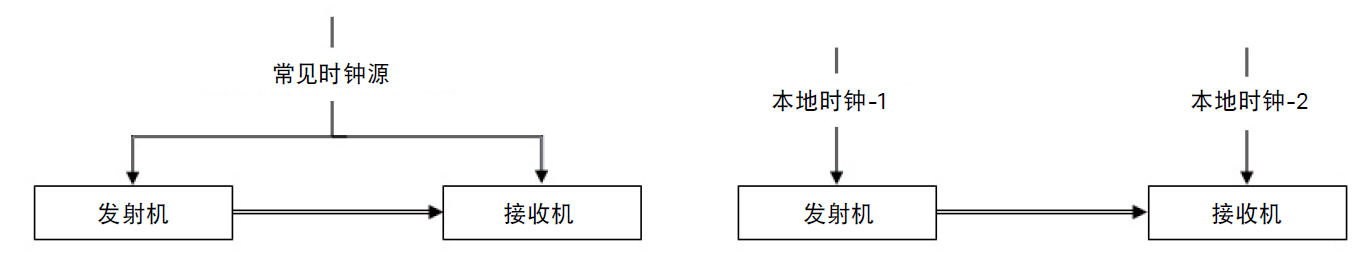

在 SerDes 体系结构中,没有与数据一起发送的显性时钟;时钟信息通过数据转换嵌入到数据中。不同的应用使用不同的协议。SONET、USB、以太网和 PCIe 是常见的串行接口。每个串行接口可以划分到同步组或异步组。

如图 3 所示,同步串行接口让发射机和接收机共享一个公共参考时钟。也就是说,发射机和接收机的归一化参考时钟频率是同一个。经过一段时间后,由于温度或电压等环境因素的变化,合成器输出时钟频率可能会发生漂移,但接收机一侧看到的频率与发射机一侧看到的频率是一致的。接收机中的 CDR 只需要跟踪由于噪声和抖动而在发射机与接收机之间发生的即时相位变化。

另一方面,异步串行接口是指发射机和接收机有不同的参考时钟,其值可能会有一些较小的差异,通常为 ppm (百万分之几,即在归一化频率上,发射机和接收机归一化频率之差)。如果发射机和接收机参考时钟来自不同的板载时钟合成器,就认为该系统为异步系统(或准同步系统)。即时在较短的时间内,也无法保证接收机时钟频率与发射机时钟频率相同。由于两个时钟合成器在温度、电压或工艺上的差异,两个时钟频率之间可能会存在平均 PPM 偏移。接收机中的 CDR 不仅需要跟踪即时相位差,还需要补偿两侧的频率差。

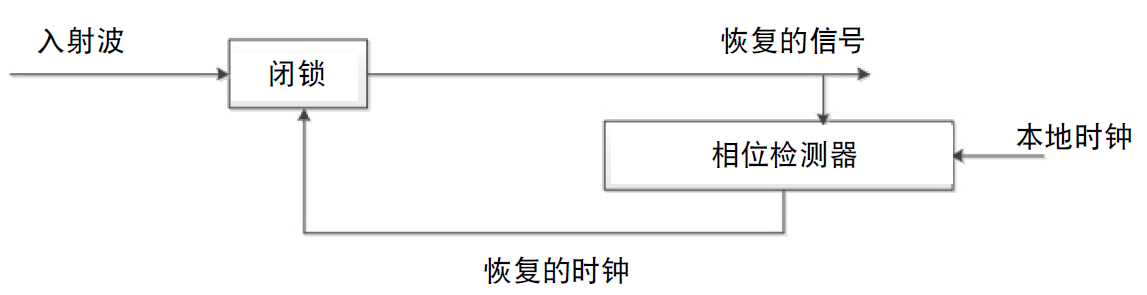

图 3. 两个时钟体系结构3.2 时钟数据恢复

SerDes 中的 PLL 有两个作用,一个是实现本地时钟频率与参考时钟频率的同步,另一个是倍频参考时钟频率,使之达到实际数据速率。在同步系统中,接收机 PLL 和发射机 PLL 使用相同的参考时钟,而在异步系统中,接收机 PLL 和发射机 PLL 的参考时钟频率可能不同。一种时钟恢复方法是让接收机端的相位频率检测器(PFD)直接调整 PLL 频率。如果没有数据或锁,内部 PLL 通常会将频率/相位锁定到参考时钟上。一旦SerDes 接收机开始接收数据,PFD 就会比较 PLL 时钟的频率和相位,以生成误差信号,进而使用此信号通过在比特中心或多或少地采样输入数据来调整 PLL。图 4 显示了计时恢复的一般概念。

图 4. 计时恢复的一般概念。

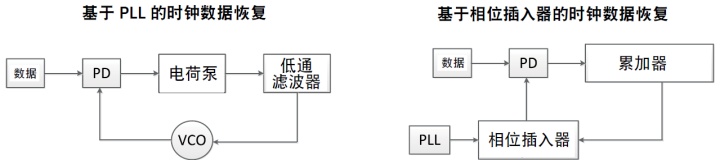

另一种方法是采用相位插入器 (PI) 模块,调节本地 PLL 的接收机采样时钟相位,从而跟踪和匹配发射机频率和相位。这两种方法的框图如图 5 所示。PD 是相位检波器,通常在不同架构下差异很大。

基于 PLL 的时钟数据恢复 基于相位插入器的时钟数据恢复

相位检测器

图 5.基于 PLL 和基于相位插入器的时钟数据恢复比较

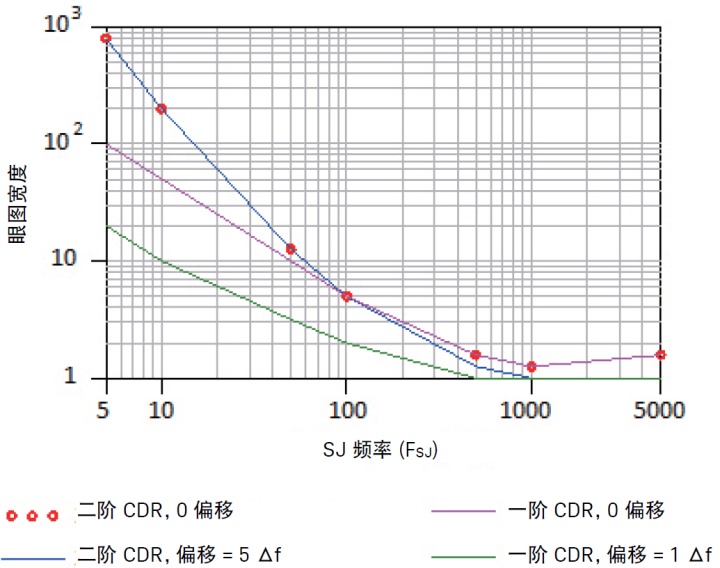

常用的 CDR 可以分为一阶或二阶 CDR。一阶 CDR 可以跟踪回路带宽内和回路增益范围内的相位偏移,但如果系统中存在频率偏移会导致相位误差。频率偏移越大,相位误差就越大。二阶 CDR 可以在跟踪范围内跟踪不包含相位误差的频率偏移。在本文中,我们将使用基于 PI 的时钟数据恢复作为示例,阐述异步系统中的时间恢复行为。基于 PLL 的时间恢复分析非常类似。 3.3 对系统性能的影响

对于异步系统,频率偏移 PPM 必须得到很好的控制。如果系统裕量很小,需要保证较小的 PPM 偏移和/或必须使用二阶 CDR 来减少裕量损耗。

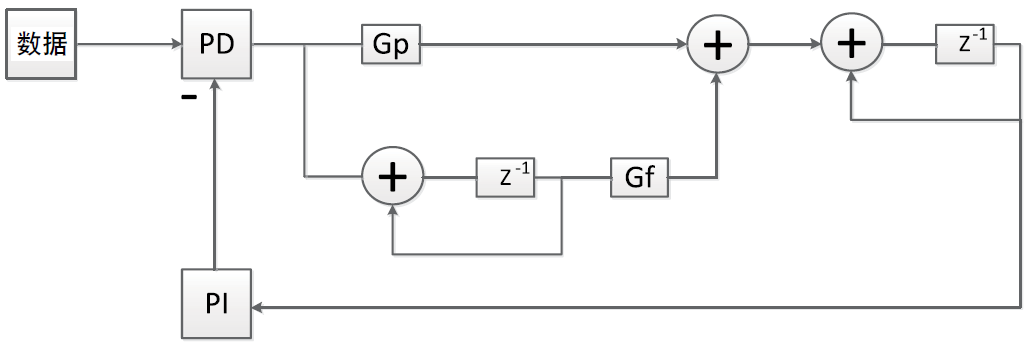

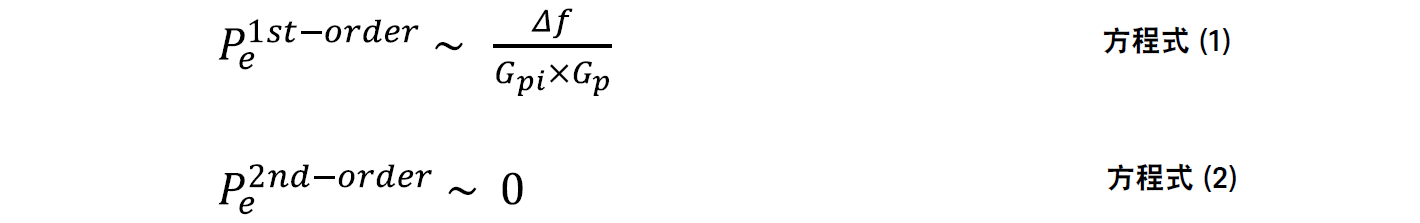

典型的基于 PI 的 二阶 CDR 架构建模如图 6 所示。Gp 为一阶 路径增益,Gf 为二阶路径增益。PD 为相位检波器,而 PI 为相位插入器。当我们可以对 PD 进行合理线性化时,分析系统行为就变得非常简单直接。当 CDR 回路处于锁定模式时,理想情况下,预计 PD 输出、相位误差为 0。值得一提的是,当 Gf 为 0 时,该架构变为一阶 CDR。

图 6.二阶 CDR 框图

由于存在较小的频率偏移,如果 CDR 回路只是一阶,那么稳态下的 PD 输出不会接近 0。如方程式(1)所示,相位误差与 PPM 偏移量级成正比,与 Gp 和 Gpi(PI 增益)成反比。而在使用二阶 CDR 时,相位误差会在 PI 分辨率内减少到一个很小的值,如方程式(2)所示。此处,Pe 是相位误差,Δf 是频率 PPM 偏移。

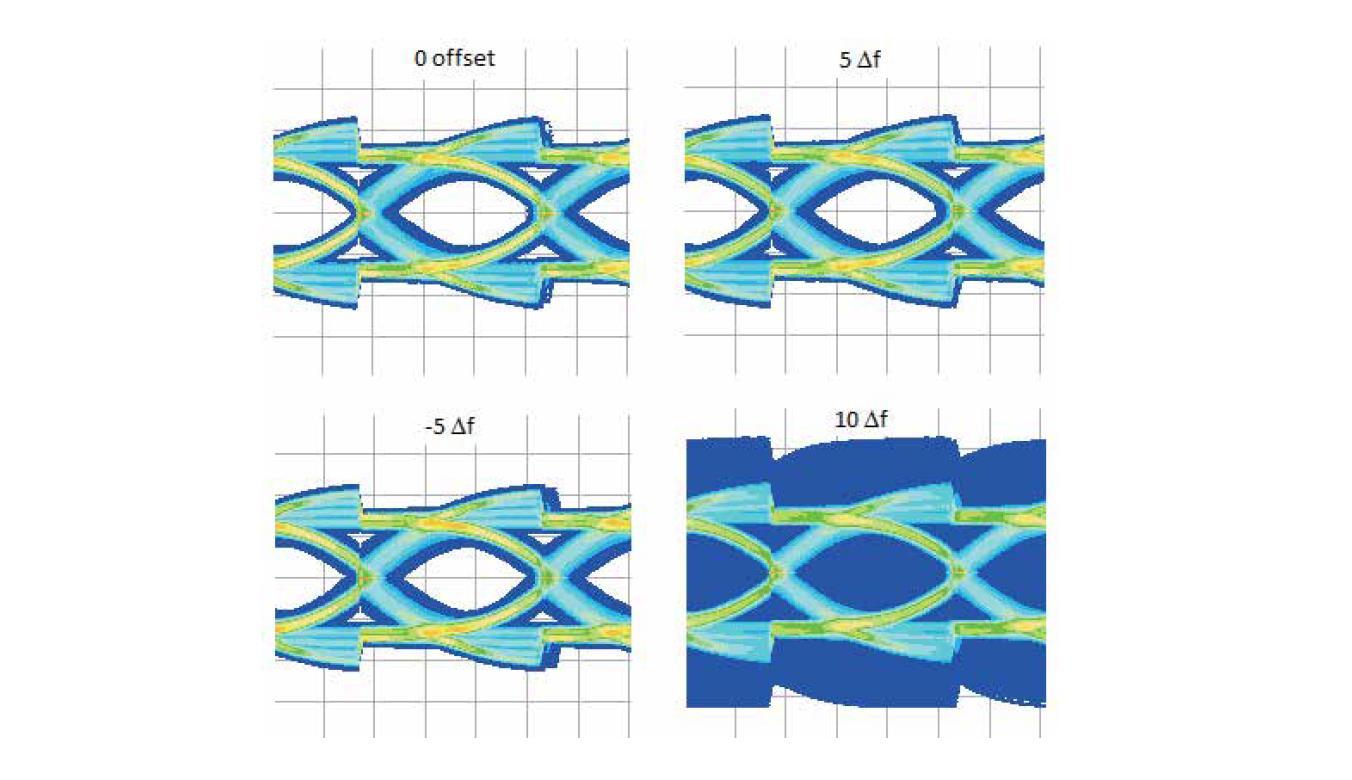

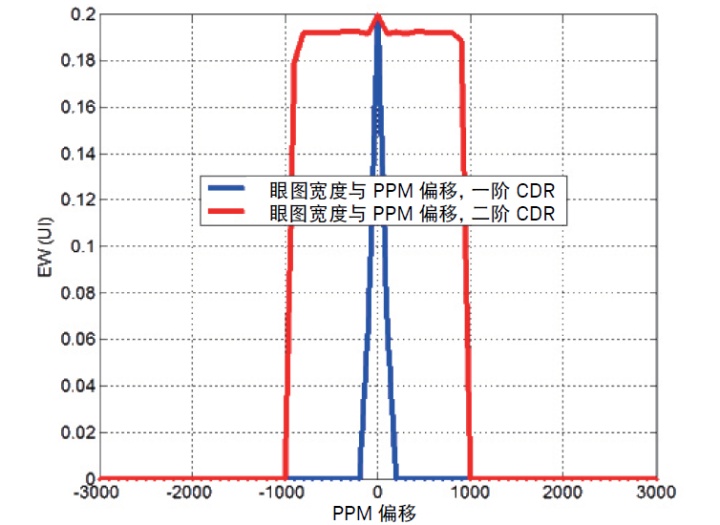

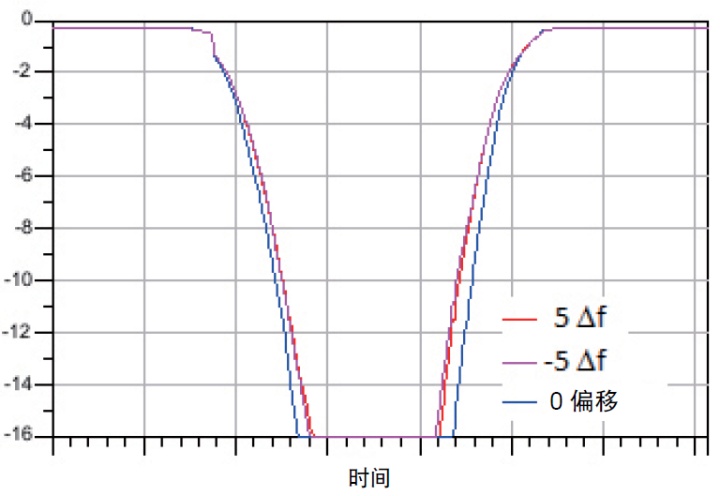

实际上,由于相位环绕的特性,PD 无法跟踪较大的频率偏移,于是相位检测输出可能会出错。即使在二阶路径上,CDR 回路也无法正确收敛。因此,当频率偏移超过 CDR 捕获范围时,CDR 无法再锁定到输入数据,眼图闭合。根据图 6 中给出的简单体系结构模型,可以从图 7 中的时域仿真看到该特性。

图 7. 眼图宽度由一阶和二阶 CDR 的 PPM 偏移决定。

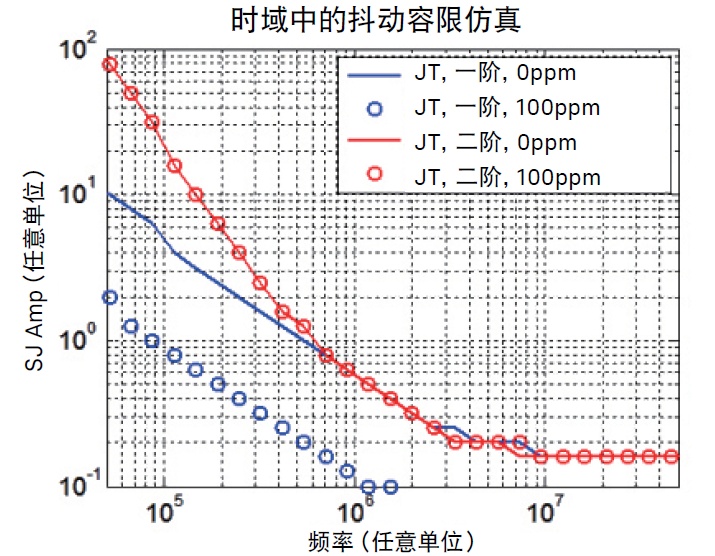

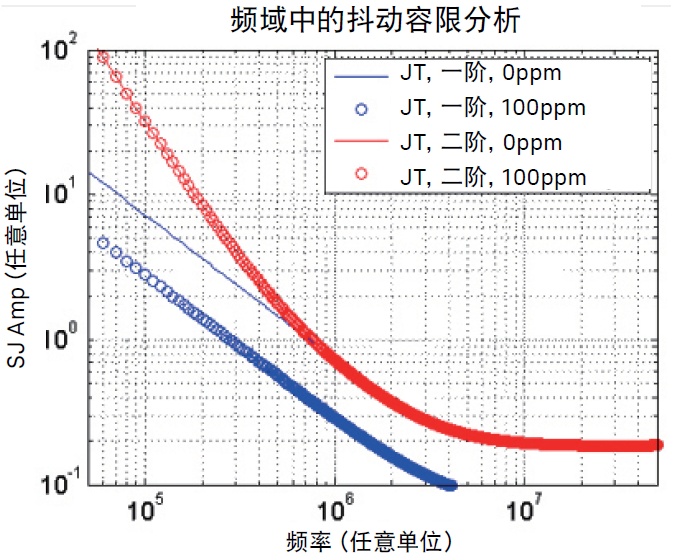

我们从这个简单模型中可以得到的另一个见解是抖动容限。众所周知,CDR 可以跟踪最高达到其带宽的低频抖动。在极低频率抖动下,二阶 CDR 回路尤为有用,因为在其抖动传递函数中引入了二阶极点。此外,一阶CDR 抖动容限在异步系统中也有所折中,而二阶 CDR 几乎不受影响。这可以在小信号分析或简单时域仿真中观测到,如图 8 所示。

尽管在有频率偏移和正弦抖动时,简单的体系结构模型可以在很大程度上预测 CDR 的特性,但用户仍需要时域仿真,以求能够提高预测的准确性,并说明 SerDes 系统中各种自适应回路间的复杂收敛和交互。这就是IBIS-AMI 仿真的用武之地。

异步系统的 IBIS-AMI 仿真

图 8. 时域和频域中的抖动容限分析。

4 异步系统的 IBIS-AMI 仿真

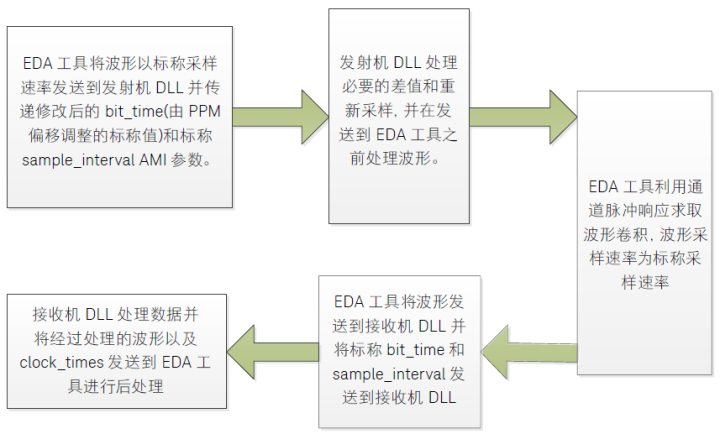

现有的 IBIS-AMI 标准支持系统级仿真,但不明确要求适用于异步系统。我们利用接收机模型和发射机模型之间的独立性,通过 EDA 平台应用异步参考时钟。通过改变 AMI 参数输入 bit_time 和 sample_interval,可以将参考时钟频率偏移应用到发射机侧或接收机侧。如果应用在发射机侧,AMI_Init 调用中的 bit_time 变量值就是实际的发射机参考时钟频率,由相对于标称数据速率的发射机频率偏移决定。此外,发射机 DLL 的输入数字激励的理想单位间隔(没有发射机抖动)等于实际发射机参考时钟频率的倒数。如果应用在接收机侧,AMI_Init 调用中的 bit_time 变量值是实际的接收机参考时钟频率,由相对于标称数据速率的接收机频率偏移决定。注意, 在这两种情况下,AMI_Init 调用中的 sample_interval 变量值都不需要依赖任何实际参考时钟频率。

如果发射机和接收机使用相同的 sample_interval,那么由于 PPM 偏移较小,发射机和接收机之间每比特采样数可能不同,并且可能不是整数。尽管 IBIS-AMI 标准要求 DLL 来执行重新采样,但许多 DLL 很可能是预测每比特整数个采样,并且可能预测失败,退出码为 0。

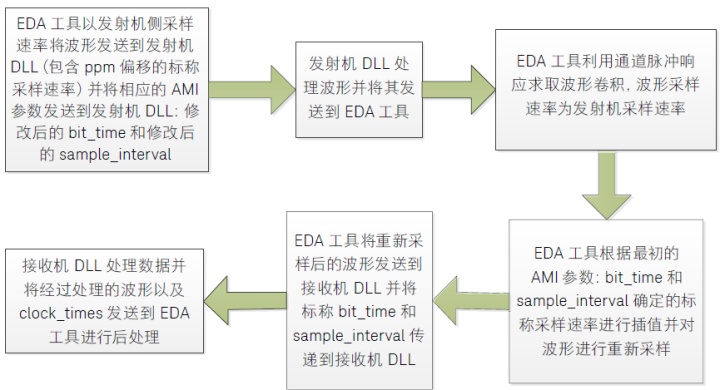

另一方面,如果发射机和接收机使用不同的 sample_intervals 来保持两侧的每比特采样数都为整数,则 EDA 工具需要执行重新采样。例如,EDA 工具以发射机采样速率向发射机发送波形,接收发射机 DLL 输出并通过采样速率与发射机相同的通道脉冲响应对其进行卷积。然后,EDA 工具插入卷积后的输出波形,并对其进行重新采样,从而在将波形发送到接收机 DLL 之前匹配接收机侧的采样速率。

两种方法分别如图 9(a) 和 9(b) 所示,假设发射机侧增加了偏移。本文并不想保证或指出应该采用哪种方法。 (a)

(b)

图 9.(A) 发射机侧增加的频率偏移,发射机 DLL 处理重新采样。

(B) 发射机侧增加的频率偏移,EDA 工具处理重新采样。

5. 异步系统仿真和测量

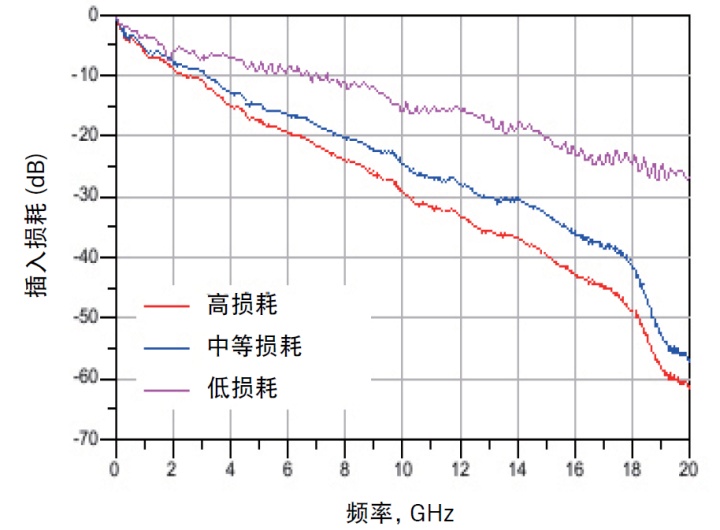

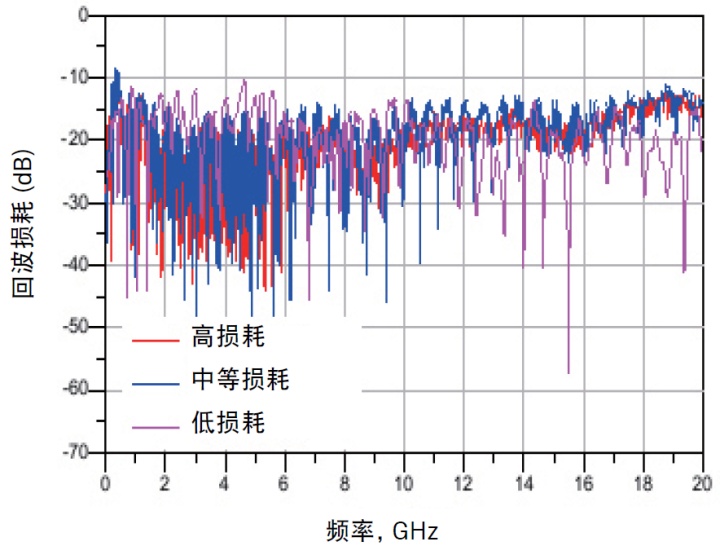

我们分析了三个分别具有高、中、低损耗的通道。这些通道的插入损耗和回波损耗在图 10 和图 11 中显示。三个通道的插入损耗分别是 36 dB、30 dB 和 18 dB。

图 10. 通道插入损耗。

图 11. 通道回波损耗。

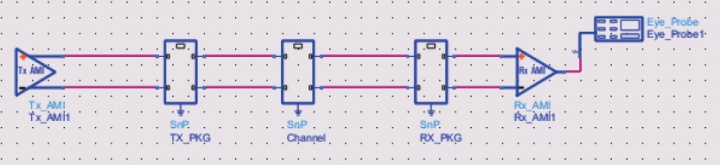

仿真设置如图 12 所示。发射数据包、物理通道和接收数据包用 4 端口 S 参数表示,对它们进行了级联以建立链路模型。标称数据速率是 28 Gbps。每次仿真运行 100 万个 PRBS23 比特。频率 PPM 偏移在 EDA 工具内部设置,因此仿真台的接口看起来与同步链路的传统 IBIS-AMI 仿真相同。

发射机模型实施 3 接头 FIR,以进行去加重。接收机模型实施自适应 CTLE、AGC 和 DFE。在本研究中,中高损耗通道使用相同的发射机均衡器设置,低损耗通道使用不同的设置。接收机模型中的默认 CDR 为二阶。该模型有一个参数旋钮,可以在一阶和二阶之间切换 CDR。在此示例中,参考时钟偏移通过 EDA 施加在发射机侧。正向偏移是指发射机一侧的数据速率高于接收机一侧的数据速率。表示的所有频率偏移都是相对于参考偏移 Δf 测得的。

图 12. 异步链路的仿真设置。

5.1 高损耗通道

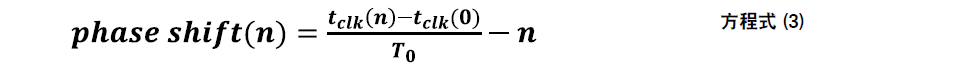

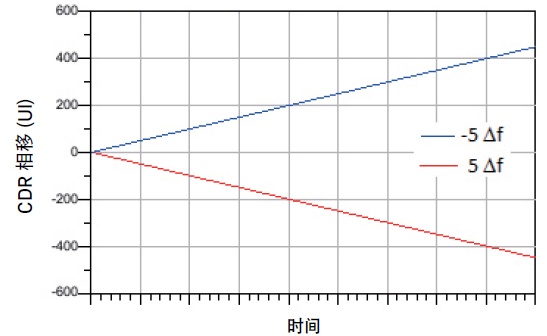

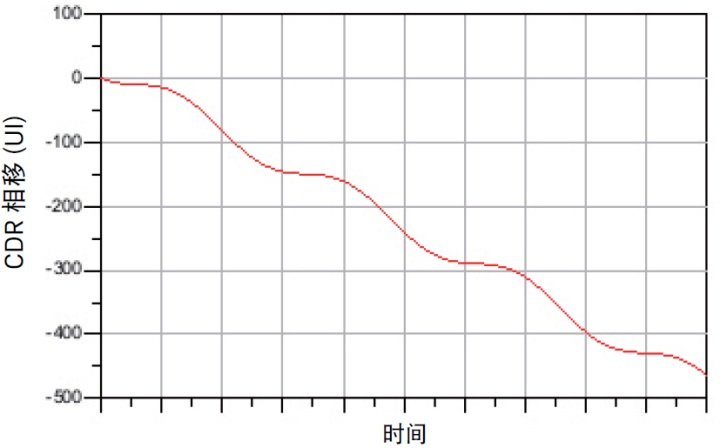

在高损耗通道中,CDR 相移随时间而变化,在 5 和 -5 参考偏移 Δf 下相对于标称数据速率的频率偏移如图 13 所示。CDR 相移定义为

其中,tclk(n) 是接收机 AMI_GetWave 调用返回的第 n 个时钟时间,T0 是标称单位间隔,在本例中为 1/28G 或 35.71 ps。图 13 显示 CDR 会跟踪 5 和 -5 Δf 参考偏移下的发射机频率偏移。结果是,眼图打开,且与没有频率偏移(同步通道中)时的眼图相同,参见图 14 中的眼图。

图 13. 高损耗通道中的 CDR 相移。

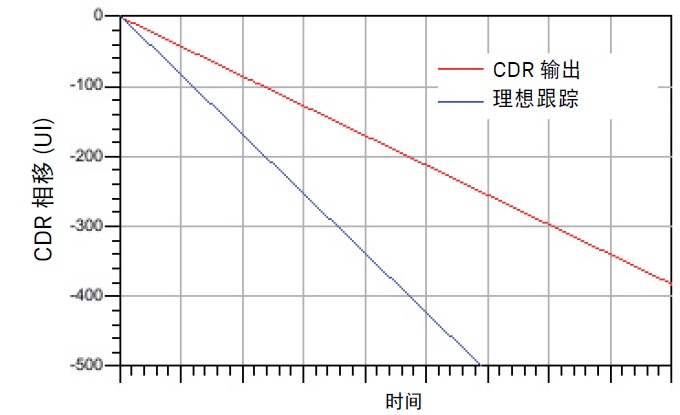

图 14 还显示了在 8.5 Δf 频率偏移下,眼图是闭合的。在该偏移下的 CDR 相移(图 15)表明,CDR 与发射机频率偏移不完全一致,并且是数据锁定时的输出,因此导致眼图闭合。红线为实际的 CDR 输出相移。蓝线是在 CDR 完全跟踪发射机频率偏移时的假设理想相移。

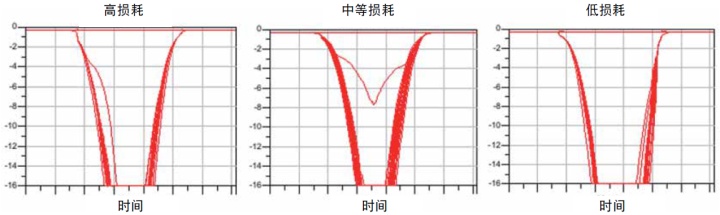

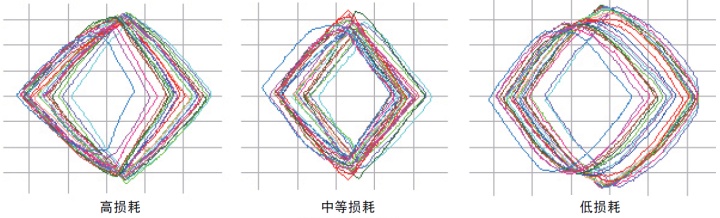

图 14. 频率偏移为 0、5、-5 和 8.5 参考偏移 Δf 时的高损耗通道眼图。

图 15. 频率偏移为 8.5 参考偏移 Δf 时的高损耗通道 CDR 相移。

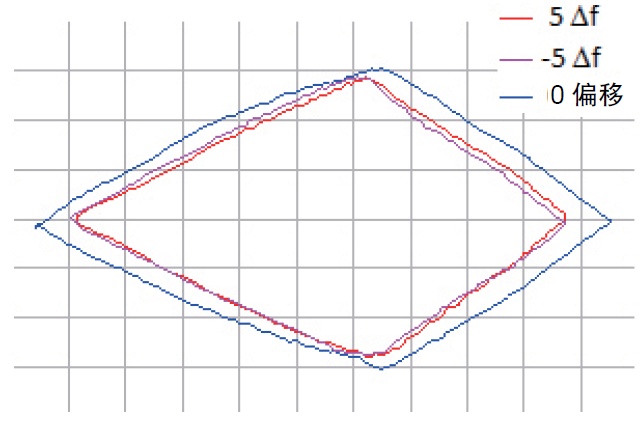

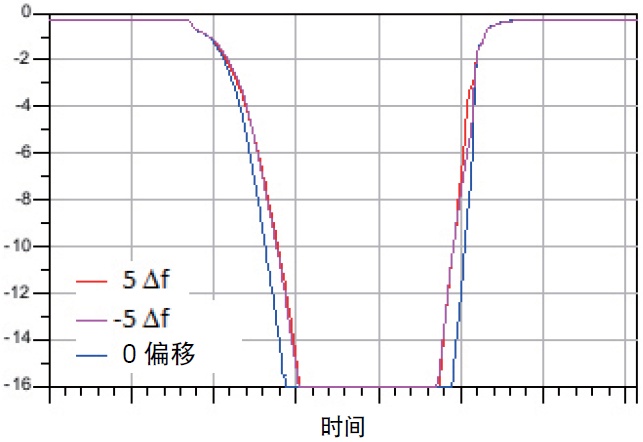

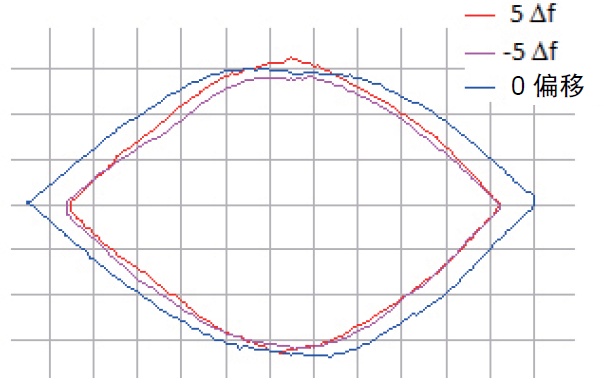

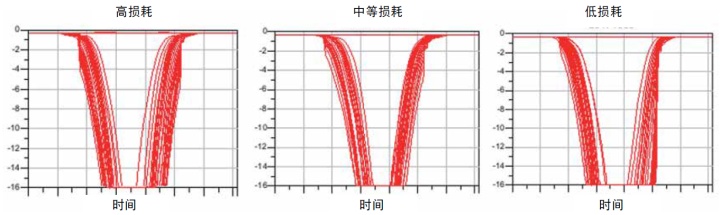

图 16 和图 17分别显示了在频率偏移为 0、5 和 -5 参考偏移 Δf 且比特误码率为 10-12 时的计时 bathtub 曲线和眼图等高线。通过与同步通道(0 偏移)中的数据进行比较可知,在异步通道(有 5 和 -5 Δf 偏移)中,频率偏移引入了轻微的额外计时收敛。

图 16. 高损耗通道中的计时 bathtub 曲线。

图 17. 高损耗通道中比特误码率为 10-12 时的眼图等高线。5.2 中等损耗通道

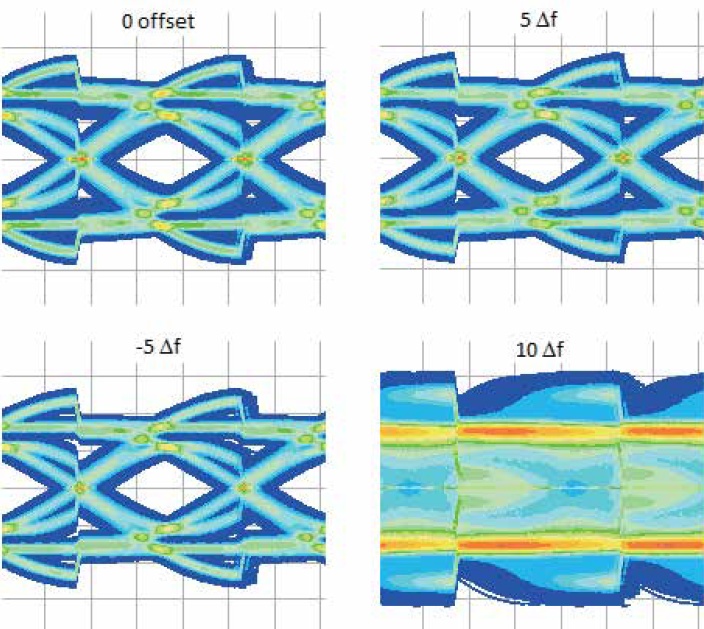

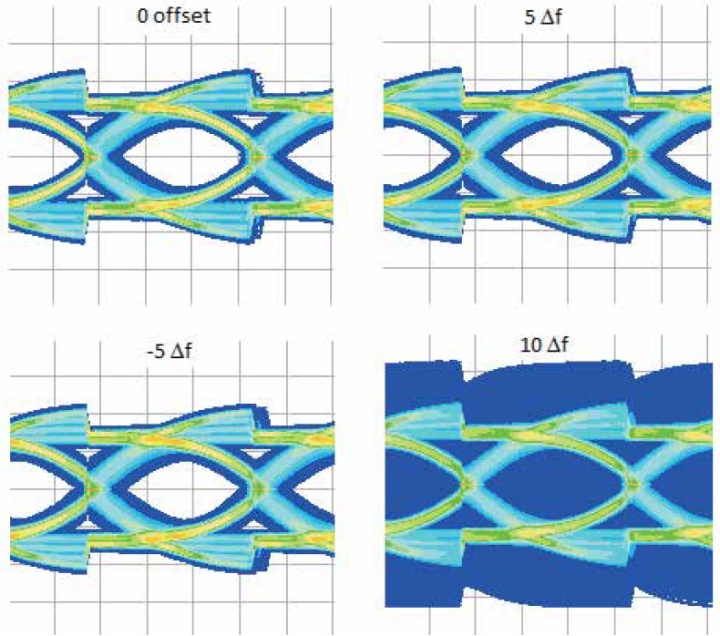

图 18 显示了频率偏移为 0、5、-5 和 10 参考偏移 Δf 时中等损耗通道的眼图。在 10 Δf 下,CDR 未能跟踪频率偏移,眼图闭合。

图 18. 不同频率偏移时的中等损耗通道眼图。

图 19. 中等损耗通道的计时 bathtub 曲线。

图 19 和图 20 分别显示了在频率偏移为 0、5 和 -5 参考偏移 Δf 且比特误码率为 10-12 时的计时 bathtub 曲线和眼图等高线。我们再次看到,使用二阶 CDR 回路时,只要它位于频率捕获范围内,有频偏时的裕量损耗就会很小。

图 20. 比特误码率为 10-12 时的中等损耗通道的眼图等高线。5.3 低损耗通道

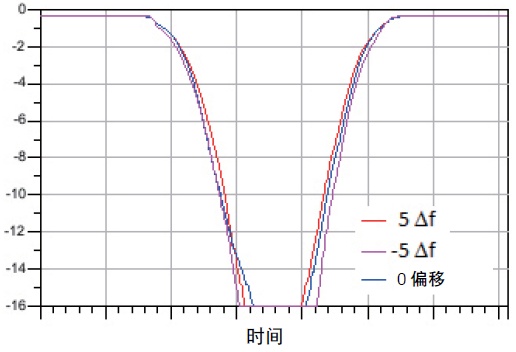

图 21 显示了频率偏移为 0、5、-5 和 10 参考偏移 Δf 时低损耗通道中的眼图。在频率偏移为 10 Δf 时,接收机 CDR 未能跟踪发射机频率偏移并且眼图闭合。图 22 和图 23 分别显示了在频率偏移为 0、5 和 -5 参考频率偏移 Δf 且比特误码率为 10-12 时的计时 bathtub 曲线和眼图等高线。此处可以对裕量损耗得出相同的结论。另外还要注意的是,正负 PPM 偏移下的相移非常小。

图 21. 具有不同频率偏移的低损耗通道眼图。

图 22. 低损耗通道中的计时 bathtub 曲线。

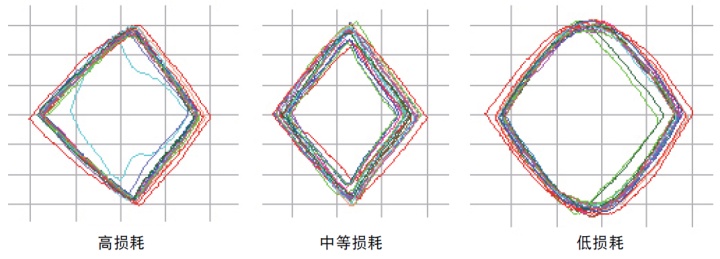

图 23. 低损耗通道中,比特误码率为 10-12 时的眼图等高线。5.4 频率偏移容限

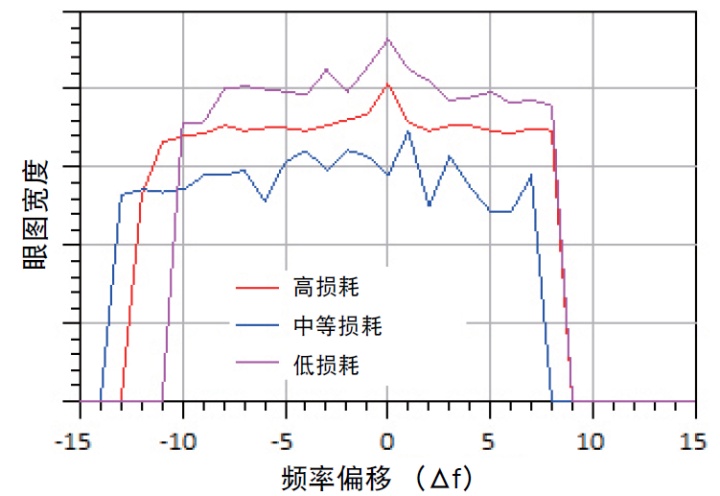

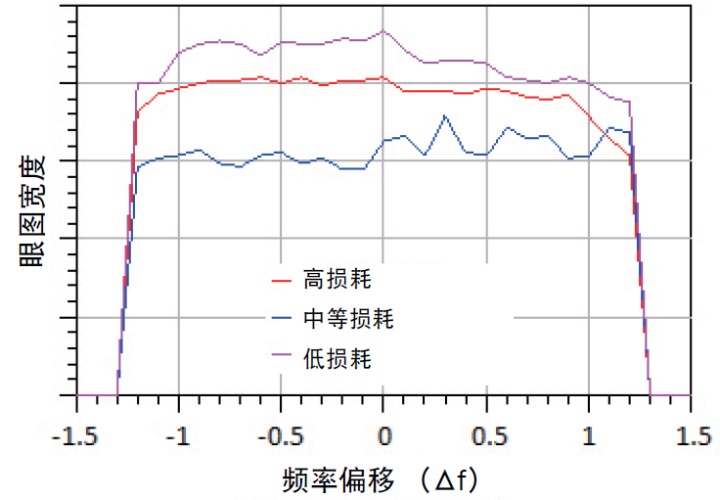

图 24 显示了在比特误码率为 10-12 时,三个通道在不同频率偏移下的眼图宽度。可以看出,CDR 能够跟踪 -11 Δf 与 8 Δf 之间的偏移。在同样的发射机侧和接收机侧均衡设置下,高损耗通道的均衡度似乎要比中等损耗通道更好一些,导致眼图宽度稍大。

图 25 和 26 显示了在 +/-15 Δf 频率偏移之间、比特误码率为 10-12 时的计时 bathtub 曲线和眼图等高线。我们可以再次看到,在捕获范围内,频率偏移对二阶 CDR 系统有影响,但相对较小。

图 24. 比特误码率为 10-12 时,不同频率偏移下的眼图宽度。

图 25. 不同频率偏移下,三个通道中的计时 bathtub 曲线。

图 26. 在 +/-15 Δf 频率偏移范围内、比特误码率为 10-12 时,三个通道的眼图等高线。

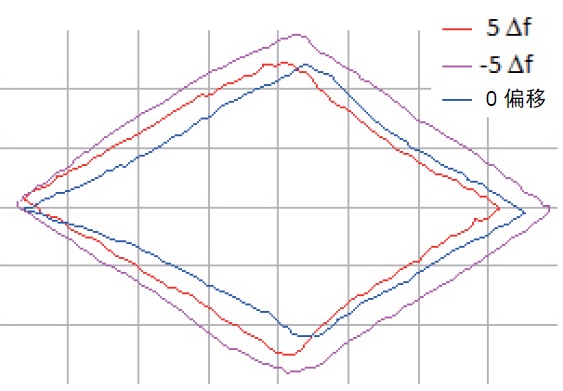

为了比较一阶 CDR 与二阶 CDR 之间的频率偏移容限,图 27 显示了比特误码率为 10-12 时,一阶 CDR 在不同频率偏移下的眼图宽度。结果表明,对于全部三个通道来说,一阶 CDR 只能跟踪 +/- 1.3 Δf 之间的偏移。一阶 CDR 中的频率偏移容限远低于二阶 CDR 中的频率偏移容限。请注意,EW 在捕获范围内看起来比较平坦, 但实际上并不是如此(与图 6 中的理论分析结果一样)。锁定点受到 PPM 偏移的严重影响(图 28),因此有效 EW 与 PPM 偏移成比例降低。

利用一阶 CDR 在 10-12 BER 下的 时间浴缸曲线和眼图等高线,在频率偏移 -1.5 与 1.5 参考偏移 Δf 之间时如图 26 所示,在频率偏移介于 -1.5 与 1.5 参考偏移 Δf 之间时如图 29 所示。未显示 BER 下关闭的眼图。当ppm 偏移偏向正方向时,眼图向左偏移,导致右侧的水平眼图裕量越来越少。同样,当 ppm 偏移偏向负方向时,眼图向右偏移,导致左侧的水平眼图裕量越来越少。这与二阶 CDR 系统相反,在二阶 CDR 系统中,只要ppm 偏移位于捕获范围内,眼图就不会偏移。

图 27. 在采用一阶 CDR 时,1e-12 BER 下的眼图宽度与频率偏移比较

图 28. 在采用一阶 CDR 时,三个通道的时间浴缸曲线

图 29. 在采用一阶 CDR 时,三个通道在 1e-12 BER 下的眼图等高线

5.5 频率偏移对抖动容限的影响

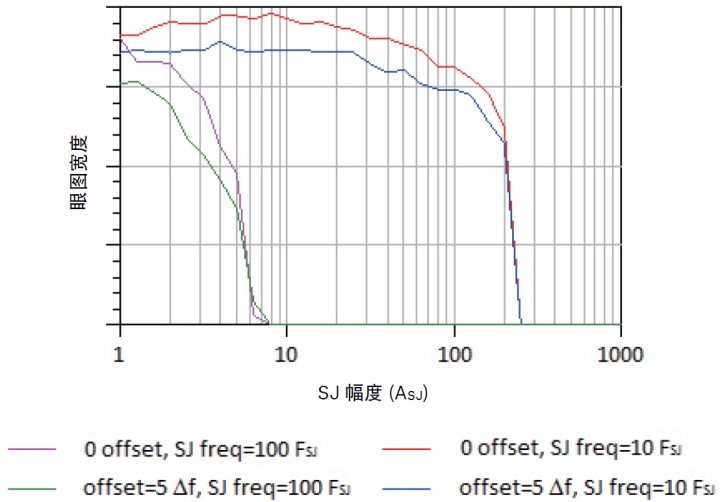

为了研究频率偏移对接收机抖动容限的影响,向发射数据流中注入正弦抖动(SJ)。在本文中,所有 SJ 频率都是相对于参考频率 FSJ 测得的,而所有 SJ 幅度都是相对于参考幅度 ASJ 测得的。

图 30 显示了当频率偏移为 5 参考偏移 Δf,发射机 SJ 频率为 10 参考 SJ 频率 FSJ 时的高损耗通道 CDR 相移。结果表明,CDR 同时跟踪发射机频率偏移和发射机 SJ。

图 30. 高损耗通道中不同频率偏移下的 CDR 相移。

图 31. 高损耗通道中,比特误码率为 10-12 时,不同发射机 SJ 幅度下的眼图宽度。

高损耗通道中,在发射机 SJ 频率为 10 和 100 F SJ 且频率偏移为 0 和 5 Δf 时,在1 ASJ 至 1000 ASJ 之间扫描发射机 SJ 幅度。比特误码率为 10-12 BER 时,不同发射机 SJ 幅度下的眼图宽度如图 31 所示。在两个 SJ 频率上,频率偏移都减小了眼图宽度。对于特定眼图宽度阈值,两种频率偏移下,CDR 能够允许的最大 SJ 幅度大约为 200 ASJ(SJ 频率为 10 FSJ)和 5 ASJ(SJ 频率为 100 FSJ)。

图 32 显示了高损耗通道对二阶 CDR 和一阶 CDR的 CDR 抖动容限。对于二阶 CDR,频率偏移对抖动容限的影响几乎可以忽略。对于一阶 CDR,频率偏移的影响较为明显,而且发生在整个发射机 SJ 频率范围内。

图 32. 高损耗通道中,CDR 在不同 SJ 频率下能够允许的最大发射机 SJ 幅度。

6. 结论和未来的工作

本文中,我们提议了一种改进的异步链路系统 IBIS-AMI 模型仿真流程。在发射机或接收机侧均可以建立发射机和接收机之间参考时钟频率偏移的模型。AMI_Init 函数的 bit_time 输入值是实际的参考时钟周期,而发射机DLL 的输入数字激励的标称单位间隔则是实际发射机参考时钟频率的倒数。

我们通过对具有不同损耗的三个异步通道进行仿真,验证了所提议方案的可行性。结果表明,频率偏移可以导致计时偏差并减少链路裕量。我们发现二阶 CDR 比一阶 CDR 具有更出色的频率偏移容限。与预测的一样,频率偏移还会影响 CDR 抖动容限。

在有抖动和频率偏移的情况下,仿真系统性能的能力高低对制定系统级计时预算非常重要。这样做比只是将链路视为同步链路更加贴近实际结果。我们采取的近似法就是假设通道响应的变化只是偏移了几 PPM,可以忽略不计,如果典型系统中的 PPM 偏移较小,这一假设是十分合理的。

当信号频率经由低频周期性信号调制以减少电磁干扰(EMI)干扰时,我们提出的仿真方案原则上可以扩展到扩频时钟(SSC)的情况。在 PCIe 和 CCIX 等规范中,允许使用 SSC。复杂之处在于频率不再恒定,而是周期性变化。因此,bit_time(可能还有 sample_interval)需要通过 EDA 工具定期更新。DLL 需要能够执行这种动态变化。这将是未来研究的一个好课题。

相关信息

PathWave 先进设计系统(ADS)2020 更新 2.0www.keysight.com

NEW! ...相对噪声强度(RIN) 光纤衰减 色散 DDR/存储器 全新 DDR5 和 LPDDR5 解决方案采用 IBIS-AMI 建模确保均衡 通过内部相位内插器训练跟踪抖动,实现最佳的 DFE 时钟 对仿真波形进行自动 DDR5 一致性测试 简化存储器设计流程,例如在控制器和存储器中集成封装设置,大大减少接线操作 改进了控制器...

W2225BP ADS Memory Designer 软件套件www.keysight.com

...Spectre 兼容模式)、IBIS 模型库、卷积仿真器(使用频域数据生成时域模型)、通道仿真器(包括逐比特和统计模式、眼图和 BER 轮廓图、IBIS AMI)。 W2307EP 互连工具箱组件 这个互连工具箱组件使您可以优化 PCB 堆叠并设计传输线几何结构。它还提供高精度的过孔设计仿真器,帮助您设计参数化、阻抗匹配的过孔转换(单端和差分)。

W1718EP SystemVue C++ 代码生成器www.keysight.com

...包括测试矢量生成 - 生成包含专有信号处理模块的程序库 - 与其他软件工程平台(不限于以下示例)进行 IP 集成 是 SystemVue W1714 AMI 建模套件的先决条件。该套件能够生成可转移的 IBIS-AMI 高速 SerDes 模型,在行业标准的 SI 信道仿真器中使用。

W2210BP ADS 核心、瞬态卷积、通道软件套件www.keysight.com

...先进的时域组件包含瞬态仿真器(SPICE 瞬态分析包括 HSPICE 和 Spectre 兼容模式)、IBIS 模型库、卷积仿真器(使用频域数据生成时域模型)、通道仿真器(包括逐位和统计模式、眼图和 BER 轮廓、IBIS AMI)、前面板(包括抖动分解)、加密型 HSPICE 协同仿真界面和宽带 SPICE 模型生成器。

139

139

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?