ICDREAM期望能给您带来更多有价值、有深度的信息!

ICDREAM力图打造成为集成电路圈提供生活、学习、工作、合作等信息的专业平台,敬请关注!

拒绝芯片后端设计外包,自己的芯片自己做!

该技术文档由ICDREAM独家整理发布。

整理不易,欢迎转发。

算术逻辑部件主要处理算术运算指令和逻辑运算指令,它的核心单元是加法器。这个加法器是影响算术逻辑部件整体性能的关键部分,因为几乎所有的算术运算和逻辑运算,都要通过它来完成。

加法器结构包括串行进位加法器(Carry Ripple Adder,CRA)、进位跳跃加法器(cany skip Adder,CKA),以及较高速度的进位选择加法器(carry select Adder,CSA)、超前进位加法器(Can了Look—a}lead Adder,CLA)和并行前缀加法器(Parallel Prcfix Adder)等。

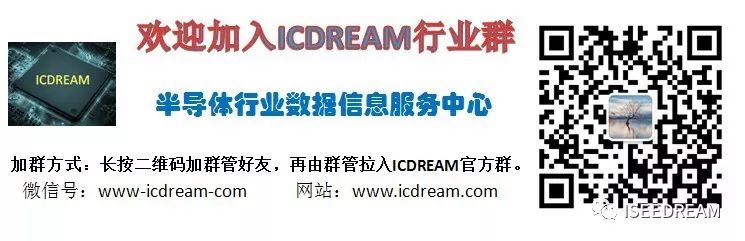

串行进位加法器(CRA)

串行进位加法器是最简单、最基本的加法器结构。串行进位加法器的进位像水波一样依次通过每位,因此也称为“行波进位加法器”。它每次只能进行一位运算,因此速度很慢。如下图所示

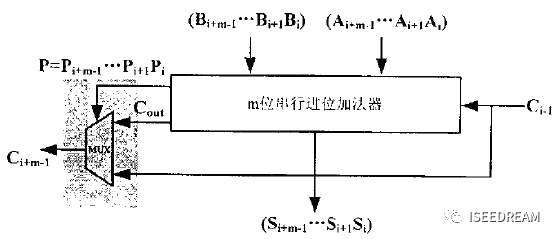

进位跳跃加法器(CKA)

进位跳跃加法器是串行进位加法器的改进结构。它将整个加法器分为几个组,如果某组的所有进位传播信号都为“1”,则将该组的进位输入直接传送到输出,而不需要进行进位运算。这个过程好像进位做了一个跳过该组的动作,因此称为进位跳跃加法器。

为了实现跳跃进位,每组需要增加一个多路选择器和一个与门,这种结构可以提高加法器的运算速度,但是,速度的提高只有在某些特定的情况下才会出现。如下图所示

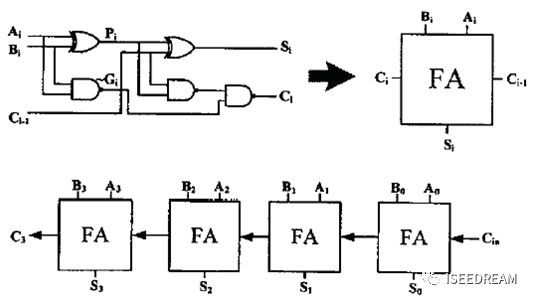

进位选择加法器(CSA)

进位选择加法器采用资源复制的基本思想,用硬件来换取速度。它将整个加法器分为几个组,每组有两条路径,进位输入为“O”和“1”的两种情况通过两条路径同时计算。一旦该组进位输入信号到来,通过多路选择器选择正确的进位输出与和值。如下图所示

由于采用了前瞻的思想,因此进位选择加法器的速度有很大提高。如果整个加法器分为M组,则运算延时可由第一组进位延时、M个多路选择器的延时及一个和产生延时相加得到。进位选择加法器虽然具有较快的速度,但由于它采用了资源复制的方法,因此实现代价也成倍增加。

一般的进位选择加法器每组具有相同的位数,延迟也与位数成线性关系,称为“线性进位选择加法器”。如果不把每组设置为相同的位数,而是从低位到高位组内位数逐渐增大,例如第一组2位,第二组3位,等三组4位,等等。这种逐组位数加长的方法使加法器结构具有亚线性延迟的特性。经过计算,这种结构的延迟与位数的平方根成正比,因此称为“平方根进位选择加法器”。

超前进位加法器(CLA)

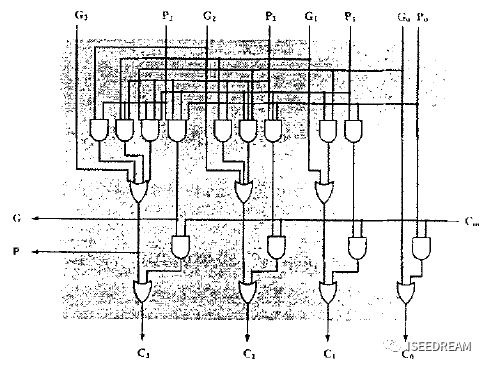

在设计更快速的加法器时,避免逐级进位很重要,但是这一效应仍然以某种形式存在于进位跳跃和进位选择加法器中。超前进位加法器提供了一种解决该问题可能的方法。在超前进位加法器中,当进位输入Cin进入超前进位模块,各级的进位输出将同时产生,每一位的进位输出与和值输出都与前面的位无关,因而有效地消除了逐级进位效应,因此加法时间与位数无关。如下图所示

但是,与位数无关的加法时间只是一种理想的情况,真正的延时至少随位数线性地增加。这是由于当位数Ⅳ增大时,超前进位模块具有很大的扇入,这将使电路结构较复杂;如果用较简单的门来实现,则要求多个逻辑层次。这两种情况都会使传播延时增加。而这种加法器的面积也随着位数增大而迅速增加。因此,超前进位结构常用在位数较小的情况,~般来说位数不大于4。

并行前缀加法器(Prefix)

并行前缀加法器是超前进位的一种改进结构,它将Ⅳ位加法器的进位传播信号层次化地分解为Ⅳ位子组合,并将进位产生和进位传播组织成递归的树型结构。并行前缀加法器使用一种特殊的方式产生各位的进位输出,这种方式称为“前缀运算(Prefix Compu诅tion)”。所有进位产生和传播信号并行地通过前缀运算单元进行运算,同时输出进位信号。各个前缀运算单元通过递归的方式连接起来,即可形成整个加法器。如下图所示

对于N位加法运算,并行前缀加法器最少只需logN步就可完成进位的运算,因此也称为“对数超前进位加法器”。并行前缀加法器的运算速度是各种加法器结构中最快的,同时,它由许多相同的前缀运算单元组成,结构规整,容易实现。由于这些优点,并行前缀加法器成为当前最常用的高速加法器结构。

可以看出,串行进位加法器速度最慢,面积最小:进位跳跃加法器速度有很大提高,而面积只有较小的增加:进位选择加法器和超前进位加法器的速度相差不大,都能达到较快的速度,但超前进位加法器的面积比进位选择加法器大出10倍以上!因此单一的超前进位加法器在位数较大时很不实用,性价比很低,必须与其它结构进行组合;并行前缀加法器速度最快,是进位选择加法器的1.5倍,而其面积却相对增长较少,比进位选择加法器略高,只有超前进位加法器的14%左右。分析结果表明,并行前缀加法器具有速度和面积两方面的优势,是设计时首选的结构。由于并行前缀加法器优秀的性能特性和较小的面积代价,因此得到了广泛的应用。

往期技术文章中可以在如下链接中找到。

20190315芯片设计工程中设计软件问题解决技巧—Cadence Innovus篇

20190219芯片设计工程中设计软件问题解决技巧—Cadence Innovus篇

20190112芯片设计工程中设计软件问题解决技巧—Cadence Innovus篇

20181226芯片设计工程中设计软件问题解决技巧—Cadence Innovus篇。

20181217芯片设计工程中设计软件问题解决技巧—Cadence Innovus篇。

20181113芯片设计工程中设计软件问题解决技巧—Cadence Innovus篇。

芯片设计工程中设计软件问题解决技巧—Cadence Innovus(Encounter) 篇20181108。

芯片设计工程中设计软件问题解决技巧—Cadence Innovus(Encounter) 篇

干货,欧美禁止出口技术!芯片高级技术中标准单元库设计基本技术解密,芯片高性能设计必备!

干货系列!运算放大器的性能指标基本概念。

干货系列!抗噪数字电路设计及参考电路。

干货系列!芯片定制数字电路设计中高扇入电路逻辑的实现结构分析技术。

干货!芯片存储器部件基本设计技术曝光。

干货!数字后端单元库设计中使用abstract工具从LAYOUT中生成LEF技术操作细节曝光!

数字后端布局布线中重要库数据LEF介绍,深入了解LEF是老司机的基本功之一!

版图(layout)与电路设计(schematic)Virtuoso实战流程扫盲介绍。

PLL(锁相环)基础知识介绍。

IO基础知识介绍。

关于 ICDREAM

www.icdream.com诞生于2010年,通过8年的沉淀已经成为业内首屈一指的专业论坛,成为行业内数万资深工程师信息交互、分享的首选平台。

2018年论坛正式升级成为中国半导体行业数据信息服务中心。为行业内50万从业工程师,1500家业内企业,提供更全面,更专业,更精准,更深度的数据信息服务。

1979

1979

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?