首先简单的说一下什么是IP核,它可以理解成Altera公司自己开发的一些接口模块,可实现相应的功能,用户在实现该功能的时候可以直接调用相应的IP核即可,不用再重新编写相应的底层代码。说白了它就类似于Matlab中封装好的函数,用户在使用过程中可以直接调用相应的函数,极大降低了编写程序的难度。

废话不多说,这里直奔主题。我们在Quartus II软件中调用的IP核分为两大类,一类是免费的IP,不需要另外的license,就是所谓的Basic Function的IP,例如浮点运算、普通运算、三角函数、基本的存储器IP、配置功能IP、PLL、所有的桥以及所有的FPGA内部的硬核以及NIOS II(不含源码)等,这类IP在Quartus II中被调用后可以正常的生成仿真文件和可综合的文件,可成功的下载到FPGA中;另一类是收费的IP,需要购买单独的IP的license,例如各种以太网软IP、PCI-E软IP、CPRI、Interlaken、PCI、RapidIO和所有的几十个视频图像IP以及所有的DDR1/2/3/4软IP、256位AES硬件加密等,这类IP在Quartus II中被调用后生成的文件比较多,在Modelsim手动仿真中需要加入的库文件比较多,甚至有时候还缺少相应的库文件,导致仿真失败,最主要的是编译综合后生成的.sof文件是限时的文件,无法生成相应的.jic文件,因此无法下载到FPGA的Flash中。这里主要是针对第一篇博客中调用的RS编、解码的IP核给予说明,通过加载修改后的license文件,破解RS编、解码的IP核。

以Quartus II18.1版本(软件下载安装包在第一篇博客中的评论处已给出)为例,对相应的RS编解码的IP核进行破解。

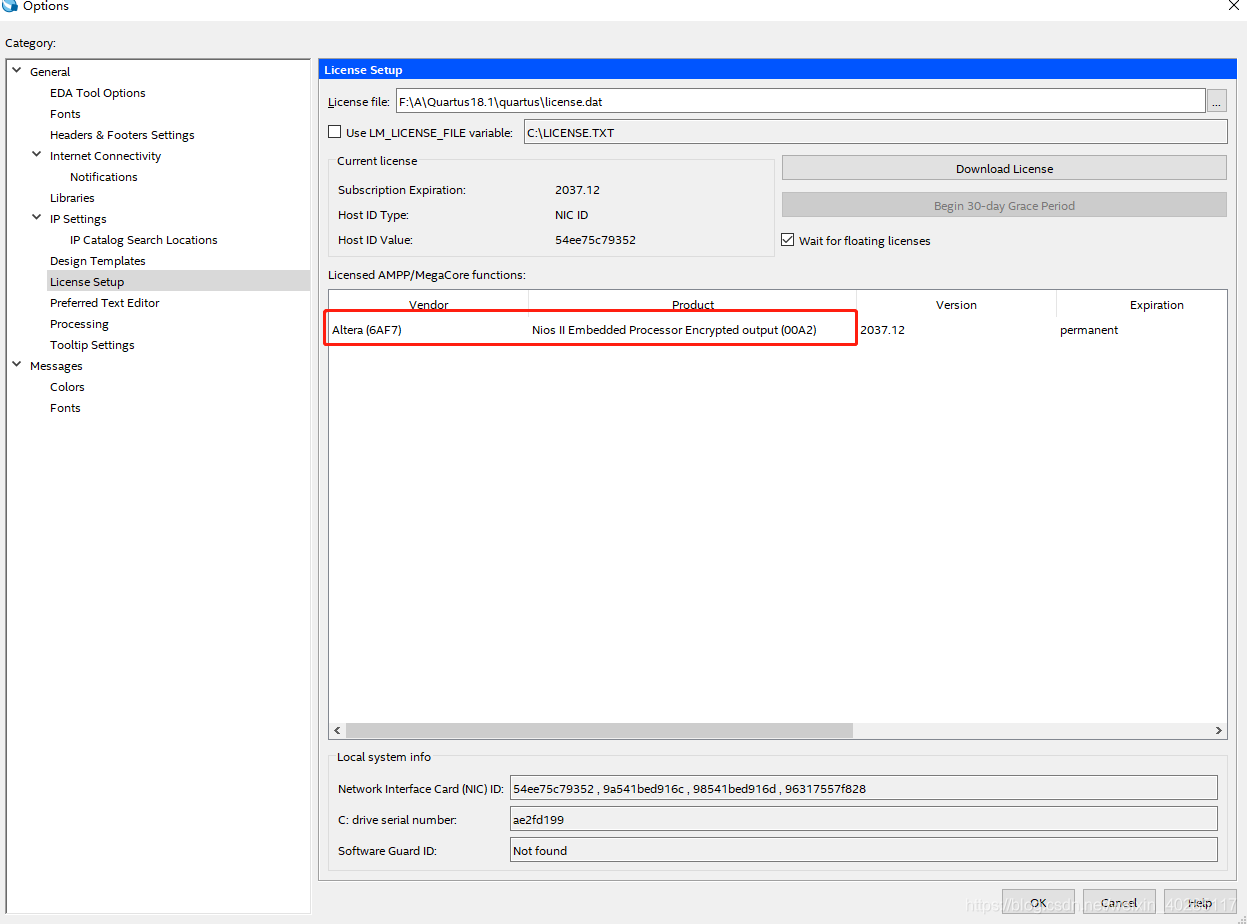

下图是正常Quartus II自身软件破解后的界面。

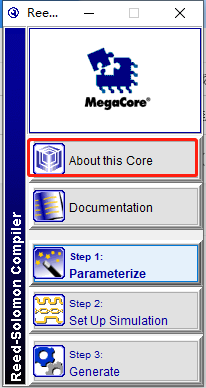

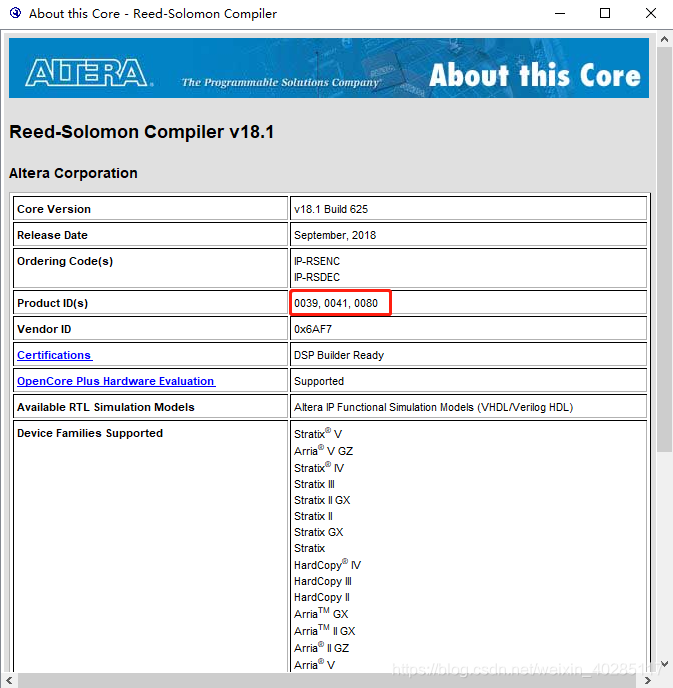

接下来,找到需要破解的RS编解码的IP核,点击第一项,关于这个核,可以看到该IP核的详细信息,如下图所示。

这里需要记住该IP核的ID号,可以看到,该IP核共有三个ID号,分别对应RS编码部分、RS编解码库文件、RS解码部分,将该ID号写入破解软件所对应的License文件,即可完成相应RS编解码部分IP核的破解。

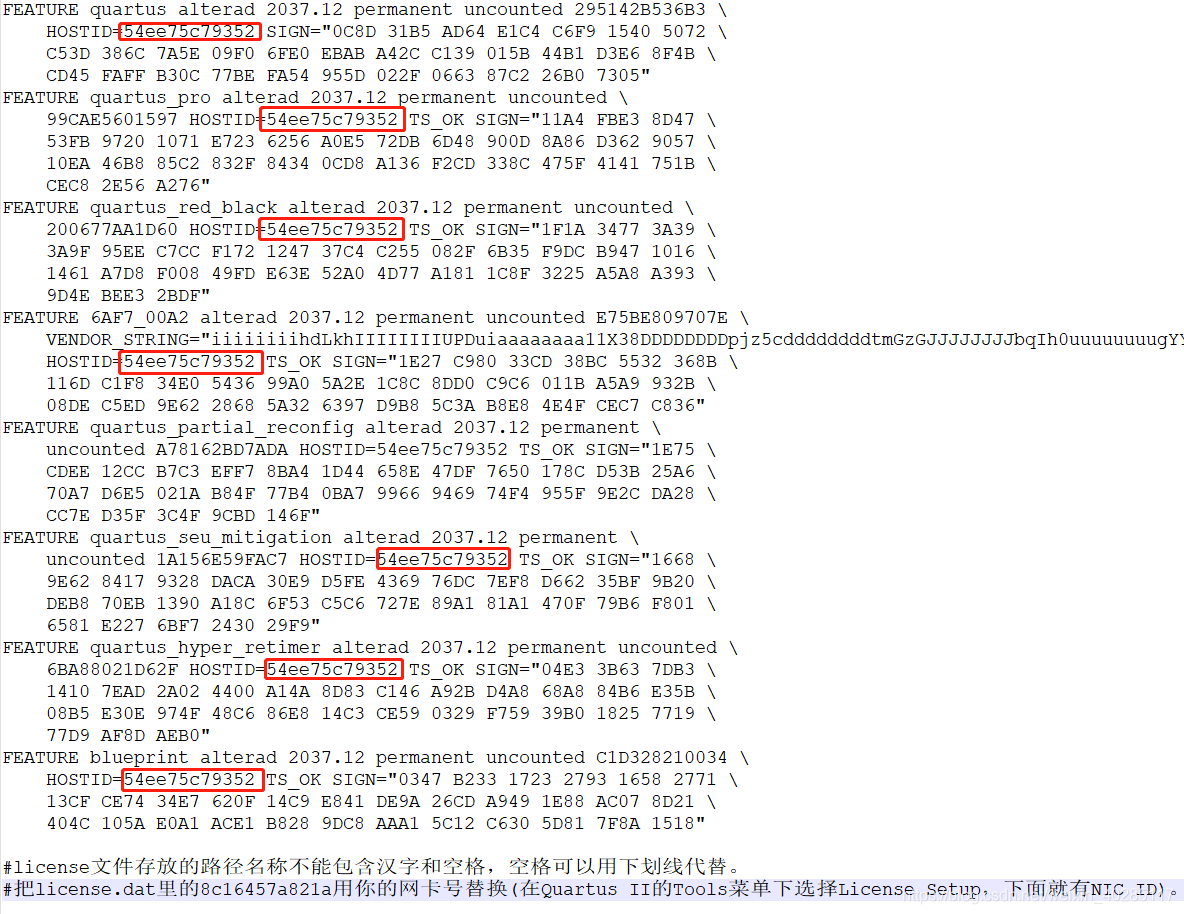

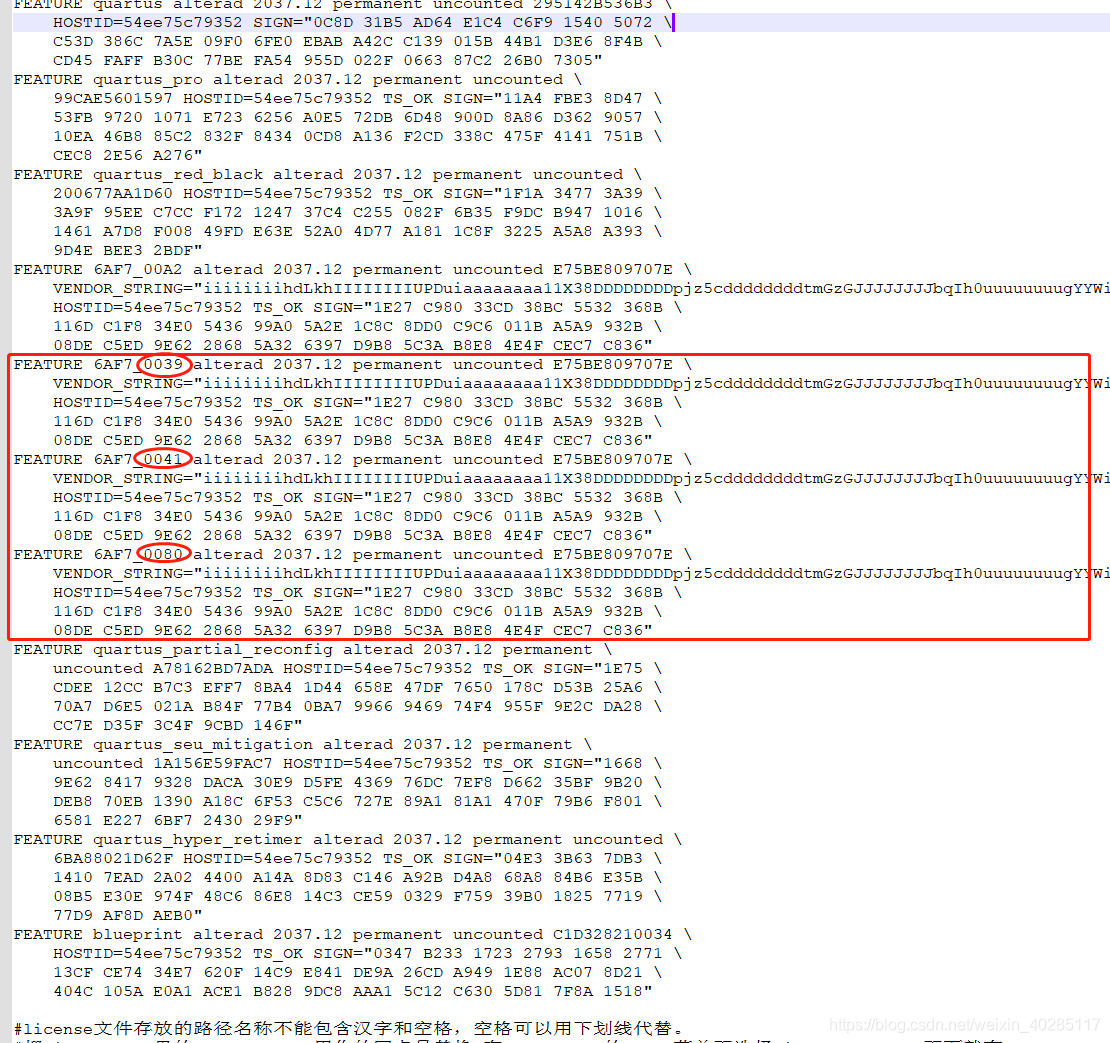

下边找到License,打开后如下图所示:

按照要求,已经将文件中的8c16457a821a更换成Quartus II软件的ID,下边需要做的操作是:在该文件的基础上再加上下边的三段代码,如红色方框区域中所示。细心的会发现该三段代码其实就是上一段代码的复制,只是改了其中红色椭圆中的序号,该序号正是RS编解码IP核对应的三个ID号。保存该文件,再将该License文件重新加载到Quartus II中License Setup中。

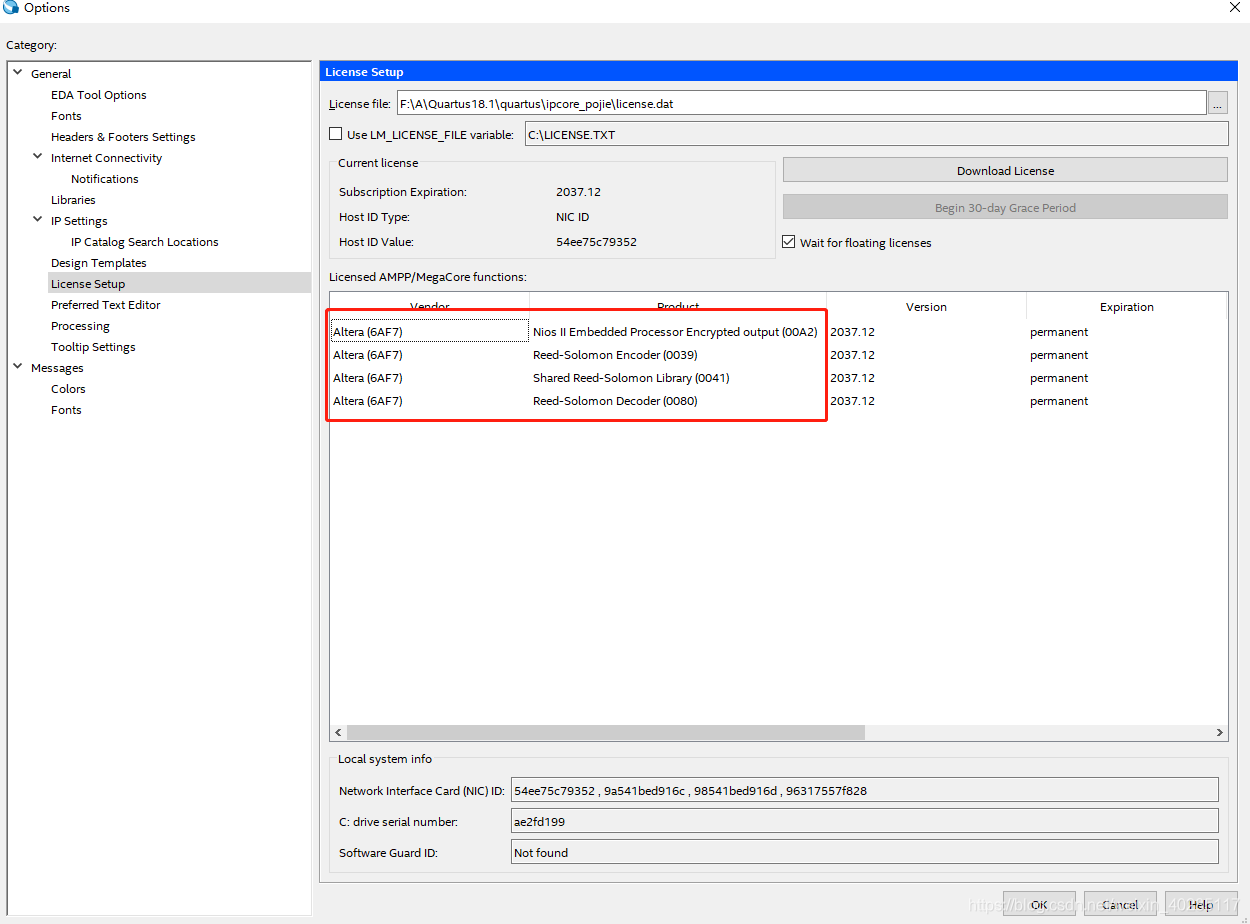

成功加载后如下图所示,可以发现该RS编解码部分的IP核已经被破解。

最后,RS编解码部分的IP核就可以正常使用了,编译综合后生成的.sof文件不再是限时文件,同时也可以生成.jic文件,可以下载到FPGA的外部Flash中。

总结

该破解方法可能还存在一些问题,由于能力有限,我并没有全部测试过,目前只是使用过RS编解码的IP核和FIR的IP核,对于一些更过于高端的IP核还没有接触过,因此并不能保证所有的IP核都适用。最后还是希望大家都支持正版软件,该破解方法仅限于学习使用。

初次创作,难免文章中存在错误,希望读者能够及时纠正并给予私信,望大家共同进步!

465

465

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?