提示:文章写后,目录可以自动生成,如何生成可参考右边的帮助文档

文章目录

目录

前言

Reed-Solomon码作为一种极具代表性的纠错码,凭借自身优异的性能,在这个信息时代一直闪烁着耀眼的光芒,广泛应用于信息传输与存储的相关领域。在线性分组码中,它的编码效率和纠错能力是最高的,特别是在短的中等码长下,性能接近香农限。本文是基于课题的要求,在Quartus II软件中通过调用IP核的方式实现RS编译码过程,并通过Modelsim进行仿真验证。

提示:以下是本篇文章正文内容,下面案例可供参考

一、RS码的相关理论知识

里德-所罗门码(RS码)是一种极具代表性的纠错码,是一种在有限域中完成理论构造的码,RS码中涉及的数据及数据间的运算都必须满足有限域的要求。有限域即伽罗华域,这里可以简单的理解成在伽罗华域中的加减运算就是异或运算(伽罗华域(Galois Field)上的四则运算_shelldon的专栏-CSDN博客_伽罗华域)。RS编码可以说是一种极其典型的信道编码,它是以码字为编码单位,其所有的码字取决于伽罗华域F(2^m),通常可以由m,n,k,三个参数表示,其中m表示每个码字需要的二进制位数,n表示码字长度,k表示信息码字长度,n-k为校验码字长度,可以纠正(n-k)/2的码字。eg:RS(15,7),它表示编码后的码字长度为15,信息码字长度为7,校验码字长度为8,可以纠正4个错误码字,每个码字的需要m=4个二进制比特位来表示。这里可以发现,m的值决定了编码后码字的最大长度,也就是说如果m = 5,那么编码后码字的最大长度为31。

二、设计流程

1.Quartus II 中调用IP核实现RS编码

1.1编码部分

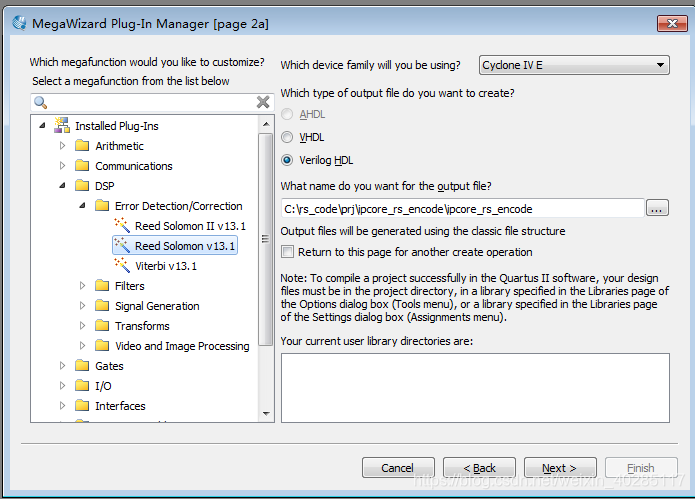

打开Quartus II软件,找到如下图所示的IP核

选择Next,等待IP核的生成

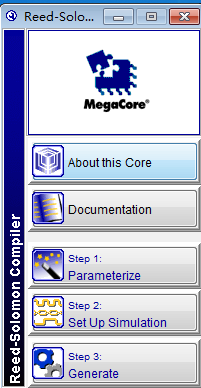

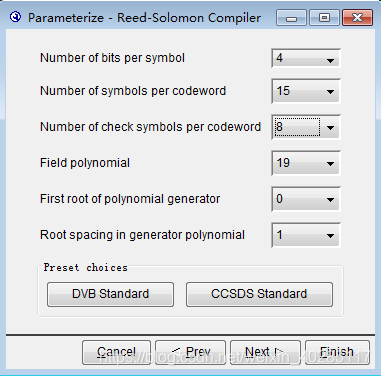

这是生成后的界面,点击Step 1:,进行编码参数的设置,如下图所示:

这里选择(15,7)编码,每个码字4个比特位(最多可以编15个码字),8个校验码字,剩下的多项式、生成多项式的第一根、生成多项式根的空间的值保持默认即可,点击Next,Finish。

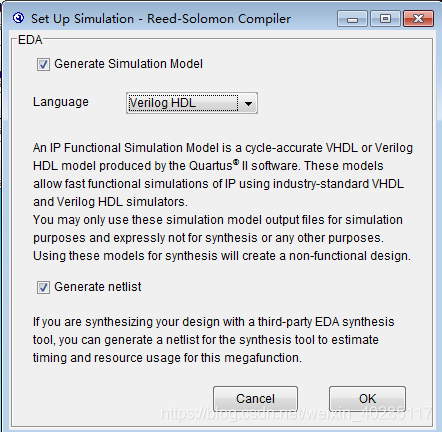

在Step 2:中选择生成仿真模型和仿真网表,点击OK

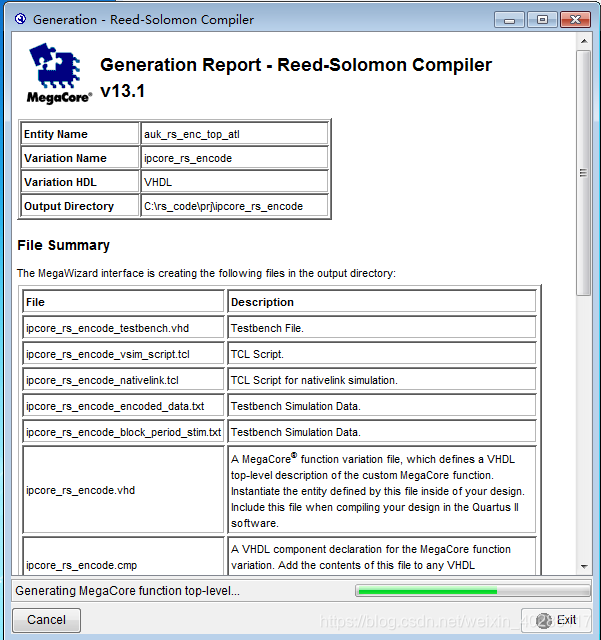

在Step 3:中生成编码IP核

注:在第三步生成IP核的过程中,由于软件存在Bug,可能会导致绿色进度条一直终不动,解决方法可以试图多次点击空白处,直至进度条跳动,或者选用更高版本的Quartus II软件(我曾安装过18.1版本的,不会出现上述问题,软件相应的安装包,我会附在评论处)生成完成后点击Exit,弹出页面是否将生成的IP核添加到工程中,点击yes。

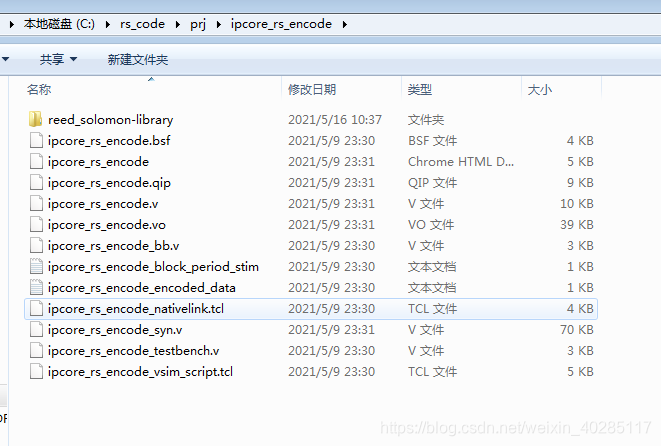

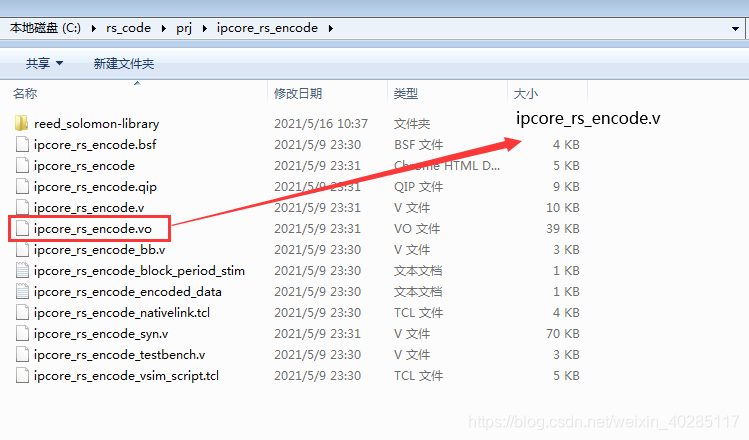

打开IP核保存的路径,生成的IP核文件如下图所示:

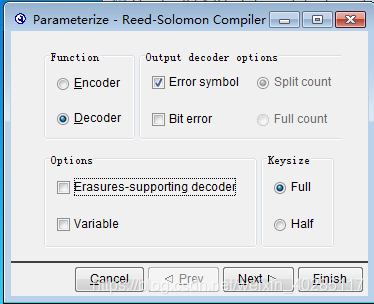

1.2解码部分

解码IP核的生成与上述编码过程基本类似,相同点不再赘述,其不同点在于Step 1:第一步选择Decoder,输出解码类型选择Error symbol

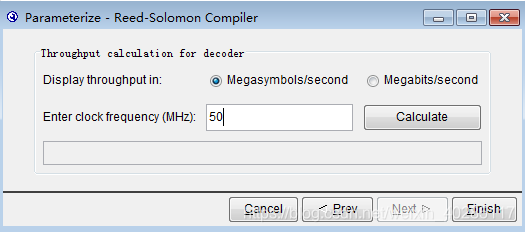

第三步,需要设置解码时钟,这里选择系统时钟50MHz

剩余操作与编码过程基本类似。

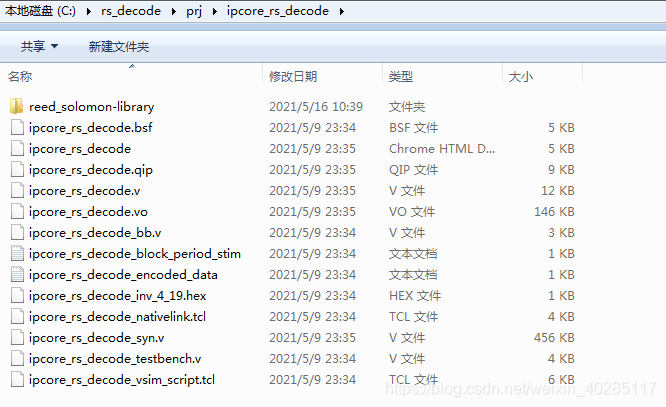

同样打开IP核的保存路径,生成的IP核文件如下图所示:

2.Modelsim仿真验证结果

2.1编码部分

在编码部分的IP核生成文件中,将ipcore_rs_encode.vo文件的后缀改成.v(由于该文件夹中已经有一个ipcore_rs_encode.v文件,因此,在更换后缀之前,可以将它先剪切到别的文件夹下)

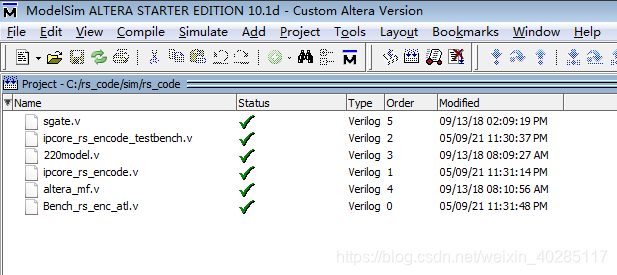

打开Modelsim,建立工程,在工程中添加以下几个文件Bench_rs_enc_atl.v、ipcore_rs_encode.v、ipcore_rs_enocde_testbench.v(这三个文件在生成的IP核文件夹下)、220model.v、alter_mf.v、sgate.v(这三个文件在Quartus II的安装目录下),注:将IP核文件夹下的两个.txt文本文件也复制到工程目录下。

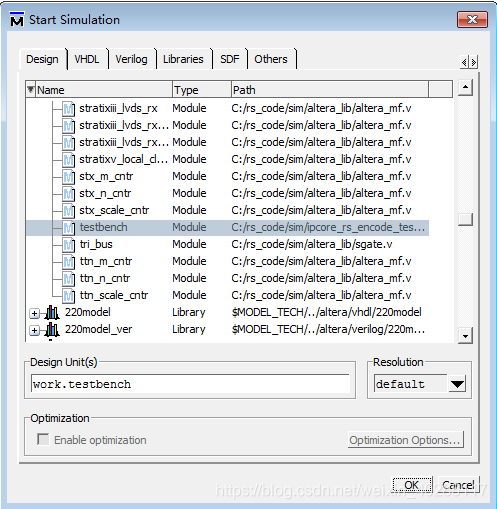

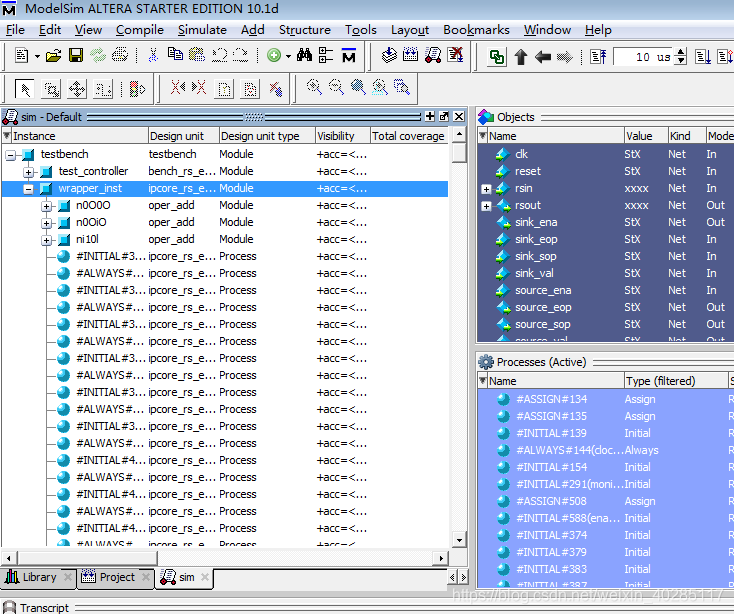

开始仿真,设置测试文件testbench

添加wrapper_inst模块下的信号到观察波形的窗口下,

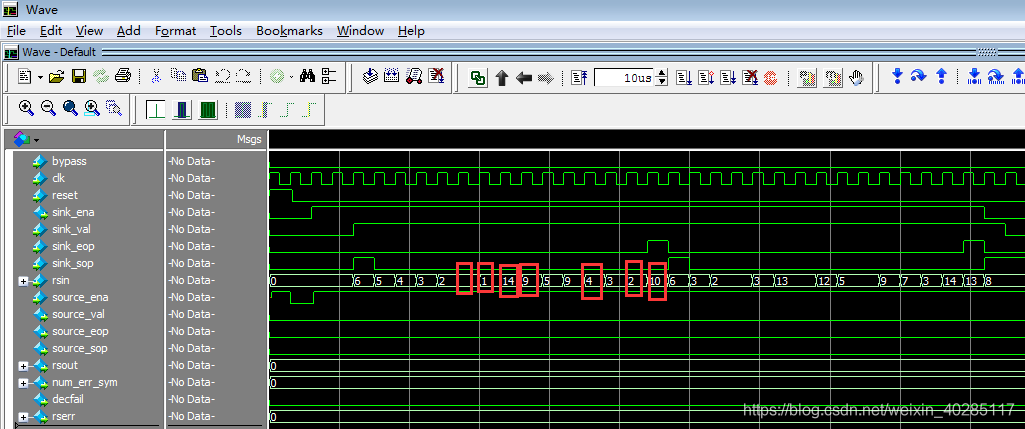

运行5us后,观察仿真结果:

结果分析:clk时钟,reset复位信号(高电平有效),sink_ena编码IP核反馈的信号,高电平表示待编码,sink_val输入编码数据使能信号,sink_sop编码输入开始信号,sink_eop编码输入结束信号,rsin输入的编码数据;source_ena编码IP核反馈信号,source_val输出编码数据使能信号,source_sop编码输出开始信号,sink_eop编码输出结束信号,rsin输出的编码后的数据。注:本次仿真过程用到的所有文件均是系统生成或自带的文件,并无自己编写的文件,如果想将该编码应用于实际,需要自己编写握手文件和测试文件,这里不予展示。

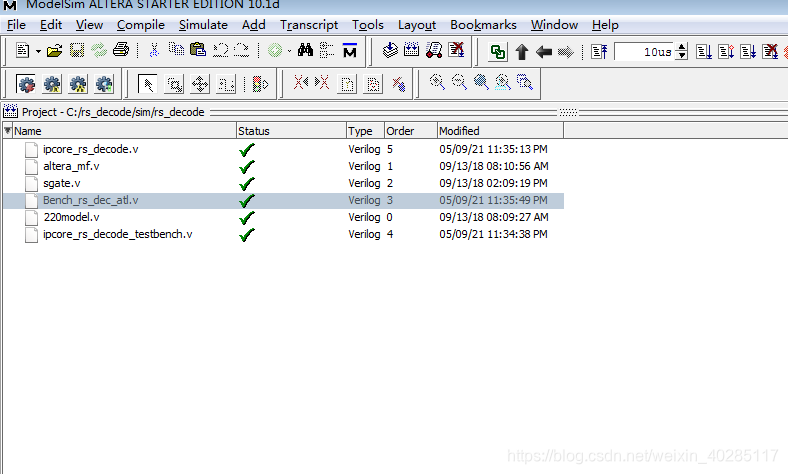

2.2解码部分

与编码类似,首先还是将解码IP核文件夹中的.vo文件改成.v文件,然后在Modelsim工程中加入上述编码过程所需要的文件。注:在解码IP核中复制两个.txt文本文件的同时,还需要复制ipcore_rs_decode_inv_4_19.hex文件到仿真的工程目录下,这个文件是关乎是否能够解码的关键。

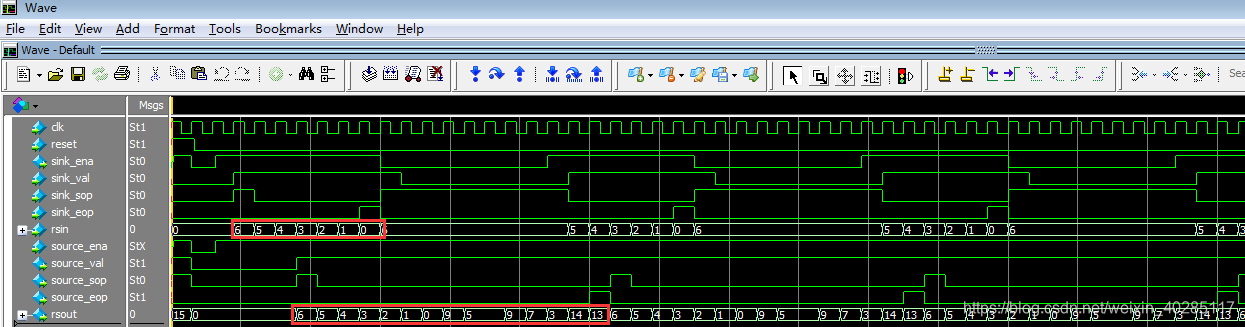

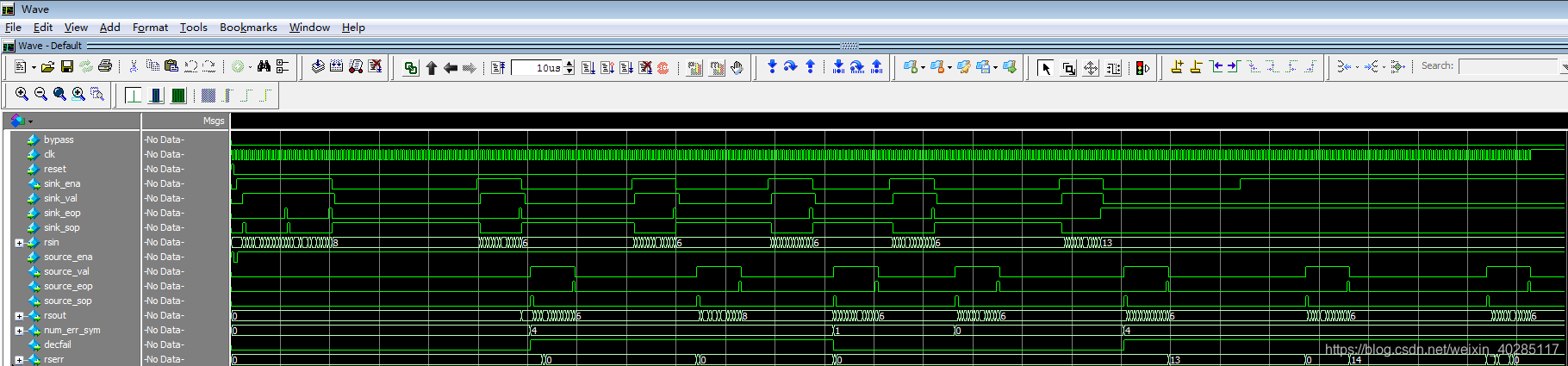

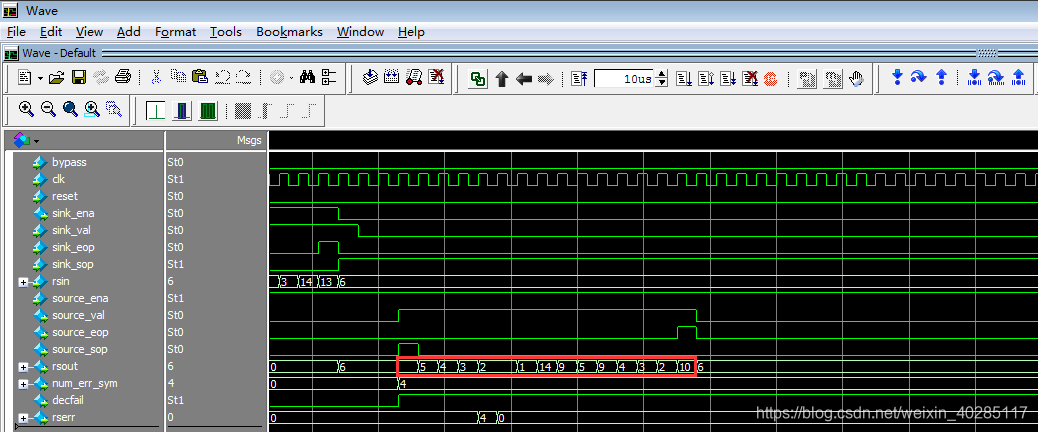

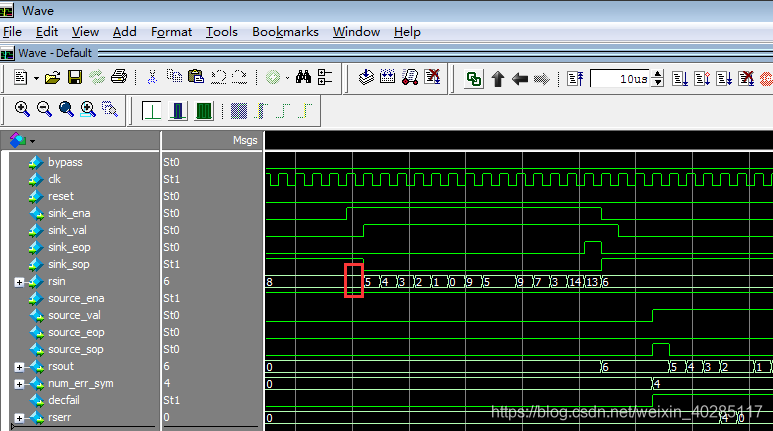

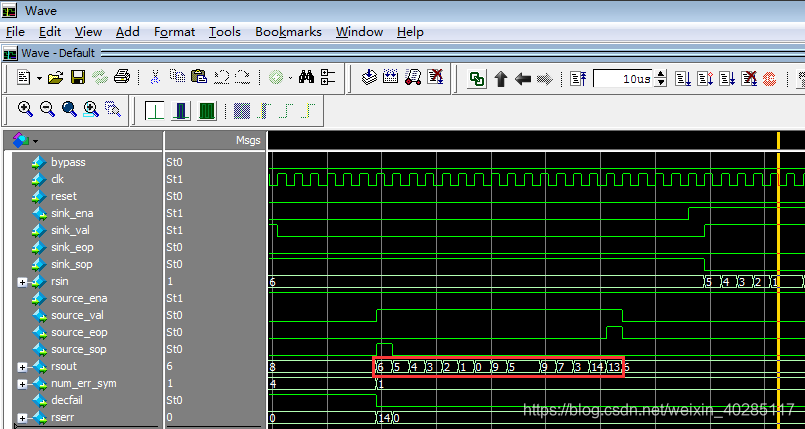

启动仿真,设置测试文件,添加信号,步骤和上述相同,这里不再赘述,运行10us,观察仿真结果:

解码过程中新增加了几个信号:bypass信号通道;num_err_sym一帧数据(15个码字)中错误码字的个数,由于(15,7)的编码纠错能力是4,因此它的最大数值是4;decfail解码失败,高电平有效,错误码字大于4个,则超出解码能力,不能进行纠错;rserr纠正码字的辅助码字

具体分析解码过程:

这是解码输入的第一帧数据6,5,4,3,2,2,1,14,9,5,9,4,3,2,10(正确的数据6,5,4,3,2,1,0,9,5,5,9,7,3,14,13)共出现7个错误码字,超出解码纠错的能力,因此输出端rsout的数据并未进行解码,decfail拉高,表示解码失败。

这是输入的第三帧数据8,5,4,3,2,1,0,9,5,5,9,7,3,14,13共出现1个错误码字,在输出端,num_err_sym=1,rserr=14(4‘b1110)和输入的码字8(4‘b1000)进行异或运算,得到6(4‘b0110),对第一个码字给予纠正,观察解码输出与正确的数据一致,证明该解码的正确性。

总结

好久之前就有写博客的想法,一直迟迟未动,这也许就是人的常病——懒惰、拖延。到今天终于完成了自己的第一篇博客,简单的谈一下自己的心得吧!我是一名电子信息专业的学生,从考研结束到现在接近一年的时间了,经历了好多,也思考了好多。也许是缘分让我误打误撞走上了学习FPGA的这条路,不能说适合,只能说努力就好。其实我个人认为本科以模电、数电出身的学子,根本没有必要非得去搞软件、算法,因为相应的一些基础专业课(数据结构、C++)大多涉及不深,当然这也纯属我个人的一些观点。其实对于FPGA(现场可编程门阵列)来说,我在本科阶段大三的时候就已经开始接触,只不过当时作为一门选修课而言,并没有引起重视,相应的只是混了个学分。步入研究生后我慢慢的了解到实验室的硬件研究方向大多都是基于FPGA和STM32做的一些项目,之后我才开始系统的学习相关的理论知识,其实对于Verilog语法而言,相对比较简单,稍微有点语法基础的人基本上两三天就可以完全整明白所有的语法。入门简单,其实我觉得真正应用起来,还是要下一定的苦功夫的,就我而言,这一年除了忙于上课和其他的事情,利用剩余时间,我也并没有学完整个系列的内容,后期还要继续努力。

之所以要写博客呢,就是想把自己学习过程中程序运行的结果、发现的问题、存在的不足记录下来和广大博友们一起讨论,和大家共同进步!未来的学习争取做到每个月写一篇博客!

本文主要是针对RS编、解码进行的,在Quartus II软件中通过调用IP核的方式实现RS编、解码以及通过Modelsim进行仿真的验证。Quartus II软件中的IP核分为两类,一类是免费的IP核,例如fifo、pll锁相环、Rom、Ram等,可以进行仿真以及生成可执行的文件(.sof、.jic),另一类是收费的IP核,FIR核、CIC核等,当然这些收费的IP核理论上来说是可以破解的,但具体的破解方法我还没有完全搞明白,相关破解方法可以在以后的文章里进行进一步讲解。本篇文章调用的编、解码IP核就是收费的IP核,但经过多次实验摸索,找到了上述的使用方法,也许该方法缺乏理论依据,相关内容仅供大家参考。

本文详细介绍了如何在QuartusII中利用IP核实现Reed-Solomon(RS)码的编码和解码过程,并通过Modelsim进行仿真验证。首先,阐述了RS码的基本理论,接着详细描述了在QuartusII中配置和生成编码及解码IP核的步骤,并提供了相关设置截图。最后,通过Modelsim进行编码和解码的仿真,展示了正确和错误码字的解码情况,验证了RS码的纠错能力。

本文详细介绍了如何在QuartusII中利用IP核实现Reed-Solomon(RS)码的编码和解码过程,并通过Modelsim进行仿真验证。首先,阐述了RS码的基本理论,接着详细描述了在QuartusII中配置和生成编码及解码IP核的步骤,并提供了相关设置截图。最后,通过Modelsim进行编码和解码的仿真,展示了正确和错误码字的解码情况,验证了RS码的纠错能力。

2580

2580

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?