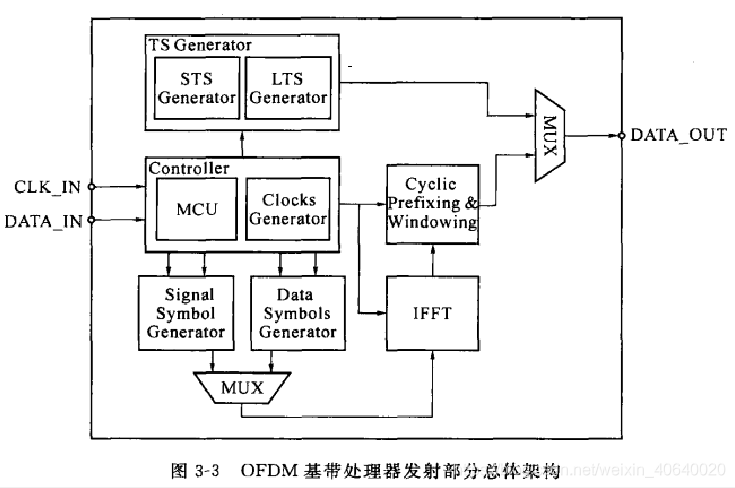

IEEE 802.11a基带处理器发射端总体架构:

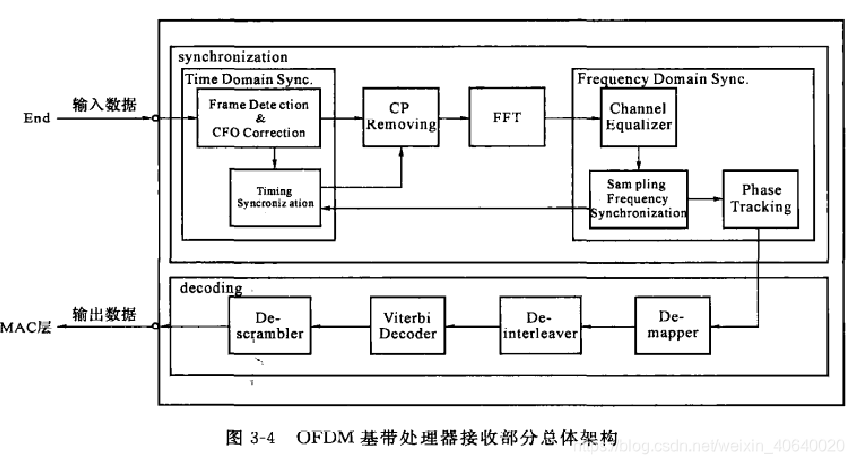

IEEE 802.11a基带处理器接收端总体架构:

IEEE 802.11a基带处理器接收端总体架构:

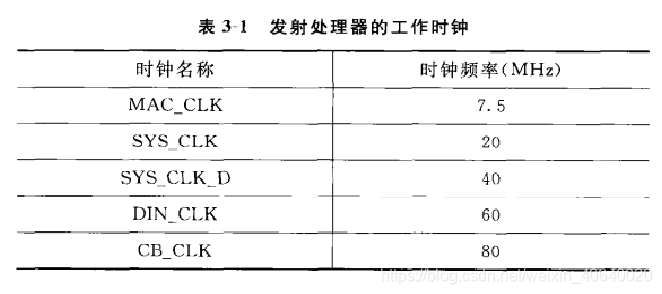

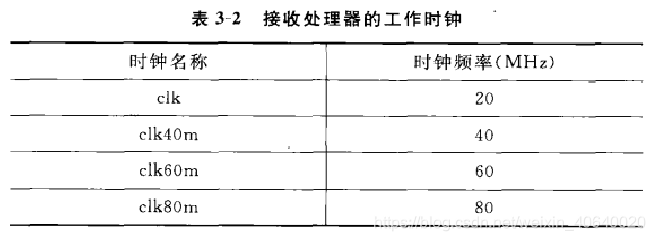

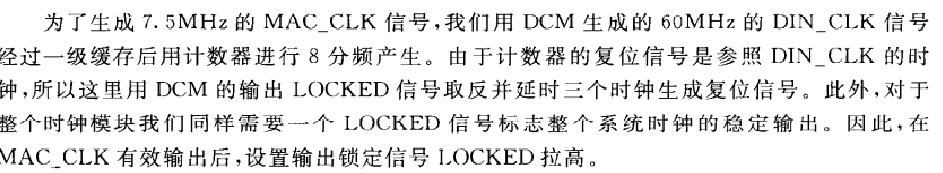

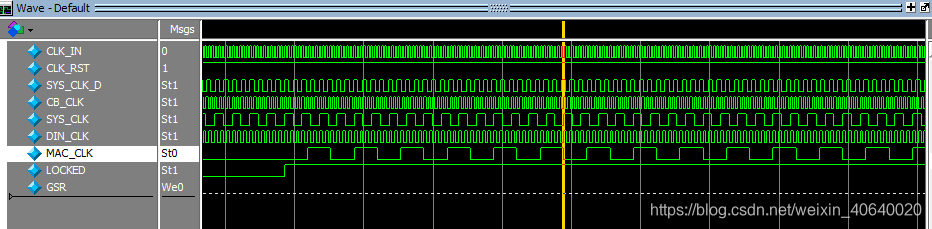

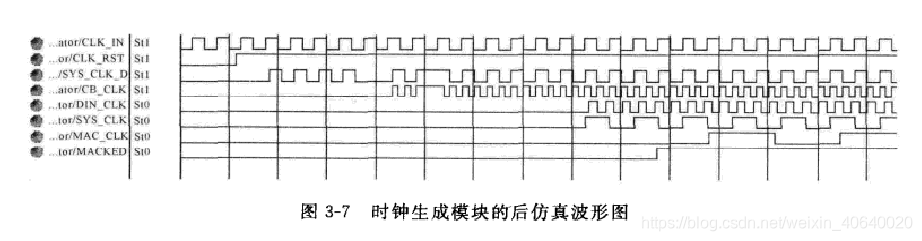

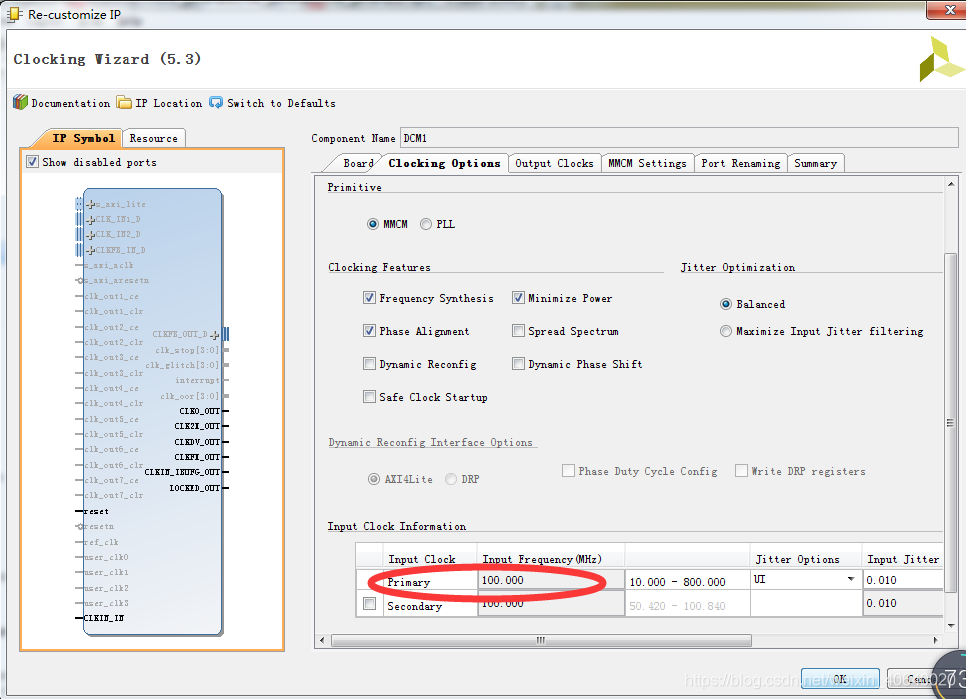

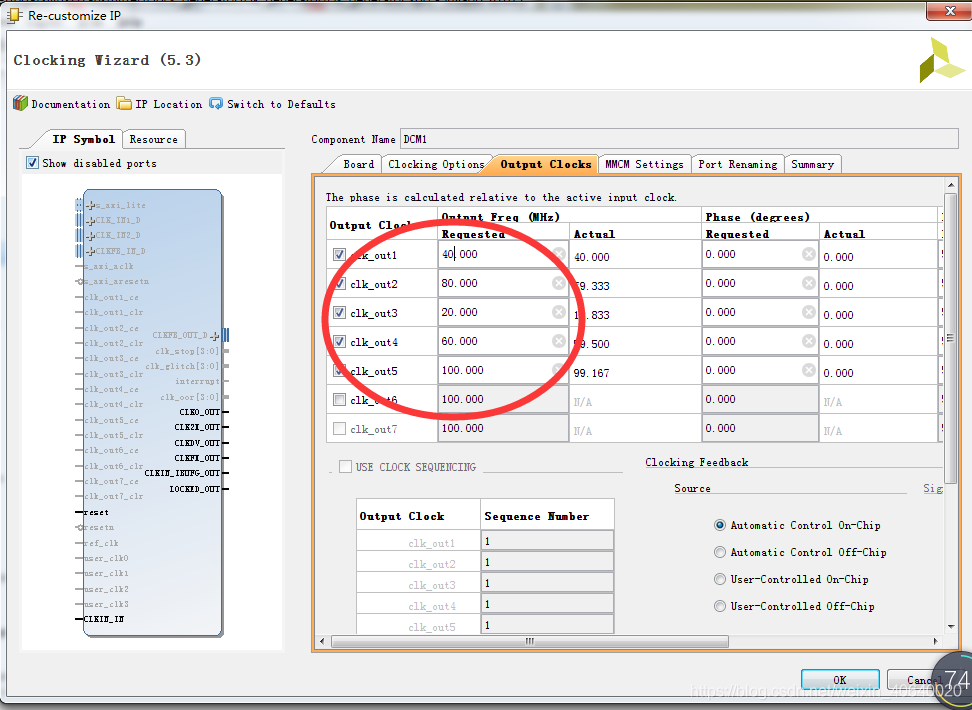

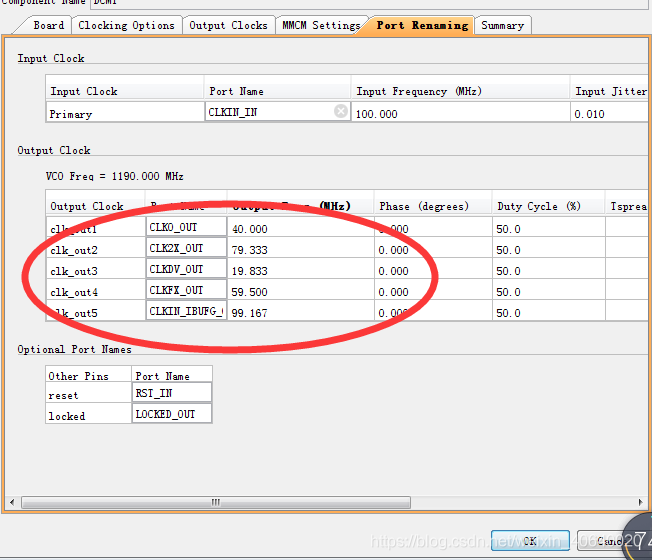

基带处理器的工作时钟:

![]()

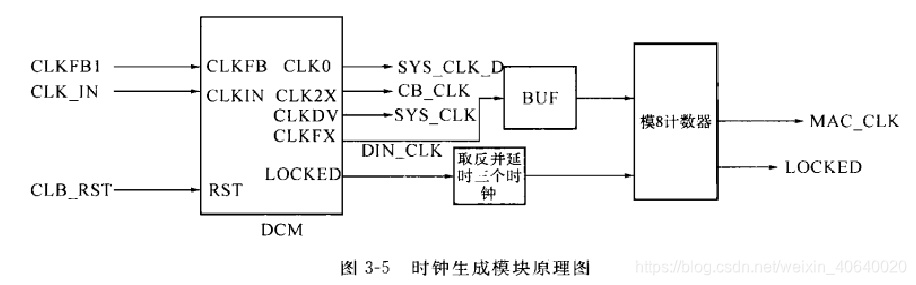

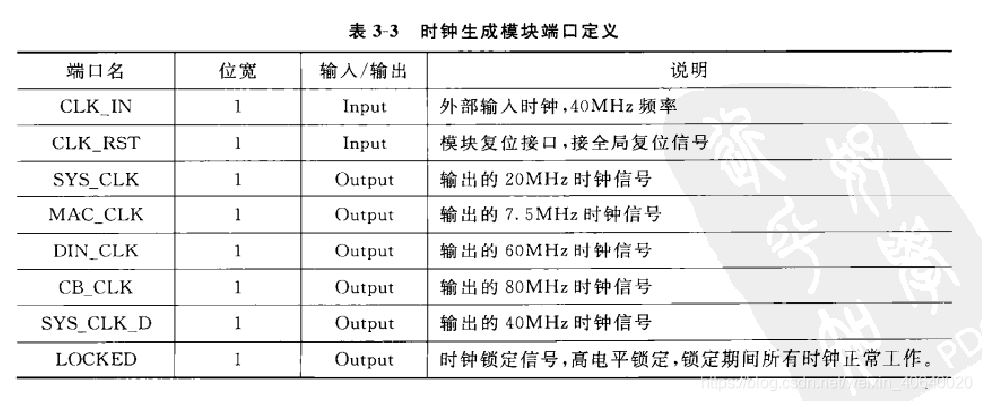

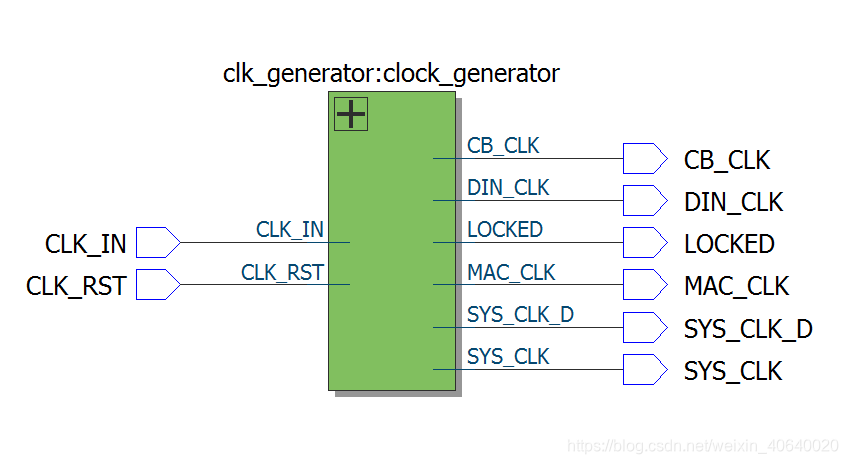

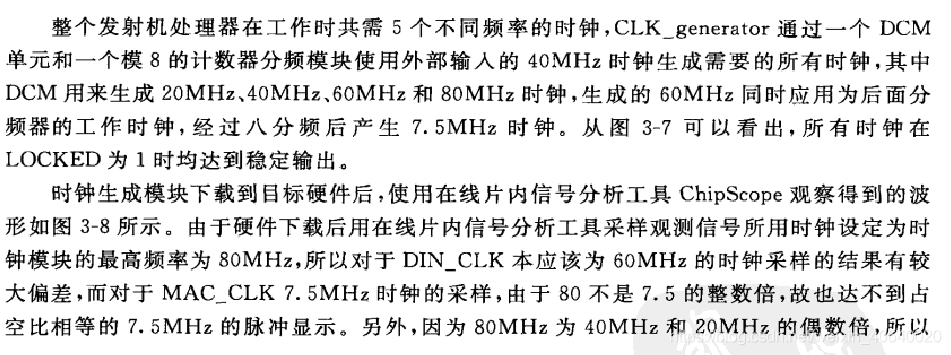

工作生成时钟模块的实现:

transmitter\clock_generator代码:

module clk_generator(CLK_IN,CLK_RST,SYS_CLK,MAC_CLK,DIN_CLK,CB_CLK,SYS_CLK_D,

LOCKED);

input CLK_IN;

input CLK_RST;

output SYS_CLK;

output MAC_CLK;

output DIN_CLK;

output CB_CLK;

output SYS_CLK_D;

output LOCKED;

wire RST; //RST is the core reset signal enabled with high level

wire LOCKED_OUT1; //Output of the DCM1 that activates after the DCM has achieved lock

wire SYS_CLK; //Clock divide output of the DCM1 by 2

wire CB_CLK; //Clock double output of the DCM1

wire DCM2_CLK; //Frequency synthesizer output to the DCM1 by 2/3

wire SYS_CLK_D; //The clock output same as input clock of DCM1

wire CLK_IN2; //Clock for generating MAC_CLK

reg LOCKED;

reg MAC_CLK; //Clock divide output of the DCM1 by 8

wire DIN_CLK;

reg lock_reg;

reg lock_reg1;

reg lock_reg2;

assign DCM2_CEN=~lock_reg2;

assign RST=~CLK_RST; //RST is the core reset signal enabled with high level.

wire RST2;

assign RST2=lock_reg2;

//Digital clock management block1 is used to generate clocks with the frequency

//of 20MHz, 40MHz, 80 MHz and 60MHz. The last one will be used as the clock to

//generator 7.5MHz.

wire clk_reg;

DCM1 U_DCM1 (

.RST_IN(RST),

.LOCKED_OUT(LOCKED_OUT1),

.CLKIN_IN(CLK_IN),

.CLKDV_OUT(SYS_CLK),

.CLK2X_OUT(CB_CLK),

.CLKFX_OUT(DCM2_CLK),

.CLK0_OUT(SYS_CLK_D),

.CLKIN_IBUFG_OUT(clk_reg)

);

BUFG DCM2_CLK_BUFG(

.I (DCM2_CLK),

.O (CLK_IN2)

);

BUFG CLK_BUFG(

.I (DCM2_CLK),

.O (DIN_CLK)

);

always @(posedge clk_reg or negedge CLK_RST) //delay lock_reg for 3 clock cycle

begin

if(!CLK_RST)

begin

lock_reg<=0;

lock_reg1<=0;

lock_reg2<=0;

end

else

begin

lock_reg<=LOCKED_OUT1;

lock_reg1<=lock_reg;

lock_reg2<=lock_reg1;

end

end

reg [3:0]count;

always @ (negedge RST2 or posedge CLK_IN2) // generater counter to devide the CLK_IN2 and generate LOCKED at appropriate time

begin

if(!RST2)

begin

count<=4'b0;

LOCKED<=1'b0;

end

else

if (count==4'b0111)

count<=4'b0;

else if(count==4'b0001)

begin

LOCKED<=1'b1;

count<=count+1;

end

else

count<=count+1;

begin

end

end

always @ (negedge RST2 or posedge CLK_IN2) //deviding CLK_IN2 by 8 to generate MAC_CLK

begin

if(!RST2)

MAC_CLK<=1'b0;

else

if (count<=4'b0011)

MAC_CLK<=1'b0;

else

MAC_CLK<=1'b1;

begin

end

end

endmodule

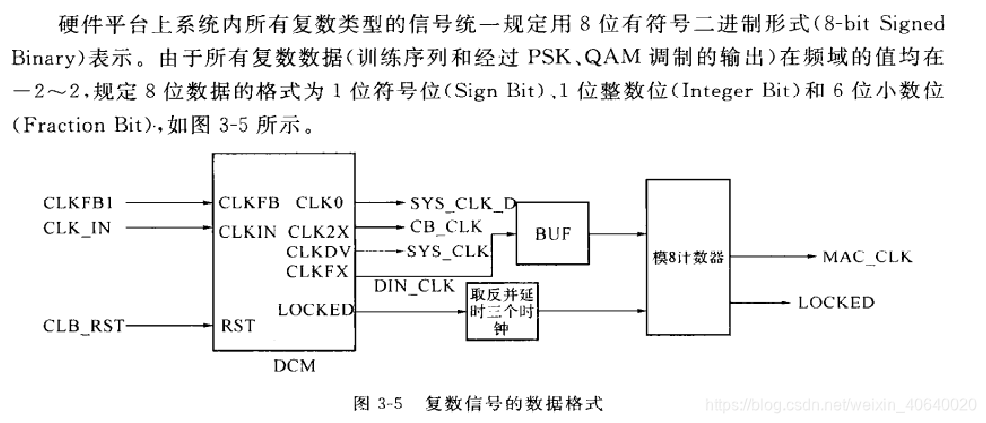

注意:调用vivado的MMCM模块

1、

2、

2、

3、

3、

4、

复位低有效

本文深入探讨了IEEE802.11a标准下基带处理器的时钟生成模块设计。通过详细的Verilog代码分析,展示了如何使用DCM和MMCM模块生成多种频率的时钟信号,包括20MHz、40MHz、80MHz和60MHz等,以及如何通过时钟分频得到MAC_CLK。此外,文章还介绍了锁相环的锁定机制和时钟分频器的具体实现。

本文深入探讨了IEEE802.11a标准下基带处理器的时钟生成模块设计。通过详细的Verilog代码分析,展示了如何使用DCM和MMCM模块生成多种频率的时钟信号,包括20MHz、40MHz、80MHz和60MHz等,以及如何通过时钟分频得到MAC_CLK。此外,文章还介绍了锁相环的锁定机制和时钟分频器的具体实现。

3483

3483

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?