导读

我在刚开始接触STM32/单片机的时候看到它的时钟系统/时钟树,都会感觉懵懵的,这是个啥?它想要告诉我哪方面的数据?特此一文记录一下学习心得。

时钟系统——MCU的脉搏,也可以理解为外设的开关,不打开它外设就没办法运行,每个外设都有其对应的时钟线(APBx、AHBx)。

MCU的资料文档一般都会有芯片的时钟系统框图👇

STM32F767IGT6时钟树

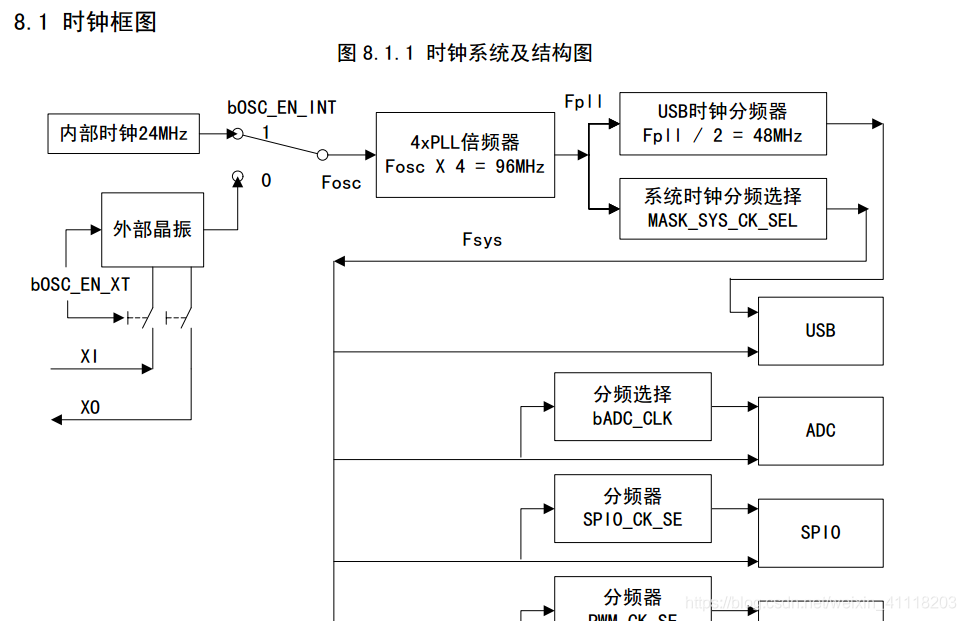

51单片机CH552G时钟框图

时钟系统的构成

- 时钟源

- 系统时钟

- 分/倍频器

- 外设

注意

这里要先区分一些时钟系统、系统时钟、时钟源的概念

时钟系统指的是这整个包含时钟源、系统时钟的系统

时钟源指的是产生一定频率的时钟

系统时钟指的是由时钟源驱动的一个时钟

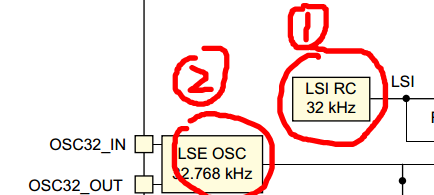

F767里面,总共有5个时钟源:

- LSI(内部低速时钟源)

- LSE(低速外部时钟源)

- HSI(高速内部时钟源)

- HSE(高速外部时钟源)

- PPL (锁相环)

记住:

L:低速时钟 H:高速时钟

I: 内部时钟 E:外部时钟

下面2张图是分别5个时钟源及其对应的频率

外部时钟一般由外部晶振产生,会相对比较准确一些。

而系统时钟则是由时钟源驱动产生的,具体由哪个时钟源驱动,则需要看时钟框图了。

STM32F767IGT6👇

可以看到,(系统时钟)SYSCLK有3路选择,HSI、HSL和PLLCLK均可以作为SYSCLK的时钟源,图中的梯形可以理解为一个选择器,3选1,同理时钟框图中的其他梯形也是同样的意思。

PLL在这篇文章里已经出现过2次了,它又是个啥?

它是由HSL或者HSI驱动产生的一个时钟,先经过分频器M,再经过倍频器N,再经过分频器P出来,形成PLL时钟源,供给外设或者系统时钟使用的。

PLL计算公式 : x=f / m * n / p

x为PLL频率,f为输入时钟源(HSL、HSI)时钟频率,m、p为分频器,n为倍频器

由这个图可以看出,SYSCLK出来后经过分频器,分配给AHB、APB或者其他时钟线,那么挂在这些时钟线上面的外设想要使用,就必须先使能相对应的时钟。

总结

所以我们在拿到一款新的芯片时,查看它的时钟框图,可以获取这些信息:

- 时钟系统有哪几个时钟源,频率分别为多少

- 系统时钟SYSCLK可以由哪几个时钟源驱动

- 哪些外设分别挂在哪个时钟线或者时钟源上

6684

6684

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?