1、scan chain是什么

扫描链(Scan chain)是可测试性设计的一种实现技术。它通过植入移位寄存器,使得测试人员可以从外部控制和观测电路内部触发器的信号值。

Scan Chain(扫描链测试)作为数字集成电路测试的重要方法之一,可以有效的筛选出坏片,提高产品质量。不同意常规性的从测试,scan test测试触角伸入到芯片的任何角落,测试目标为电路中的标准单元,包括组合及时序逻辑。

扫描链插入

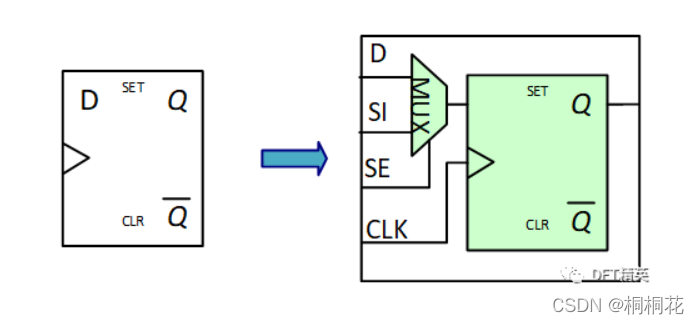

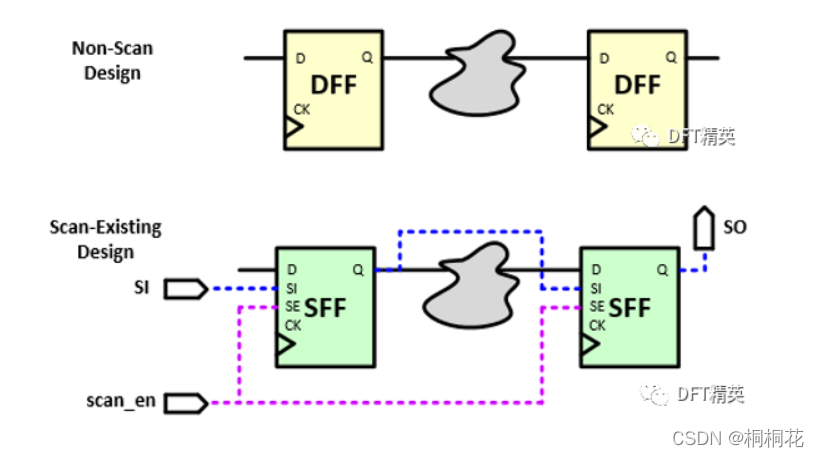

在芯片功能设计完成后,整个网表是由一堆普通的寄存器和组合逻辑构成的。扫描链的插入就是指将普通寄存器替换成为扫描寄存器(scan flip-flop)的过程。

SE scan enable为其切换信号。

正常工作模式时,SE为0,这时scan FF的功能与原有的D-FF完全一致,data path 为D到Q。芯片的功能得以保持不变。

当SE被切换为1时,这时候scan FF执行其scan属性,data path为SI到Q。SI即为测试时的数据流向入口。

SE=0 datapath:D->Q scan FF act as DFF

SE=1 datapath: SI->Q Scan FF act as Scan

将片上的扫描寄存器Q-SI连接起来,就成为了扫描链。

通过shift的方式可以由scan chain将数据串行输入的每个寄存器的SI端,达到控制每个寄存器的目的。在capture模式下,将芯片组合逻辑的反馈传回寄存器,达到对芯片内部观测的作用。

2、Scan Chain Reordering

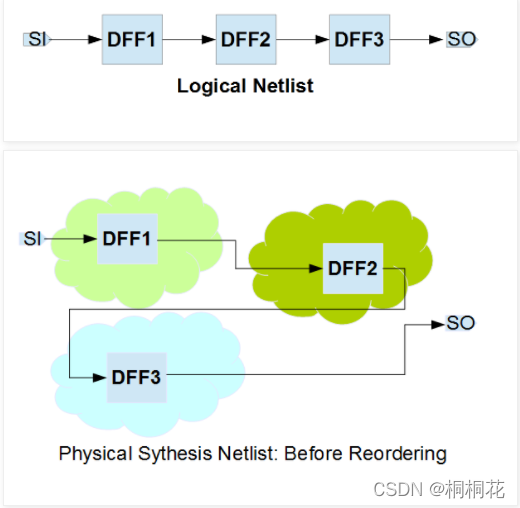

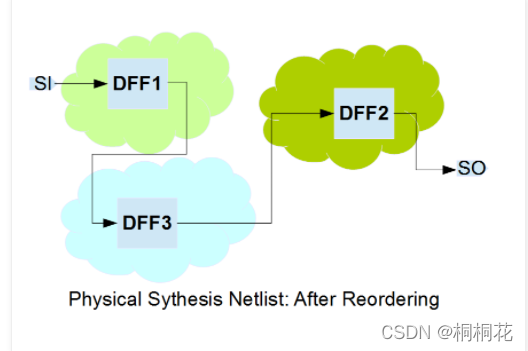

这是在设计中重新连接扫描链的过程,通过重新排序扫描连接来优化布线,从而改善时序和拥塞。

由于逻辑综合任意连接扫描链,我们需要在布局后执行扫描重新排序(scan reorder ),以使扫描链布线最优。

基于时序和拥塞。该工具以最佳方式放置标准单元。 这样做时,如果扫描链被分离,它可能会破坏链排序(这是由 Synopsys 的 DFT 编译器等扫描插入工具完成的),并且可以重新排序以优化它并保持链中的触发器数量。

物理网表根据布局重新排序。在示例设计中,重新排序的扫描链需要更少的布线资源。

Congestion Effect:

在 placement期间,优化可能会使扫描链由于拥塞而难以布线。 因此,该工具将重新排序链以减少拥塞。

Timing Effect:

这有时会增加链中的hold time问题。 为了克服这些 buffers,可能必须将其插入扫描路径。 它可能无法准确地保持扫描链长度。 它不能交换来自不同时钟域的单元。

因为之前生成的扫描链重新排序模式是没有用的。 但这不是问题,因为 ATPG 可以通过读取新的网表来重做。

参考:

https://www.sohu.com/a/330331191_778637

https://vlsibasic.blogspot.com/2014/09/scan-chain-reordering.html

3038

3038

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?